Supplementation

Field Effect Transistors

DC Biasing

FET Amplifiers

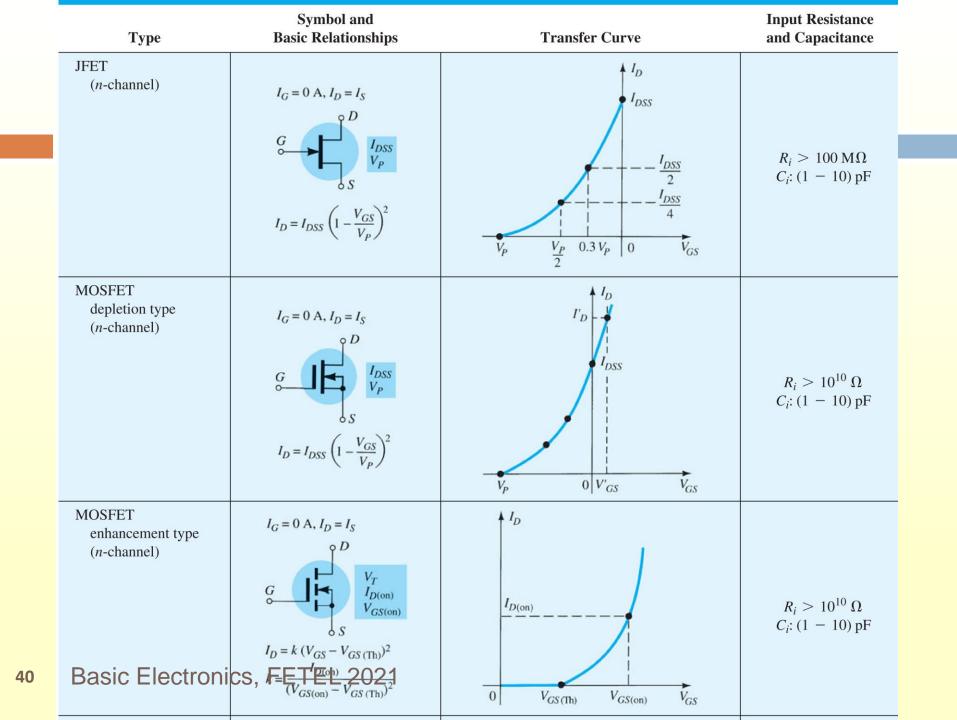

## Field Effect Transistors

#### What is FET?

In FET, a weak electrical signal coming through one electrode creates an electric field which controls the current flowing.

| FET                                                       |                                                                                                                                                              | BJT |                                                                                                                                                                |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| because its oper<br>flow of majority                      | lar semiconductor device<br>ration depends upon the<br>carriers <i>i.e.</i> , either holes<br>the case may be.                                               | 1.  | BJT is a bipolar semiconductor device<br>because the current constituting elements<br>are both majority carriers as well as<br>minority carriers in this case. |  |

| more larger (ran<br>BJT. The reasor<br>input terminal i.  | dance of FET is much<br>ging in Megaohms) than<br>a behind this is that the<br><i>e.</i> , gate to source of FET<br>d and reverse bias offers<br>resistance. | 2.  | The input impedance of BJT is very less<br>in comparison to FET.                                                                                               |  |

| 3. FET is a voltage                                       | e controlled device.                                                                                                                                         | 3.  | BJT is a current controlled device.                                                                                                                            |  |

| <ol> <li>FET is less nois<br/>junctions.</li> </ol>       | y. Because there are no                                                                                                                                      | 4.  | Much noisy than FET.                                                                                                                                           |  |

| 5. Higher frequence                                       | y response.                                                                                                                                                  | 5.  | Frequency variation affects the performance.                                                                                                                   |  |

| <ol><li>Good thermal<br/>absence of mine</li></ol>        | stability because of ority carriers.                                                                                                                         | 6.  | Temperature dependent, thermal runaway may cause.                                                                                                              |  |

| 7. Costlier than B                                        | JT.                                                                                                                                                          | 7.  | Relatively cheaper.                                                                                                                                            |  |

| 8. Small sized.                                           |                                                                                                                                                              | 8.  | Comparatively bigger.                                                                                                                                          |  |

| output quantiti<br>square term in                         | ship between input and<br>es is nonlinear due to<br>shockley's equations                                                                                     | 9.  | The BJT is an almost linear device or we<br>can say that BJT works linearly in active<br>region as an amplifier.                                               |  |

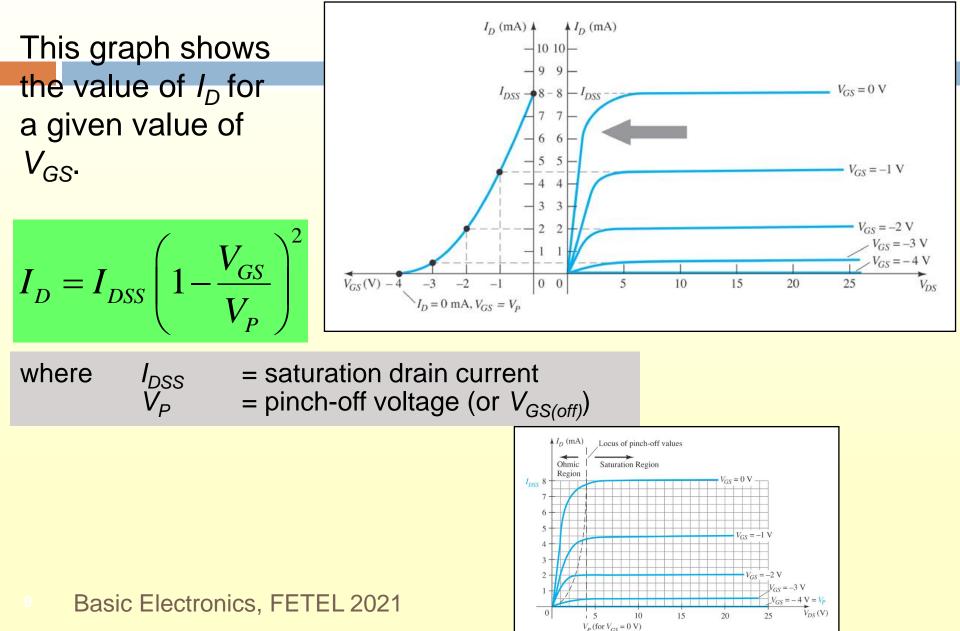

| $I_D = I_{DSS} \left( 1 - \frac{V_0}{V} \right)$          | $\left(\frac{3S}{P}\right)$                                                                                                                                  |     |                                                                                                                                                                |  |

| <ol> <li>No offset voltage<br/>switch or chopp</li> </ol> | ; so it works better as a<br>per.                                                                                                                            | 10. | There is always an offset voltage before switching.                                                                                                            |  |

| 1. Small gain band                                        | lwith product.                                                                                                                                               | 11. | Greater than FET.                                                                                                                                              |  |

FET are smaller and more temperature stable than BJT and suited for IC applications.

# FETs vs. BJTs

#### Similarities: Amplifiers Switching devices Impedance matching circuits

**Differences:** FETs are voltage controlled devices. BJTs are current controlled devices.

FETs have higher input impedance. BJTs have higher gain.

FETs are less sensitive to temperature variations and are better suited for integrated circuits

FETs are generally more static sensitive than BJTs.

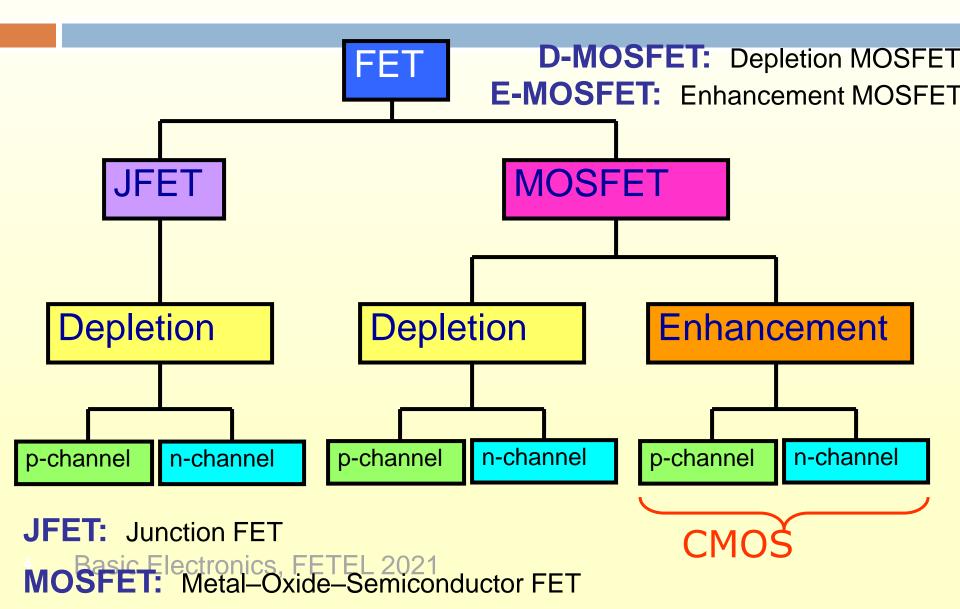

# **FET Family**

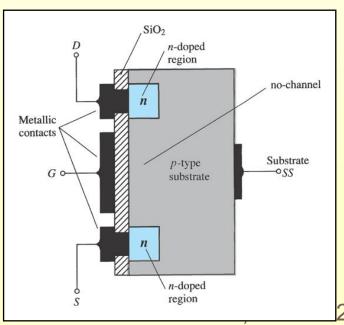

## JFET construction.

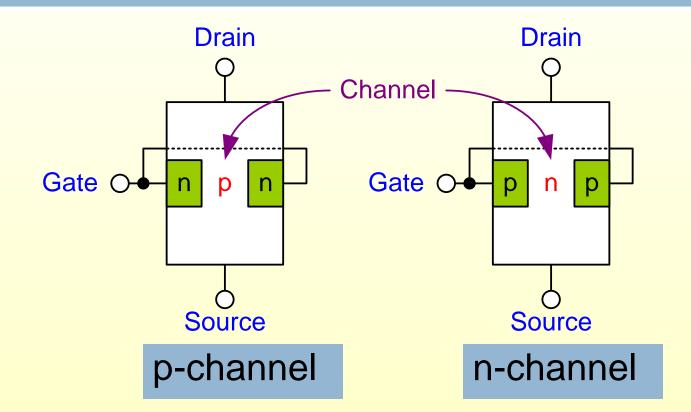

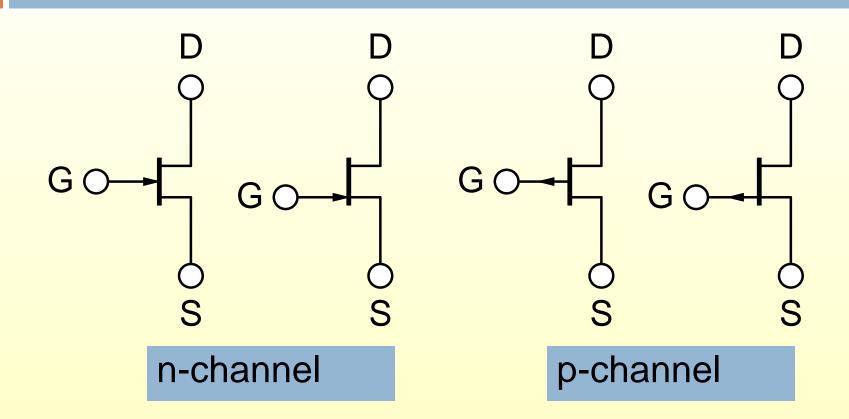

## JFET schematic symbols.

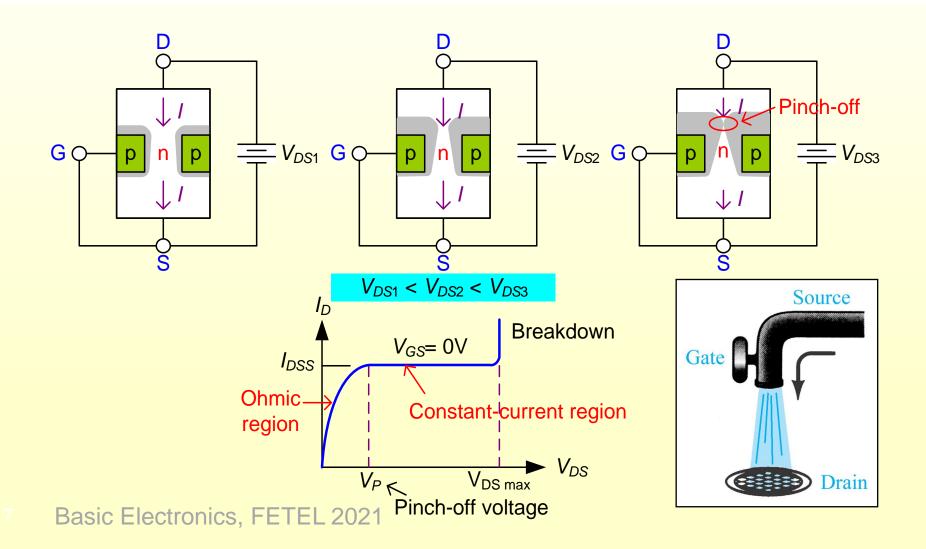

## Summary: Varying $V_{DS}$ with $V_{GS} = 0V$

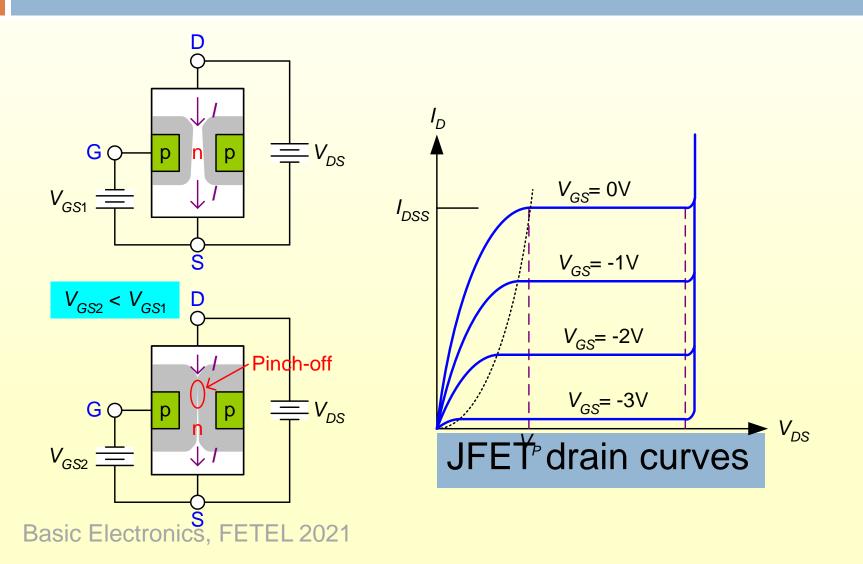

# Summary: Varying V<sub>GS</sub>

# JFET Transfer Curve

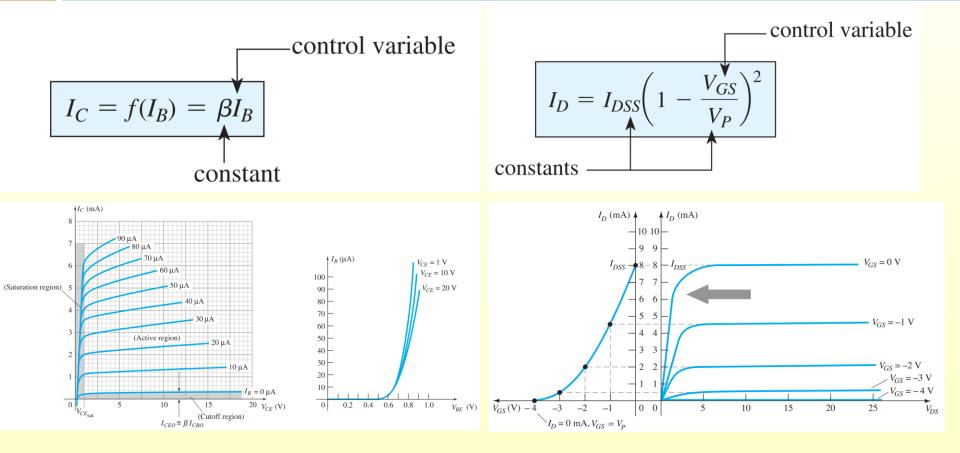

# **BJT vs. JFET**

## JFET Specification Sheet

#### **N-Channel General Purpose Amplifier**

This device is a low level audio amplifier and switching transistors, and can be used for analog switching applications. Sourced from Process 55.

#### Absolute Maximum Ratings\* TA = 25°C unles

| igs* ⊤ | A = 25°C unless otherwise noted |  |

|--------|---------------------------------|--|

|--------|---------------------------------|--|

| Symbol                            | Parameter                                        | Value       | Units |

|-----------------------------------|--------------------------------------------------|-------------|-------|

| V <sub>DG</sub>                   | Drain-Gate Voltage                               | 25          | V     |

| V <sub>GS</sub>                   | Gate-Source Voltage                              | - 25        | V     |

| I <sub>GF</sub>                   | Forward Gate Current                             | 10          | mA    |

| T <sub>J</sub> , T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150 | °C    |

#### 11 Basic Electronics, FETEL 2021

| Electr                         | cal Characteristics TA =                                                                                         | 25°C unless otherwise noted                                                                                                                                                                                      |                            |                   |                                         |                                      |

|--------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------------------------------|--------------------------------------|

| Symbol                         | Parameter                                                                                                        | Test Conditions                                                                                                                                                                                                  | Min                        | Тур               | Max                                     | Un                                   |

| OFF CHAI                       | RACTERISTICS                                                                                                     |                                                                                                                                                                                                                  |                            |                   |                                         |                                      |

| V <sub>(BR)GSS</sub>           | Gate-Source Breakdown Voltage                                                                                    | I <sub>G</sub> = 10 μA, V <sub>DS</sub> = 0                                                                                                                                                                      | - 25                       |                   |                                         |                                      |

| I <sub>GSS</sub>               | Gate Reverse Current                                                                                             | V <sub>GS</sub> = -15 V, V <sub>DS</sub> = 0                                                                                                                                                                     |                            |                   | - 1.0<br>- 200                          |                                      |

| $V_{\text{GS(off)}}$           | Gate-Source Cutoff Voltage                                                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                            | - 0.5<br>- 1.0<br>- 2.0    |                   | - 200<br>- 6.0<br>- 7.0<br>- 8.0        |                                      |

| V <sub>GS</sub>                | Gate-Source Voltage                                                                                              | $ \begin{array}{ll} V_{DS} = 15 \ V, \ I_D = 100 \ \mu A & {\color{red} 5457} \\ V_{DS} = 15 \ V, \ I_D = 200 \ \mu A & {\color{red} 5458} \end{array} $                                                         |                            | - 2.5<br>- 3.5    | 0.0                                     |                                      |

|                                |                                                                                                                  | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 400 μA 5459                                                                                                                                                             |                            | - 4.5             |                                         | <u> </u>                             |

| ON CHAR                        | ACTERISTICS                                                                                                      | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 400 μA <b>5459</b>                                                                                                                                                      |                            | - 4.5             |                                         |                                      |

| ON CHAR                        | ACTERISTICS Zero-Gate Voltage Drain Current*                                                                     | $V_{DS} = 15 \text{ V},  \text{I}_{D} = 400 \ \mu\text{A} \qquad \textbf{5459}$ $V_{DS} = 15 \text{ V},  \text{V}_{GS} = 0 \qquad \textbf{5457}$ $\textbf{5458}$ $\textbf{5459}$                                 | 1.0<br>2.0<br>4.0          | 3.0<br>6.0<br>9.0 | 5.0<br>9.0<br>16                        | m                                    |

| I <sub>DSS</sub>               | Zero-Gate Voltage Drain Current*                                                                                 | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 5457<br>5458<br>5459                                                                                                                                                 | 2.0                        | 3.0<br>6.0        | 9.0                                     | m                                    |

| I <sub>DSS</sub>               | Zero-Gate Voltage Drain Current*                                                                                 | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 5457<br>5458                                                                                                                                                         | 2.0                        | 3.0<br>6.0        | 9.0                                     | m<br>m<br>m                          |

| IDSS<br>SMALL SI               | Zero-Gate Voltage Drain Current*                                                                                 | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 5457<br>5458<br>5459<br>V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0, f = 1.0 kHz<br>5457<br>5458                                                                     | 2.0<br>4.0<br>1000<br>1500 | 3.0<br>6.0        | 9.0<br>16<br>5000<br>5500               | μmi<br>μmi                           |

| IDSS<br>SMALL SI<br>grs        | Zero-Gate Voltage Drain Current*<br>GNAL CHARACTERISTICS<br>Forward Transfer Conductance*                        | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 5457<br>5458<br>5459<br>V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0, f = 1.0 kHz<br>5457<br>5458<br>5459                                                             | 2.0<br>4.0<br>1000<br>1500 | 3.0<br>6.0<br>9.0 | 9.0<br>16<br>5000<br>5500<br>6000       | m<br>m<br>μml<br>μml<br>μml          |

| IDSS<br>SMALL SI<br>grs<br>gos | Zero-Gate Voltage Drain Current*<br>GNAL CHARACTERISTICS<br>Forward Transfer Conductance*<br>Output Conductance* | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0 5457<br>5458<br>5459<br>V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0, f = 1.0 kHz<br>5457<br>5458<br>5459<br>V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 0, f = 1.0 kHz | 2.0<br>4.0<br>1000<br>1500 | 3.0<br>6.0<br>9.0 | 9.0<br>16<br>5000<br>5500<br>6000<br>50 | mm<br>mm<br>μmt<br>μmt<br>μmt<br>μmt |

2N5457 / 5458 / 5459 / MMBF5457 / 5458 / 5459

# 2N5457 / 5458 / 5459 / MMBF5457 / 5458 / 5459

## Example

The partial datasheet for a 2N5459 JFET indicates that typically  $I_{DSS} = 9$  mA and  $V_{GS(off)} = -8$  V (maximum). Using these values, determine the drain current for VGS = 0 V, -1 V, and -4 V.

For  $V_{\rm GS} = 0$  V,

$$I_{\rm D} = I_{\rm DSS} = 9 \,\mathrm{mA}$$

For  $V_{\rm GS} = -1 \, \rm V$ ,

$$I_{\rm D} \approx I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS(off)}} \right)^2 = (9 \text{ mA}) \left( 1 - \frac{-1 \text{ V}}{-8 \text{ V}} \right)^2$$

$$= (9 \text{ mA})(1 - 0.125)^2 = (9 \text{ mA})(0.766) = 6.89 \text{ mA}$$

For

$$V_{\text{GS}} = -4 \text{ V}$$

,

$I_{\text{D}} \approx (9 \text{ mA}) \left(1 - \frac{-4 \text{ V}}{-8 \text{ V}}\right)^2 = (9 \text{ mA})(1 - 0.5)^2 = (9 \text{ mA})(0.25) = 2.25 \text{ mA}$

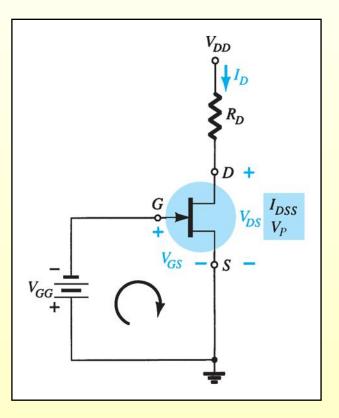

# **JFET Biasing Circuits**

- Gate bias (Fixed bias) circuit

- Self bias circuit

Dasic Electionics, retel 2021

Voltage-divider bias circuit

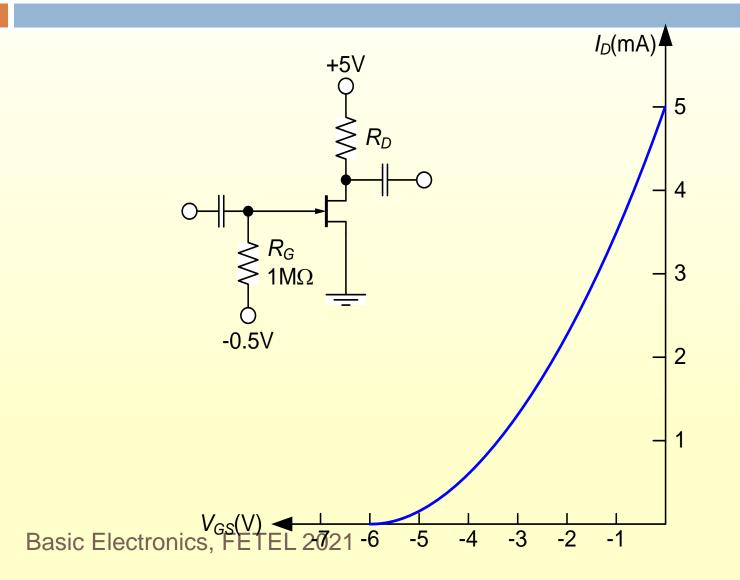

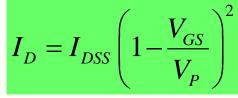

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right)^{2}$$

$$V_{GS} = ???? \rightarrow BIAS$$

$$V_{GS} \text{ must be negative for N-channel JFET}$$

$$I_{3} \text{ Basic Electronics, FETEL 2021}$$

$V_{GS}(V) \blacktriangleleft$

## Gate Bias (Fixed bias)

14

## Self bias circuit.

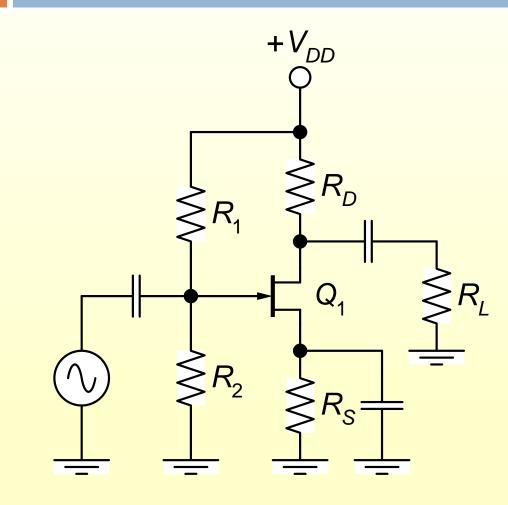

## Voltage-divider bias.

$$V_G = V_{DD} \frac{R_2}{R_1 + R_2}$$

$$I_D = \frac{V_S}{R_S} = \frac{V_G - V_{GS}}{R_S}$$

$$\therefore I_D \Big|_{V_{GS} = 0} = \frac{V_G}{R_S}$$

$$\therefore V_{GS} \Big|_{I_D = 0} = V_G$$

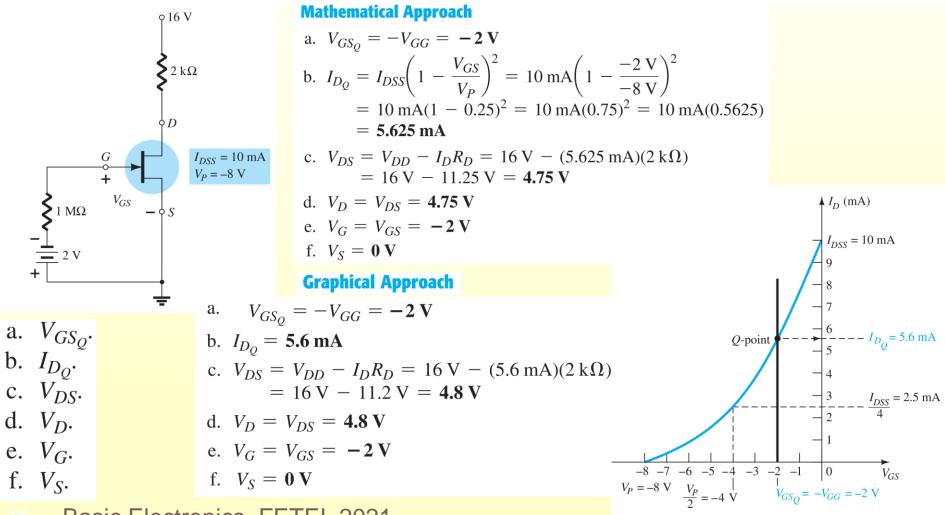

## JFET Biasing: Gate bias/Fixed Bias Configuration

$$V_{DS} = V_{DD} - I_D R_D$$

$$V_S = 0 V$$

$$V_C = V_{DS}$$

$$V = V_{GS}$$

$$V_{GS} = -V_{GG}$$

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

# Example

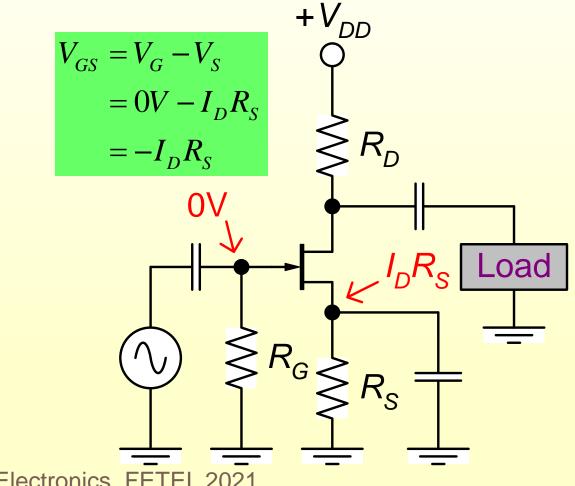

## JFET Biasing: Self-Bias Configuration

#### <sup>19</sup> Basic Electronics, FETEL 2021

# JFET Biasing:

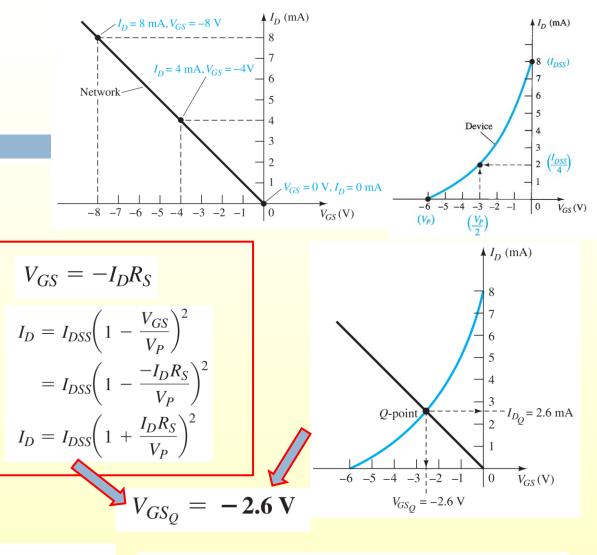

**Self-Bias Calculations**

#### **Graphical calculations**

$$V_{GS} = -I_D R_S$$

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

1. Select a value of  $I_D < I_{DSS}$  and use the component value of  $R_S$  to calculate  $V_{GS}$ . Plot the point identified by  $I_D$  and  $V_{GS}$  and draw a line from the origin of the axis to this point.

2. Plot the transfer curve using  $I_{DSS}$  and  $V_P$  ( $V_P = |V_{GSoff}|$  on spec sheets) and a few points such as  $V_{GS} = V_P / 4$  and  $V_{GS} = V_P / 2$  etc.

The Q-point is located where the first line intersects the transfer curve. Using the value of  $I_D$  at the Q-point ( $I_{DQ}$ ):

$$V_{DS} = V_{DD} - I_D (R_S + R_D)$$

$$V_{S} = I_{D}R_{S}$$

$$V_D = V_{DS} + V_S = V_{DD} - V_{RD}$$

<sup>20</sup> Basic Electronics, FETEL 2021

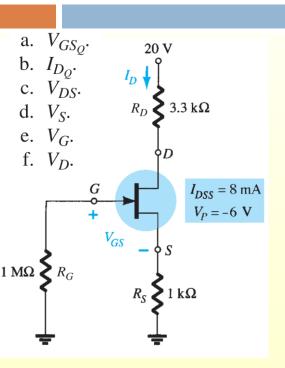

# Example

b. At the quiescent point

21

$$I_{D_Q} = 2.6 \text{ mA}$$

c.  $V_{DS} = V_{DD} - I_D(R_S + R_D)$

$= 20 \text{ V} - (2.6 \text{ mA})(1 \text{ k}\Omega + 3.3 \text{ k}\Omega)$

$= 20 \text{ V} - 11.18 \text{ V}$

Basic Electronics VETEL 2021

d.

$$V_S = I_D R_S$$

$= (2.6 \text{ mA})(1 \text{ k}\Omega)$

$= 2.6 \text{ V}$

e.  $V_G = 0 \text{ V}$

f.  $V_D = V_{DS} + V_S = 8.82 \text{ V} + 2.6 \text{ V} = 11.42 \text{ V}$

$V_D = V_{DD} - I_D R_D = 20 \text{ V} - (2.6 \text{ mA})(3.3 \text{ k}\Omega) = 11.42 \text{ V}$

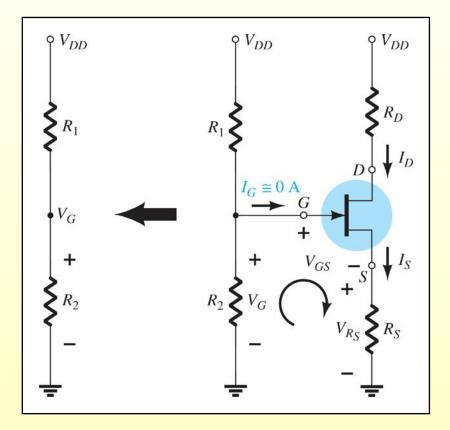

# JFET Biasing:

Voltage-Divider Bias

$I_{G} = 0 A$

$I_D$  responds to changes in  $V_{GS}$ .

<sup>22</sup> Basic Electronics, FETEL 2021

## JFET Biasing: Voltage-Divider Bias Calculations

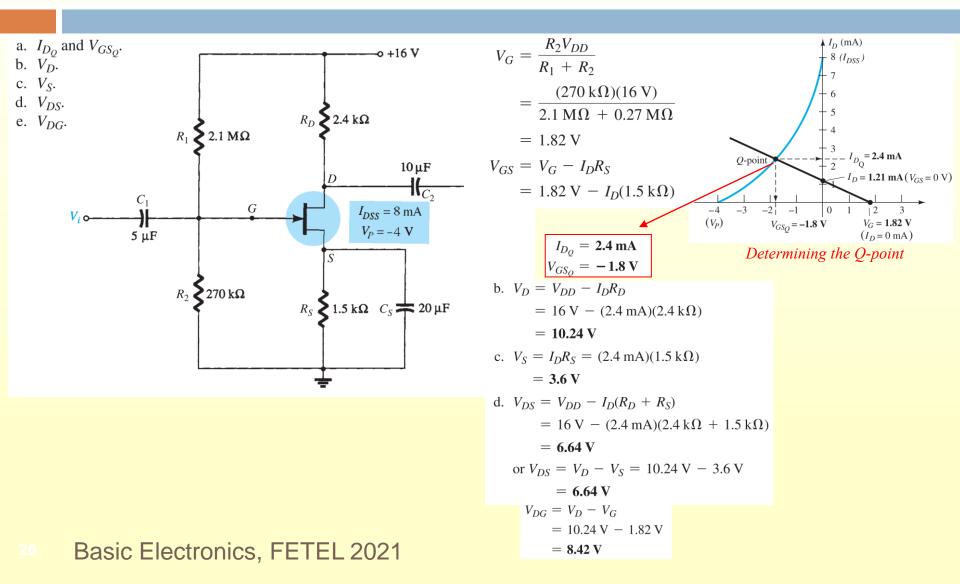

$V_G$  is equal to the voltage across divider resistor  $R_2$ :

$V_G = \frac{R_2 V_{DD}}{R_1 + R_2}$

Using Kirchhoff's Law:

$$V_{GS} = V_G - I_D R_S$$

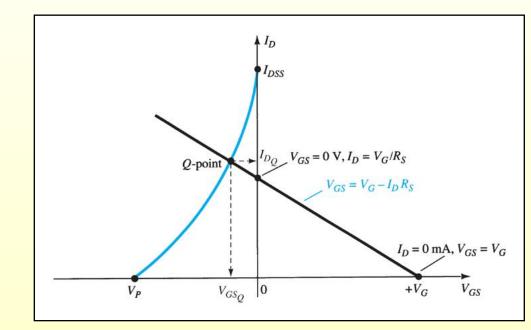

The Q-point is established by plotting a line that intersects the transfer curve.

<sup>23</sup> Basic Electronics, FETEL 2021

## JFET Biasing:

Voltage-Divider Q-Point

Plot the line that is defined by these two points:

$$V_{GS} = V_G, \ I_D = 0 \text{ A}$$

$$V_{GS} = 0$$

V,  $I_D = V_G / R_S$

Plot the transfer curve by plotting  $I_{DSS}$ ,  $V_P$  and the calculated values of  $I_D$

#### The Q-point is located where the line intersects the transfer curve

## JFET Biasing: Voltage-Divider Bias Calculations

# Using the value of $I_D$ at the Q-point, solve for the other values in the voltage-divider bias circuit:

$$V_{DS} = V_{DD} - I_D(R_D + R_S)$$

$$V_D = V_{DD} - I_D R_D$$

$$V_S = I_D R_S$$

<sup>25</sup> Basic Electronics, FETEL 2021

# Example

## **JFET Amplifiers**

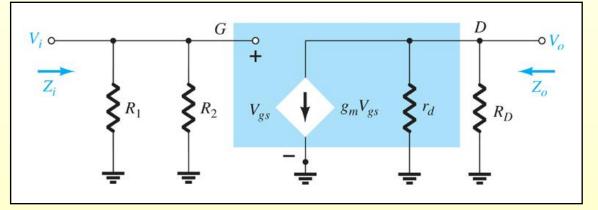

# JFET amplifier:

FET Small-Signal Model

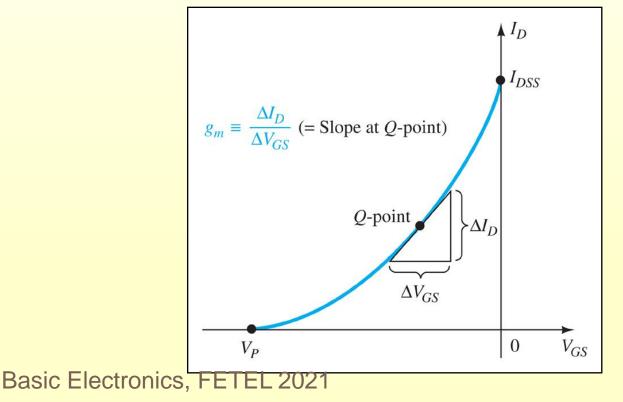

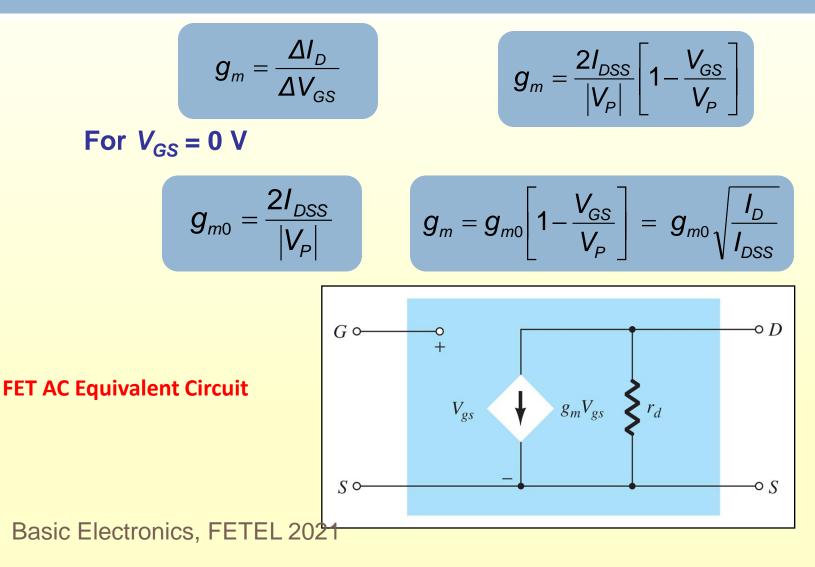

**Transconductance:** The ratio of a change in  $I_D$  to the corresponding change in  $V_{GS}$

• Transconductance is denoted  $g_m$  and given by:

$=\frac{\Delta I_{D}}{\Delta V_{C}}$  $g_m$

# **JFET amplifier:**

Mathematical Definitions of g<sub>m</sub>

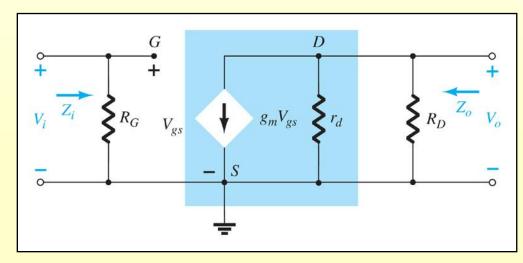

## JFET amplifier: FET Impedance

#### **Input impedance:**

$$Z_i = \infty \Omega$$

#### **Output Impedance:**

$$Z_o = r_d = \frac{1}{y_{os}}$$

where  $r_d = \frac{\Delta V_{DS}}{\Delta I_D} \Big|_{V_{GS} = \text{constant}}$

$y_{os}$ = admittance parameter listed on FET spec sheets

<sup>30</sup> Basic Electronics, FETEL 2021

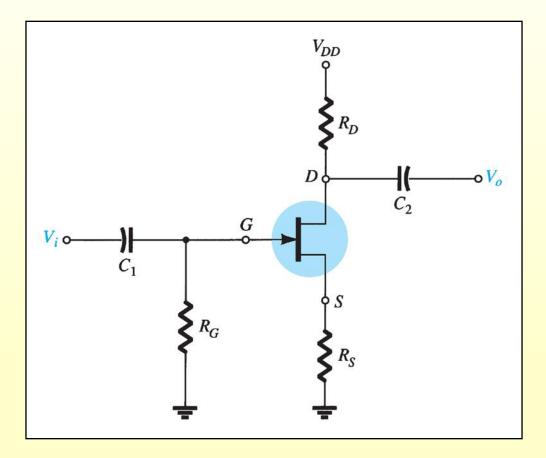

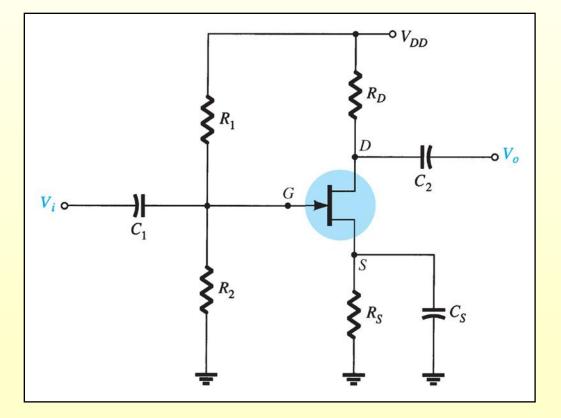

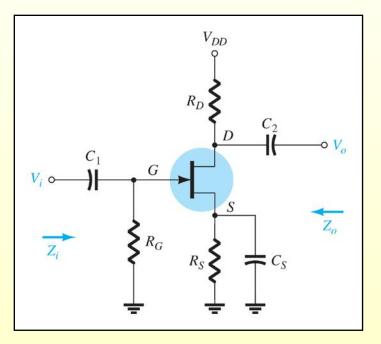

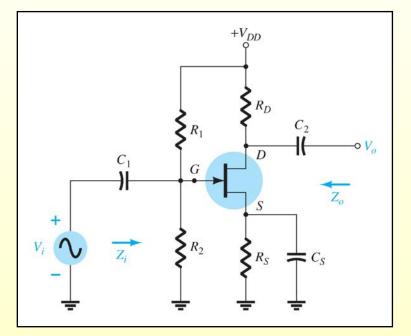

## JFET amplifier: Common-Source (CS) Self-Bias

This is a common-source amplifier configuration, so the input is applied to the gate and the output is taken from the drain.

There is a 180° phase shift between input and output.

## JFET amplifier:

Common-Source (CS) Self-Bias Calculation

### Input impedance:

$Z_i = R_G$

#### **Output impedance:**

$$Z_o = r_d || R_D$$

$$Z_o \cong R_D \Big|_{r_d \ge 10 R_D}$$

$\begin{array}{c} & & & & \\ \bullet & & \\ \bullet & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ &$

Voltage gain:

$$A_{v} = -g_{m}(r_{d}||R_{D})$$

$$A_{v} = -g_{m}R_{D}|_{r_{d} \ge 10R_{D}}$$

Electronic Devices and Circuit Theory Pearson Higher Education, Inc

**Basic Electronics, Fetel 2019**

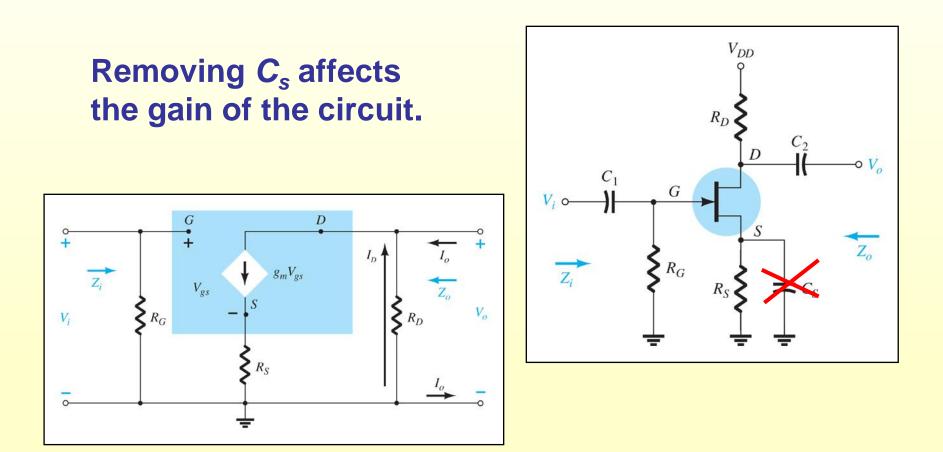

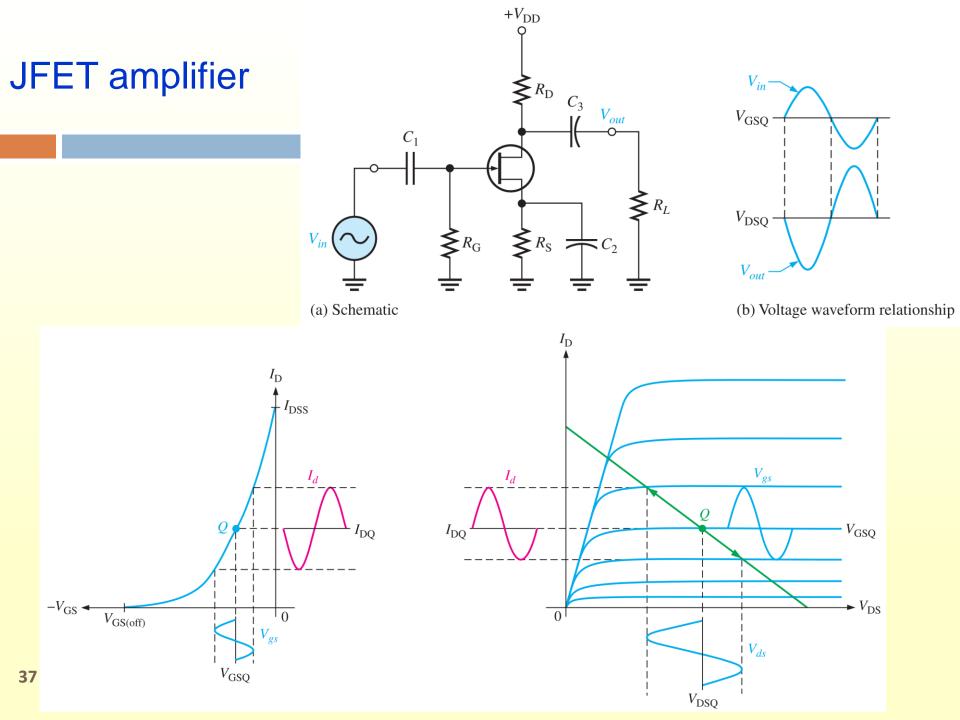

## JFET amplifier: Common-Source (CS) Self-Bias Calculation, without C<sub>s</sub>

## JFET amplifier: Common-Source (CS) Self-Bias Calculation, without C<sub>s</sub>

## Input impedance: $Z_i = R_G$

**Output impedance:**

$Z_o \cong R_D \Big|_{r_d \ge 10 R_D}$

## Voltage gain:

$$\begin{array}{c} & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$$

$$A_{v} = \frac{V_{o}}{V_{i}} = -\frac{g_{m}R_{D}}{1 + g_{m}R_{S} + \frac{R_{D} + R_{S}}{r_{d}}}$$

$$A_{v} = \frac{V_{o}}{V_{i}} = -\frac{g_{m}R_{D}}{1 + g_{m}R_{S}}\Big|_{r_{d} \ge 10(R_{D} + R_{S})}$$

<sup>34</sup> Basic Electronics, FETEL 2021

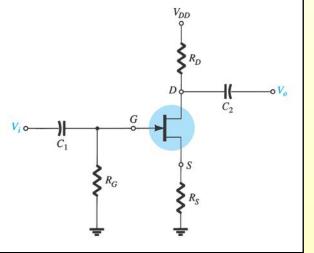

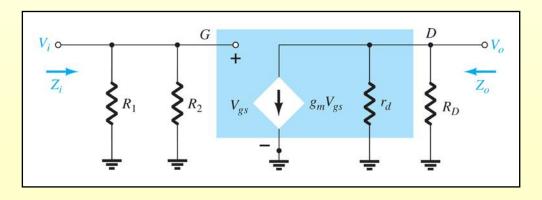

# JFET amplifier:

#### Common-Source (CS) Voltage-Divider Bias

This is a common-source amplifier configuration, so the input is applied to the gate and the output is taken from the drain.

#### <sup>35</sup> Basic Electronics, FETEL 2021

## JFET amplifier:

#### Common-Source (CS) Voltage-Divider Bias

#### Impedances

#### Input impedance:

$$Z_i = R_1 || R_2$$

# Output impedance:

$$Z_{o} = I_{d} \prod X_{D}$$

$$Z_{o} \cong R_{D} \Big|_{r_{d} \ge 10 R_{D}}$$

# Voltage gain:

$$A_{v} = -g_{m}(r_{d}||R_{D})$$

$$A_{v} = -g_{m}R_{D}|_{r_{d} \ge 10R_{D}}$$

**EXAMPLE 8.8** The self-bias configuration of Example 7.2 has an operating point defined by  $V_{GS_Q} = -2.6$  V and  $I_{D_Q} = 2.6$  mA, with  $I_{DSS} = 8$  mA and  $V_P = -6$  V. The network is redrawn as Fig. 8.20 with an applied signal  $V_i$ . The value of  $g_{os}$  is given as 20  $\mu$ S.

- a. Determine  $g_m$ .

- b. Find  $r_d$ .

- c. Find  $Z_i$ .

- d. Calculate  $Z_o$  with and without the effects of  $r_d$ . Compare the results.

- e. Calculate  $A_v$  with and without the effects of  $r_d$ . Compare the results.

Solution:

a.

$$g_{m0} = \frac{2I_{DSS}}{|V_P|} = \frac{2(8 \text{ mA})}{6 \text{ V}} = 2.67 \text{ mS}$$

$g_m = g_{m0} \left( 1 - \frac{V_{GS_Q}}{V_P} \right) = 2.67 \text{ mS} \left( 1 - \frac{(-2.6 \text{ V})}{(-6 \text{ V})} \right) = 1.51 \text{ mS}$

b.  $r_d = \frac{1}{y_{os}} = \frac{1}{20 \,\mu\text{S}} = 50 \text{ k}\Omega$

c.  $Z_i = R_G = 1 \text{ M}\Omega$

d. With  $r_d$ ,

$r_d = 50 \text{ k}\Omega > 10R_D = 33 \text{ k}\Omega$

$$r_d = 50 \,\mathrm{k}\Omega > 10R_D = 33 \,\mathrm{k}$$

Therefore,

$$Z_o = R_D = 3.3 \,\mathrm{k}\Omega$$

If  $r_d = \infty \Omega$ ,

$$Z_o = R_D = 3.3 \,\mathrm{k}\Omega$$

e. With  $r_d$ ,

39

$$A_{v} = \frac{-g_{m}R_{D}}{1 + g_{m}R_{S} + \frac{R_{D} + R_{S}}{r_{d}}} = \frac{-(1.51 \text{ mS})(3.3 \text{ k}\Omega)}{1 + (1.51 \text{ mS})(1 \text{ k}\Omega) + \frac{3.3 \text{ k}\Omega + 1 \text{ k}\Omega}{50 \text{ k}\Omega}}$$

$$= -1.92$$

With  $r_{d} = \infty \Omega$  (open-circuit equivalence),

Basic Electronics,  $\overline{A_{v}} = \frac{\Xi \Box 2 \partial \Delta A}{1 + g_{m}R_{S}} = \frac{-(1.51 \text{ mS})(3.3 \text{ k}\Omega)}{1 + (1.51 \text{ mS})(1 \text{ k}\Omega)} = -1.98$

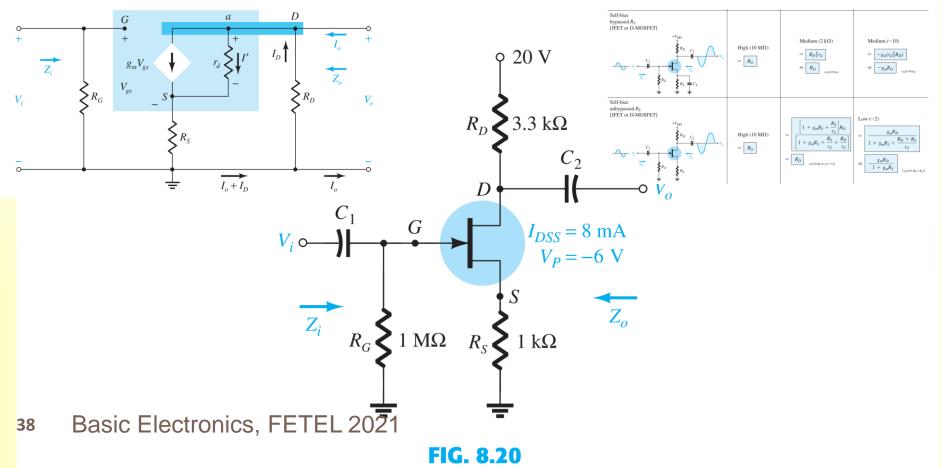

FET Bias Configurations

| Туре                                                                      | Configuration      | Pertinent Equations                                                                               | <b>Graphical Solution</b>                                                                                     |

|---------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| JFET<br>Fixed-bias                                                        |                    | $V_{GS_Q} = -V_{GG}$ $V_{DS} = V_{DD} - I_D R_S$                                                  | $\begin{array}{c c} & I_D \\ I_{DSS} \\ \hline \\ \hline \\ V_P \ V_{GG} \ 0 \\ \hline \\ V_{GS} \end{array}$ |

| JFET<br>Self-bias                                                         | $R_{G}$            | $V_{GS} = -I_D R_S$ $V_{DS} = V_{DD} - I_D (R_D + R_S)$                                           | $Q-\text{point}$ $Q-\text{point}$ $V_{P  IV'_{GS}} = 0$ $V_{GS}$                                              |

| JFET<br>Voltage-divider<br>bias                                           | $R_1$              | $V_G = \frac{R_2 V_{DD}}{R_1 + R_2}$ $V_{GS} = V_G - I_D R_S$ $V_{DS} = V_{DD} - I_D (R_D + R_S)$ | $Q-\text{point}$ $V_{B}$ $V_{G}$ $V_{G}$ $V_{GS}$                                                             |

| JFET<br>$(R_D = 0 \ \Omega)$                                              |                    | $V_{GS} = -I_D R_S$ $V_D = V_{DD}$ $V_S = I_D R_S$ $V_{DS} = V_{DD} - I_S R_S$                    | $Q-\text{point} \qquad V_P + V'_{GS} \qquad 0 \qquad V_{GS}$                                                  |

| JFET<br>Special case<br>$(V_{GS_Q} = 0 \text{ V})$<br><b>41</b> Basic Ele | ctronics, FETEL 20 | $V_{GS_Q} = 0 V$ $I_{D_Q} = I_{DSS}$                                                              | $Q\text{-point} \qquad I_D \\ I_{DSS} \\ V_{GSQ} = 0 \text{ V} \\ V_P \qquad 0 \qquad V_{GS}$                 |

| Depletion-type<br>MOSFET<br>Fixed-bias<br>(and MESFETs)                  |                                                                                                                                | $V_{GS_Q} = +V_{GG}$ $V_{DS} = V_{DD} - I_D R_S$                                                  | $I_{DSS}$ $Q$ -point $I_{DSS}$ $V_P = 0$ $V_{GG} = V_{GS}$                                                                                                                                                                 |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Depletion-type<br>MOSFET<br>Voltage-divider<br>bias<br>(and MESFETs)     | $R_1 R_D V_{DD}$                                                                                                               | $V_G = \frac{R_2 V_{DD}}{R_1 + R_2}$ $V_{GS} = V_G - I_S R_S$ $V_{DS} = V_{DD} - I_D (R_D + R_S)$ | $\begin{array}{c c} V_{G} & I_{D} \\ \hline R_{S} & Q \text{-point} \\ I_{DSS} & Q \text{-point} \\ \hline V_{P} & 0 & V_{G} V_{GS} \end{array}$                                                                           |

| Enhancement<br>type MOSFET<br>Feedback<br>configuration<br>(and MESFETs) |                                                                                                                                | $V_{GS} = V_{DS}$ $V_{GS} = V_{DD} - I_D R_D$                                                     | $\begin{array}{c c} V_{DD} & I_D \\ \hline R_D \\ I_{D(\text{on})} \\ \hline \end{array} \\ \hline \\ 0 \\ \hline \\ V_{GS(\text{Th})} \\ \hline \\ V_{GS(\text{on})} \\ \hline \\ V_{DD} \\ V_{GS} \\ \hline \end{array}$ |

| Enhancement<br>type MOSFET<br>Voltage-divider<br>bias<br>(and MESFETs)   | $\begin{array}{c} \begin{array}{c} \begin{array}{c} \begin{array}{c} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ | $V_G = \frac{R_2 V_{DD}}{R_1 + R_2}$ $V_{GS} = V_G - I_D R_S$                                     | $\begin{array}{c c} V_{G} & I_{D} \\ \hline \\ Q\text{-point} \\ \hline \\ 0 & V_{GS(\text{Th})} & V_{G} & V_{GS} \end{array}$                                                                                             |

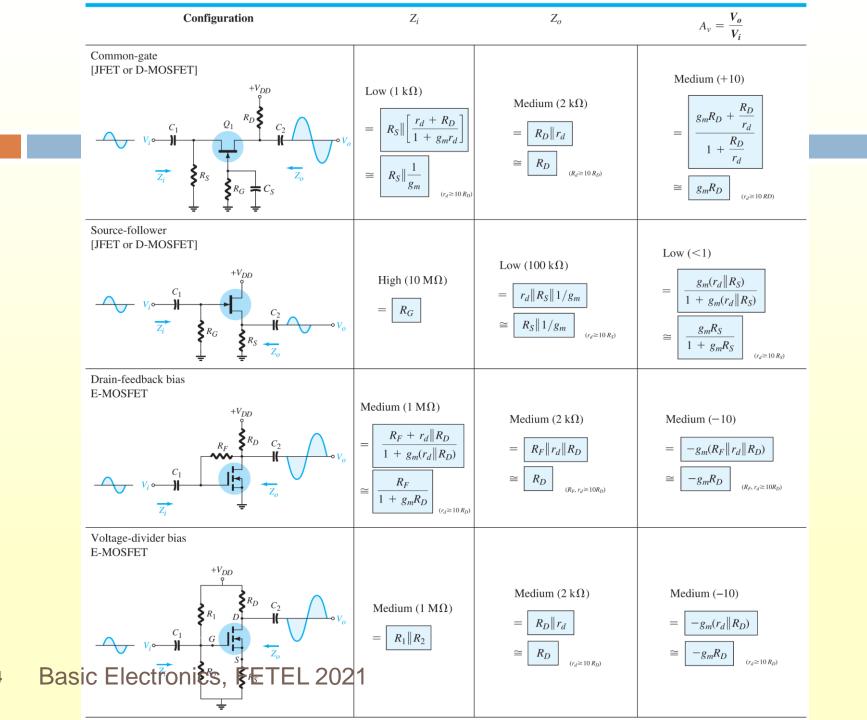

$Z_i$ ,  $Z_o$ , and  $A_v$  for various FET configurations

43

Admittance is defined as

$$Y \equiv \frac{1}{Z}$$

where

Y is the admittance, measured in <u>siemens</u>, Dẫn nạp Z is the <u>impedance</u>, measured in <u>ohms</u>

$$Y = G + jB$$

#### here

Y is the admittance, measured in siemens.

G is the <u>conductance</u>, measured in siemens. Độ dẫn

B is the susceptance, measured in siemens. Điện nạp