ĐẠI HỌC QUỐC GIA THÀNH PHỐ HÒ CHÍ MINH TRƯỜNG KHOA HỌC TỰ NHIÊN

VẬT LÝ LINH KIỆN ĐIỆN TỬ

#### Chap 3:

#### **BJT – BIPOLAR JUCNTION TRANSISTOR**

Trình bày: NGUYỄN THỊ THIÊN TRANG

# GIỚI THIỆU CHUNG

- ❖ Cấu tạo & nguyên lý hoạt động BJT

- Các cách mắc mạch & các dạng đặc tuyến tương ứng

- Phân cực cho BJT

- Các mô hình tương đương của BJT

- ❖ Phân loại BJT

- Một số ứng dụng BJT

- ❖ Giản đồ năng lượng BJT

- ❖ Quy trình chế tạo BJT

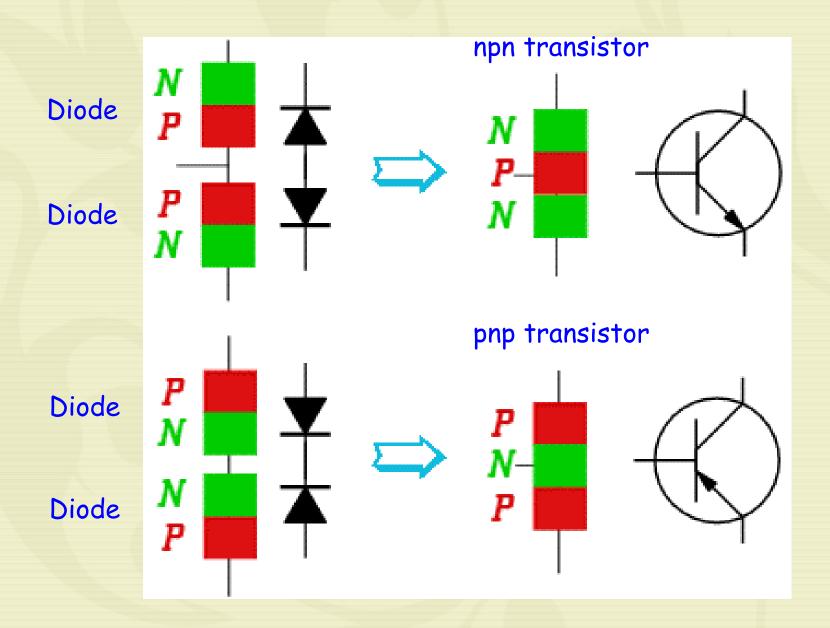

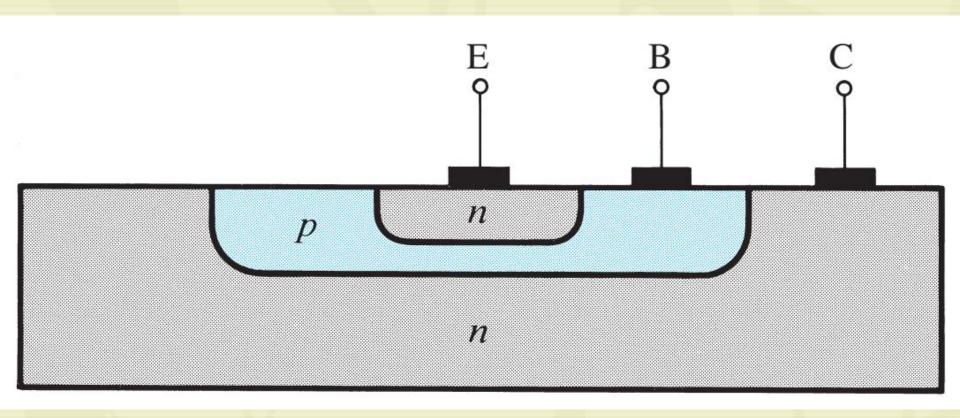

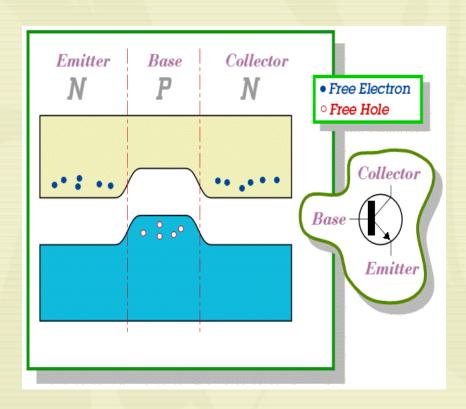

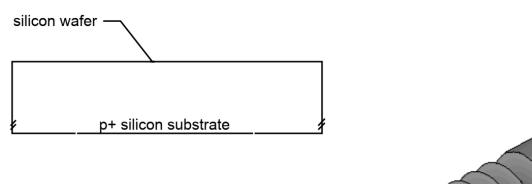

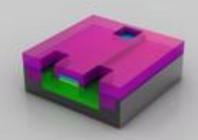

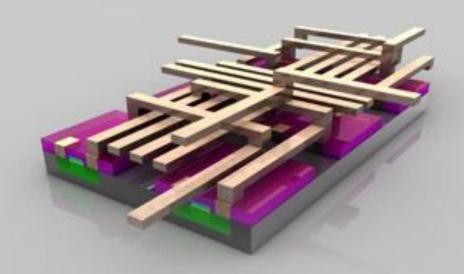

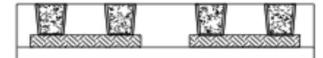

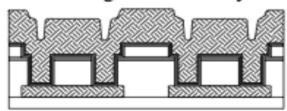

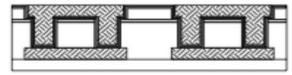

Cấu tạo mặt cắt ngang của transistor NPN

pnp

npn

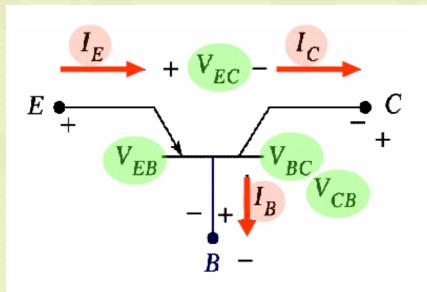

Two of the currents and two of the voltages are independent.

If two of the currents or voltages are known, third terminal current or voltage is determined.

$$\begin{split} \boldsymbol{I}_{\scriptscriptstyle E} &= \boldsymbol{I}_{\scriptscriptstyle B} + \boldsymbol{I}_{\scriptscriptstyle C} \\ \boldsymbol{V}_{\scriptscriptstyle EB} &+ \boldsymbol{V}_{\scriptscriptstyle BC} + \boldsymbol{V}_{\scriptscriptstyle CE} = 0 \end{split}$$

Current flowing into a device = current flowing out of device

$$(V_{\mathit{CE}} = - \ V_{\mathit{EC}})$$

- Vùng phát E pha đậm,

- Vùng nền rất hẹp và pha lợt (nhẹ)

- Vùng thu C lớn nhất và pha trung gian giữa vùng phát pha đậm và vùng nền pha lợt

- → Tên gọi nhằm ám chỉ:

Cực phát (Emitter) phát các hạt tải đến cực thu (collector) và dòng hạt tải này được điều khiển bởi cực nền (base)

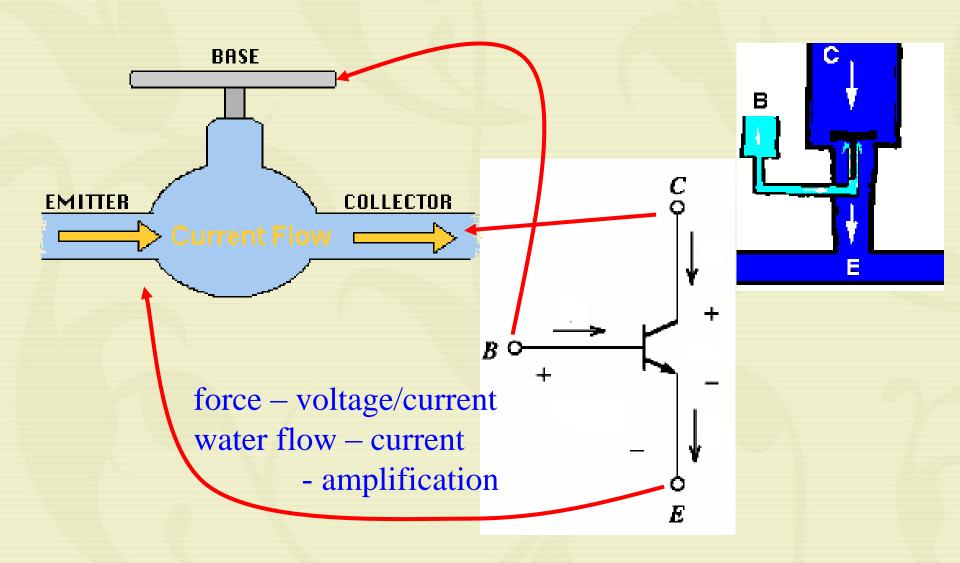

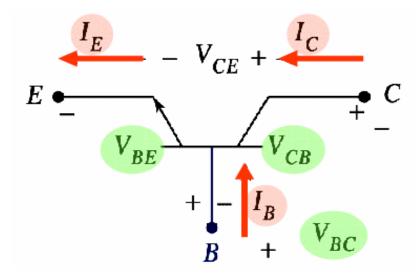

### NGUYÊN LÝ HOẠT ĐỘNG

### NGUYÊN LÝ HOẠT ĐỘNG

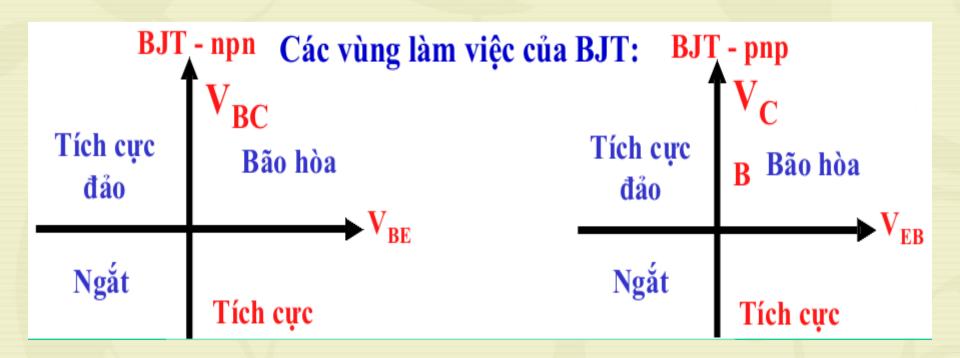

+ Chế độ đảo (tích cực đảo): Tiếp giáp BE phân cực ngược, tiếp giáp BC phân cực thuận, đây là chế độ không mong muốn

### NGUYÊN LÝ HOẠT ĐỘNG

- Gồm có 3 đặc tuyến thông dụng sau:

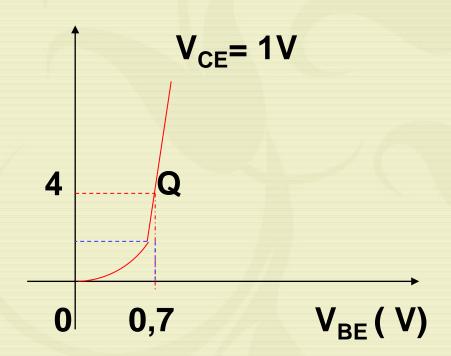

- a. Đặc tuyến vào  $I_B = f(V_{BE})_{VCE = Cte}$   $I_B(mA)$

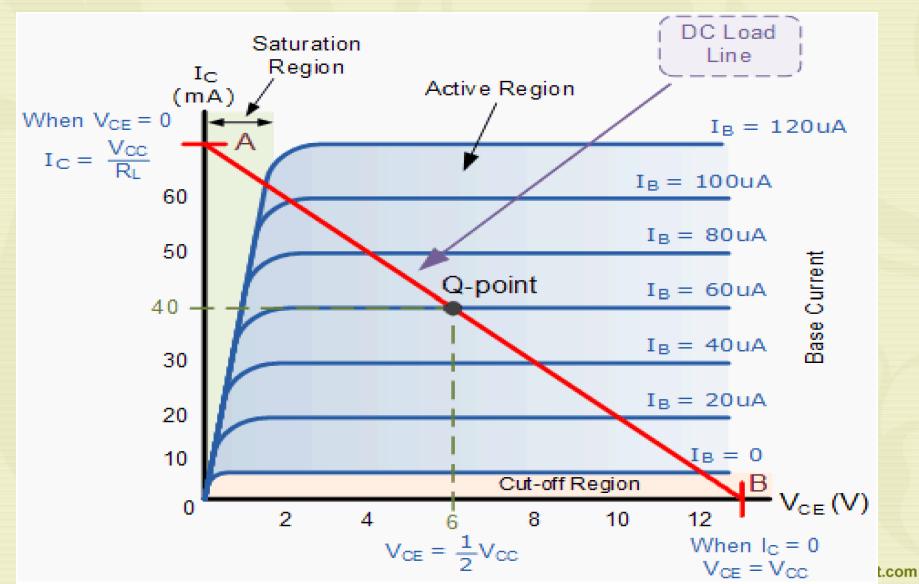

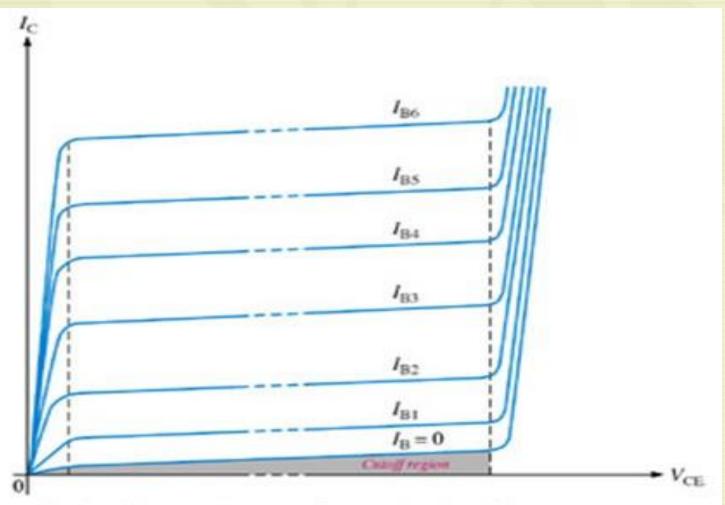

b. Đặc tuyến ra  $I_C = f(V_{CE}) I_B = Cte$

b. Đặc tuyến ra  $I_C = f(V_{CE}) I_B = Cte$

(c) Family of I<sub>C</sub> versus V<sub>CE</sub> curves for several values of I<sub>B</sub> (I<sub>B1</sub>< I<sub>B2</sub>< I<sub>B3</sub>, etc.)

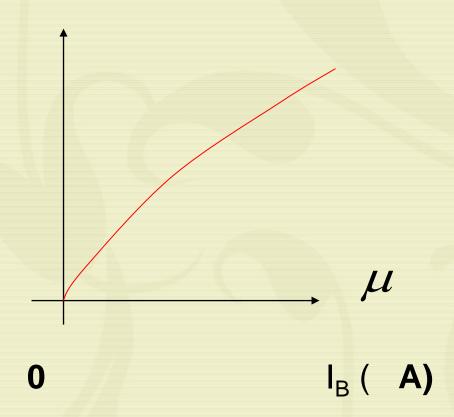

c. Đặc tuyến truyền IC =  $f(IB)V_{CE} = Cte$

Ic (mA)

- Trong dải thay đổi

nhỏ của l<sub>B</sub>, l<sub>C</sub> thay đổi

tuyến tính.

- Khi dòng l<sub>B</sub> lớn , l<sub>C</sub>

không còn tuyến tính

| Characteristic   | Common<br>Base | Common<br>Emitter | Common<br>Collector |  |  |

|------------------|----------------|-------------------|---------------------|--|--|

| Input Impedance  | Low            | Medium            | High                |  |  |

| Output Impedance | Very High      | High              | Low                 |  |  |

| Phase Angle      | 0°             | 180°              | 0°                  |  |  |

| Voltage Gain     | High           | Medium            | Low                 |  |  |

| Current Gain     | Low            | Medium            | High                |  |  |

| Power Gain       | Low            | Very High         | Medium              |  |  |

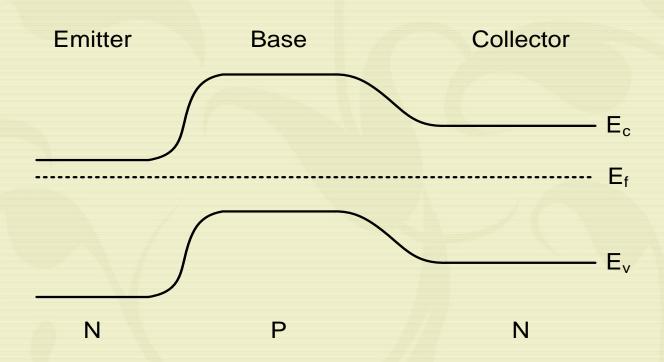

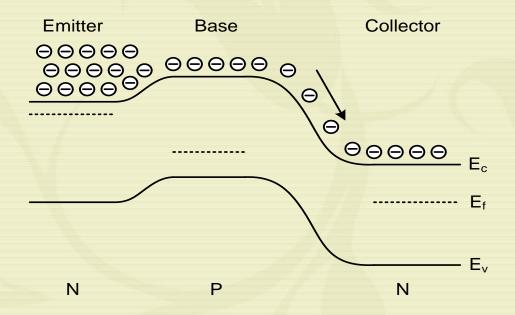

# BJT GIẢN ĐỒ NĂNG LƯỢNG

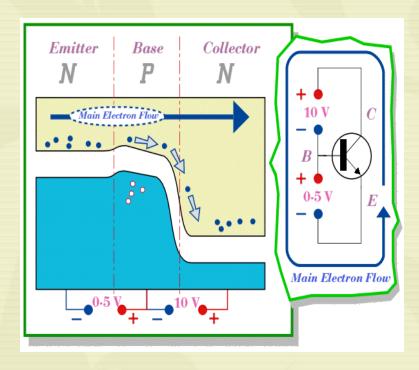

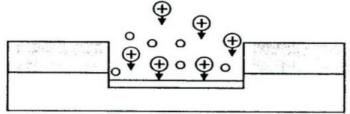

#### How the BJT works

**NPN Bipolar Transistor**

- Figure shows the energy levels in an NPN transistor under no externally applying voltages.

- In each of the N-type layers conduction can take place by the free movement of electrons in the conduction band.

- In the P-type (filling) layer conduction can take place by the movement of the free holes in the valence band.

- However, in the absence of any externally applied electric field, we find that depletion zones form at both PN-Junctions, so no charge wants to move from one layer to another.

#### How the BJT works

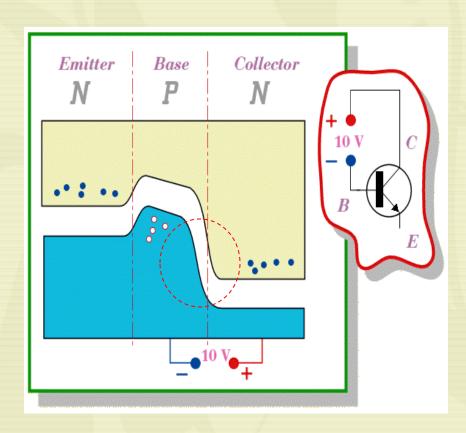

Apply a Collector-Base voltage

- What happens when we apply a moderate voltage between the collector and base parts.

- The polarity of the applied voltage is chosen to increase the force pulling the N-type electrons and Ptype holes apart.

- This widens the depletion zone between the collector and base and so no current will flow.

- In effect we have reversebiassed the Base-Collector diode junction.

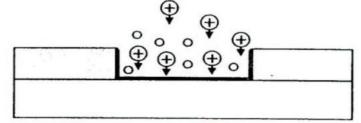

### Charge Flow

Apply an Emitter-Base voltage

- What happens when we apply a relatively small Emitter-Base voltage whose polarity is designed to forwardbias the Emitter-Base junction.

- This 'pushes' electrons from the Emitter into the Base region and sets up a current flow across the Emitter-Base boundary.

- Once the electrons have managed to get into the Base region they can respond to the attractive force from the positively-biassed Collector region.

- As a result the electrons which get into the Base move swiftly towards the Collector and cross into the Collector region.

- Hence a Emitter-Collector current magnitude is set by the chosen Emitter-Base voltage applied.

- Hence an external current flowing in the circuit.

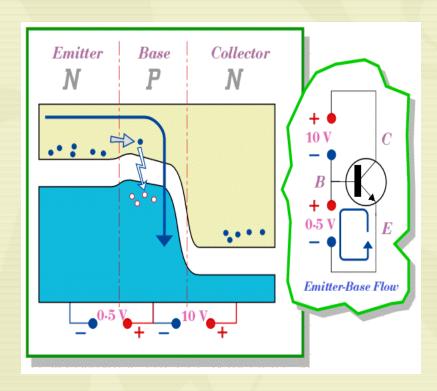

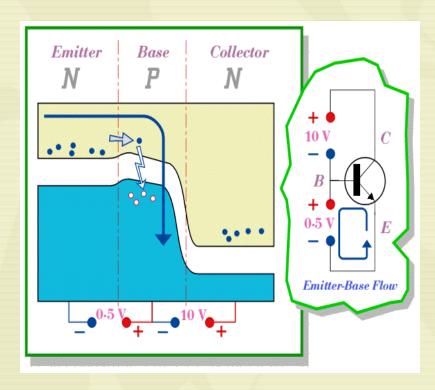

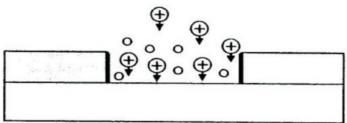

### Charge Flow

Some electron fall into a hole

- Some of free electrons crossing the Base encounter a hole and 'drop into it'.

- As a result, the Base region loses one of its positive charges (holes).

- The Base potential would become more negative (because of the removal of the holes) until it was negative enough to repel any more electrons from crossing the Emitter-Base junction.

- The current flow would then stop.

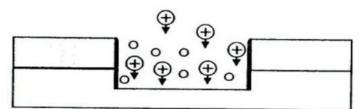

### Charge Flow

Some electron fall into a hole

- To prevent this happening we use the applied E-B voltage to remove the captured electrons from the base and maintain the number of holes.

- The effect, some of the electrons which enter the transistor via the Emitter emerging again from the Base rather than the Collector.

- For most practical BJT only about 1% of the free electrons which try to cross Base region get caught in this way.

- Hence a Base current, I<sub>B</sub>,

which is typically around one

hundred times smaller than the

Emitter current, I<sub>E</sub>.

#### GIẢN ĐỒ NĂNG LƯỢNG

Trạng thái cân bằng - không có dòng chuyển dời của hoạt mang điện

#### GIẢN ĐỒ NĂNG LƯỢNG

- EB phân cực thuận

- Rào thế giản và các electron khuếch tán dần sang cực B

- Các electron quét qua cực B để đến C

- CB phân cực nghịch

- Electron dịch chuyển xuống từ E sang C

#### FABRICATION PROCESS

https://www.youtube.com/watch?v=fwNkg1fsqBY

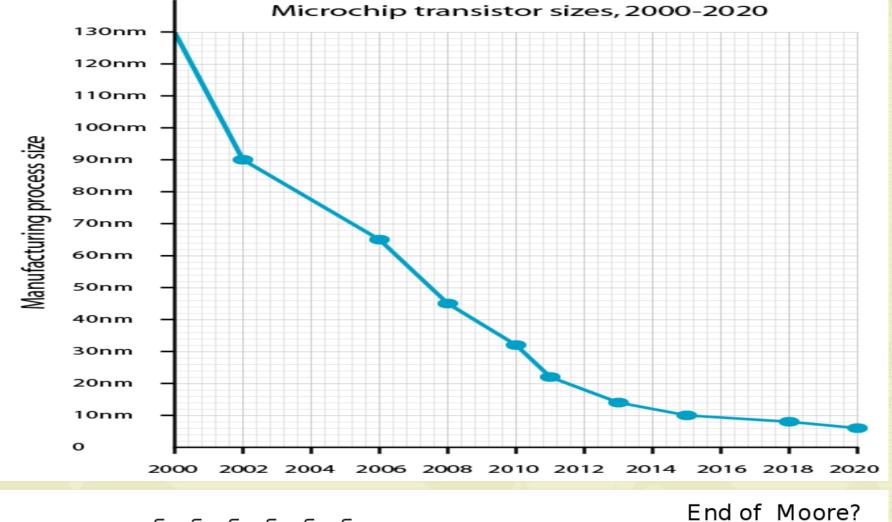

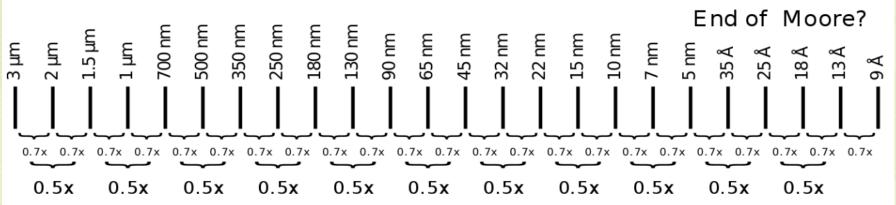

#### MINIMUM FEATURE SIZE

| Year | Processor         | Speed           | Transistors  | Process |

|------|-------------------|-----------------|--------------|---------|

| 1982 | i286              | 6 - 25 MHz      | ~134,000     | 1.5 μm  |

| 1986 | i386              | 16 – 40 MHz     | ~270,000     | 1 μm    |

| 1989 | i486              | 16 - 133 MHz    | ~1 million   | .8 μm   |

| 1993 | Pentium           | 60 - 300 MHz    | ~3 million   | .6 μm   |

| 1995 | Pentium Pro       | 150 - 200 MHz   | ~4 million   | .5 μm   |

| 1997 | Pentium II        | 233 - 450 MHz   | ~5 million   | .35 μm  |

| 1999 | Pentium III       | 450 – 1400 MHz  | ~10 million  | .25 μm  |

| 2000 | Pentium 4         | 1.3 – 3.8 GHz   | ~50 million  | .18 μm  |

| 2005 | Pentium D         | 2 cores/package | ~200 million | .09 μm  |

| 2006 | Core 2            | 2 cores/die     | ~300 million | .065 μm |

| 2008 | Core i7           | 4 cores/die     | ~800 million | .040 μm |

| 2010 | "Sandy<br>Bridge" | 8 cores/die     | ??           | .032 μm |

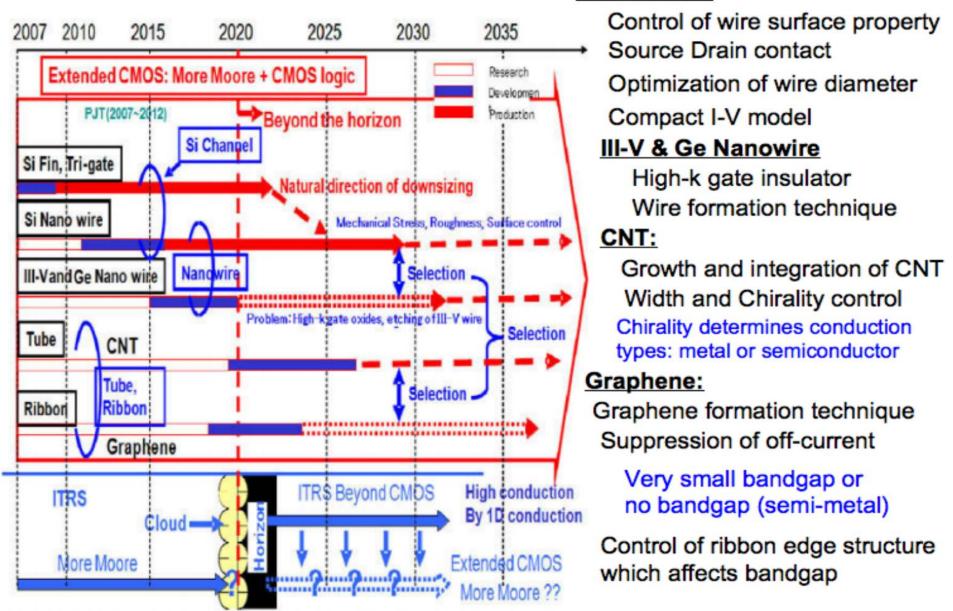

#### Current Issues Si Nanowire

Fig. 19. Long range roadmap for logic CMOS transistors for next 30 years.

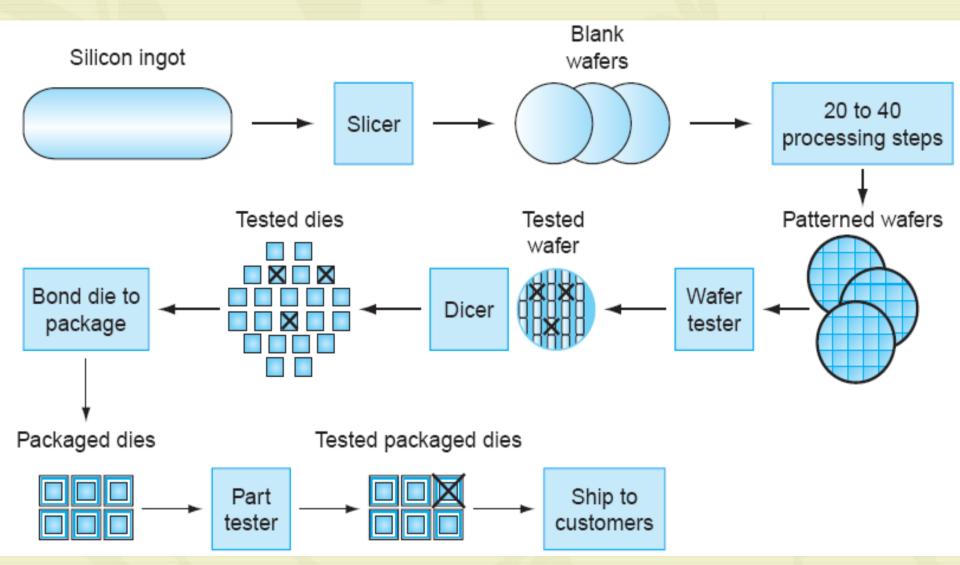

#### IC MANUFACTURING

#### IC FABRICATION

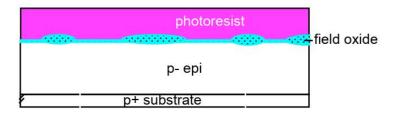

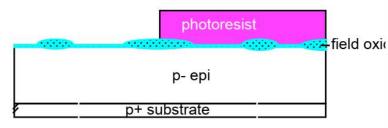

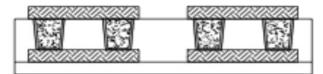

- Chips are fabricated using set of masks

- Photolithography

- Basic steps

- oxidize

- apply photoresist

- remove photoresist with mask

- HF acid eats oxide but not photoresist

- pirana acid eats photoresist

- ion implantation (diffusion, wells)

- vapor deposition (poly)

- plasma etching (metal)

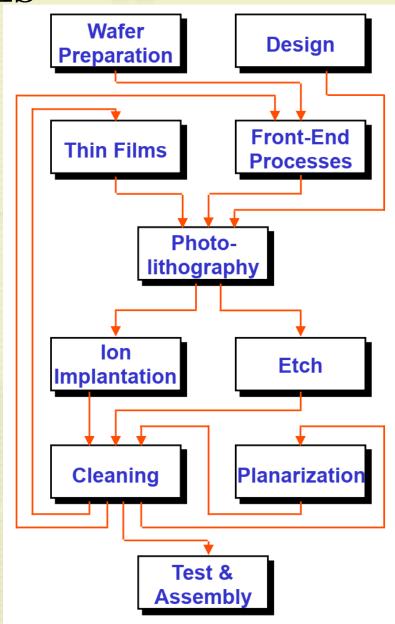

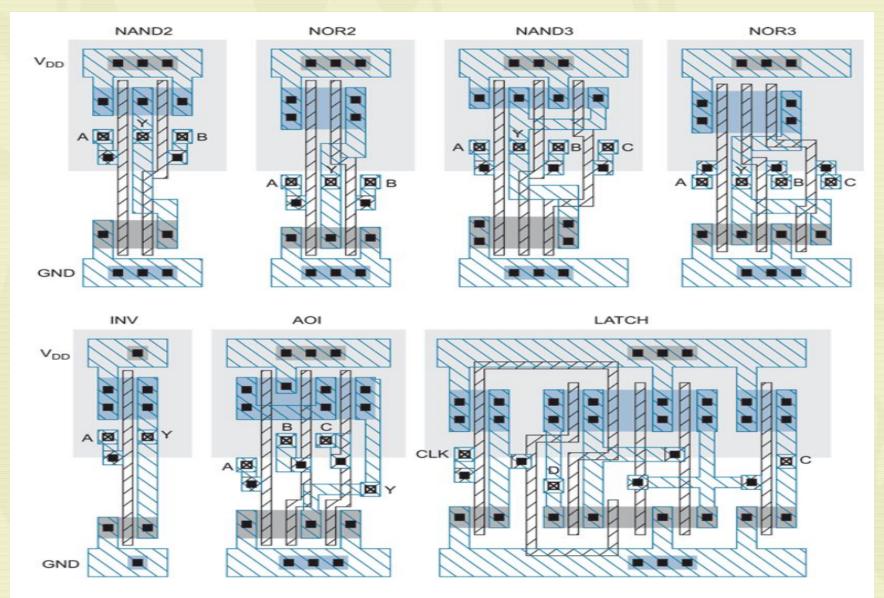

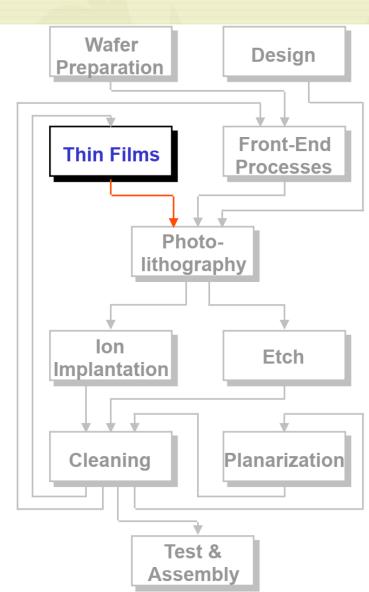

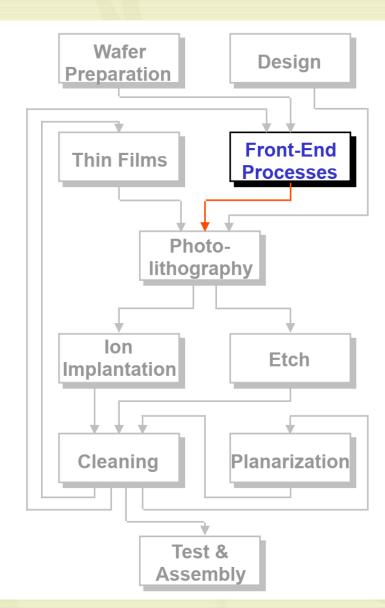

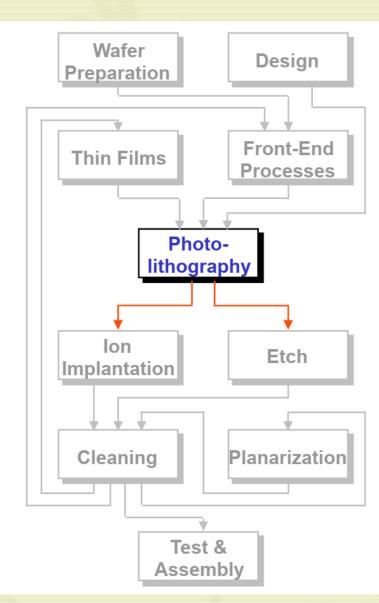

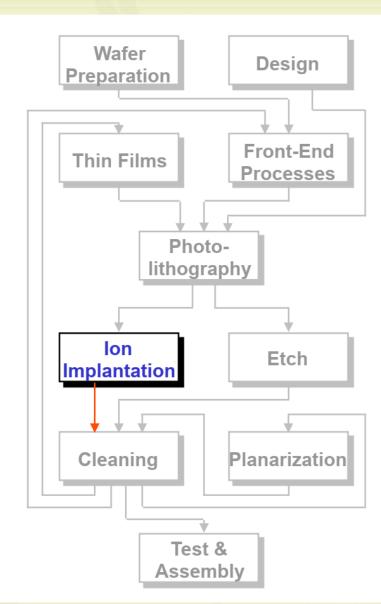

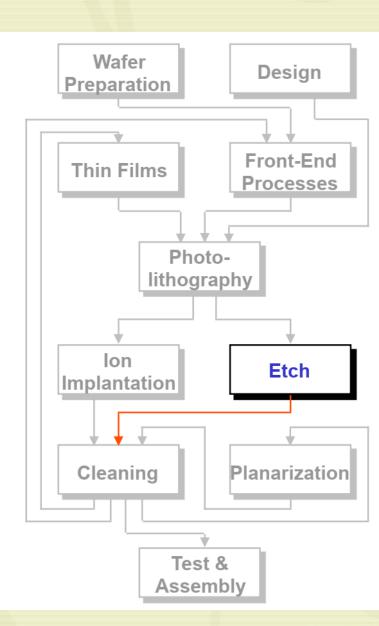

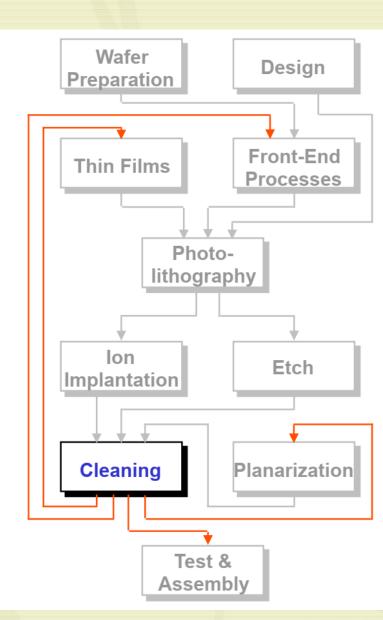

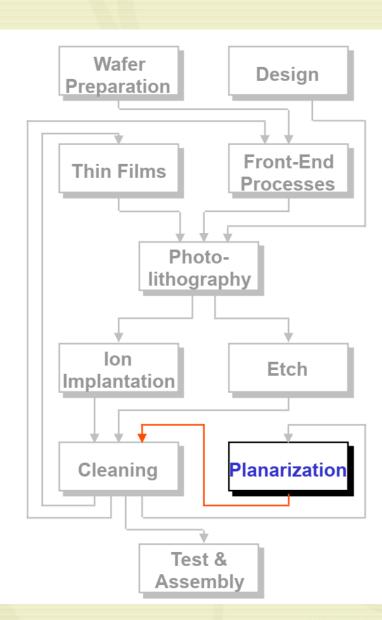

# SEMICONDUCTOR MANUFACTURING PROCESSES

- Design

- Wafer Preparation

- Front-end Processes

- Photolithography

- Etch

- Cleaning

- Thin Films

- Ion Implantation

- Planarization

- Test and Assembly

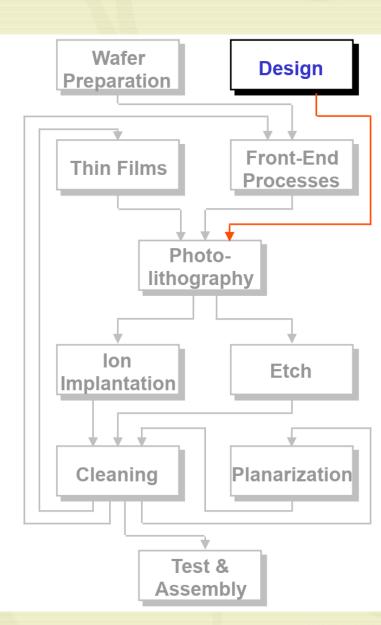

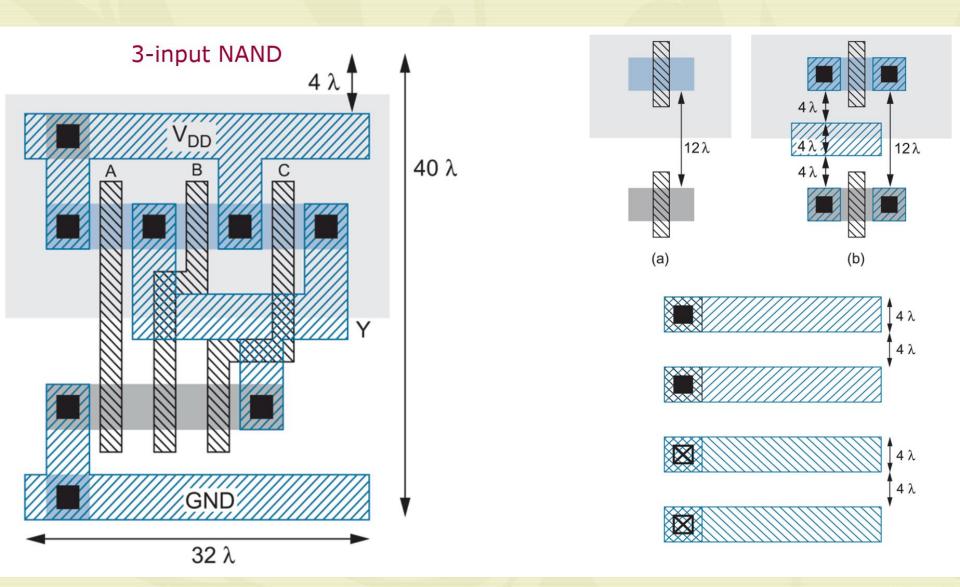

#### **DESIGN**

- Establish Design Rules

- Circuit Element Design

- Interconnect Routing

- Device Simulation

- Pattern Preparation

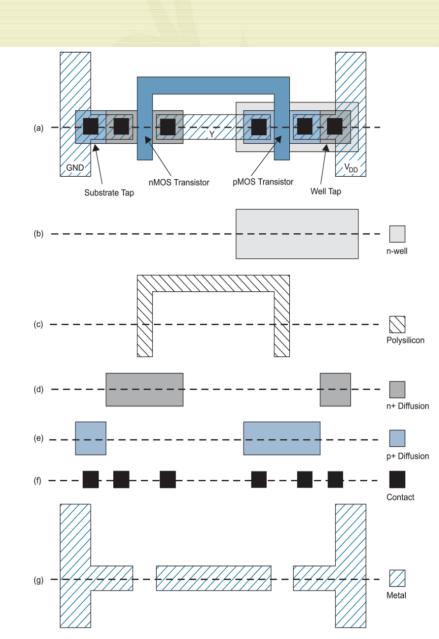

#### **DESIGN - LAYOUT**

#### DESIGN - ELEMENT CELL LIBRARY

Layout

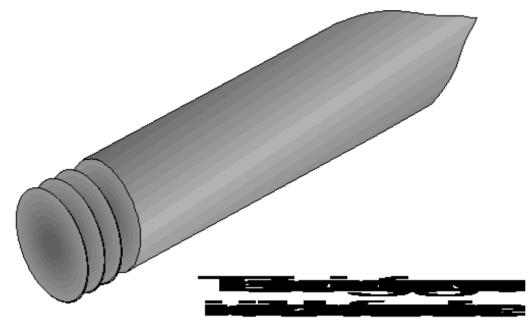

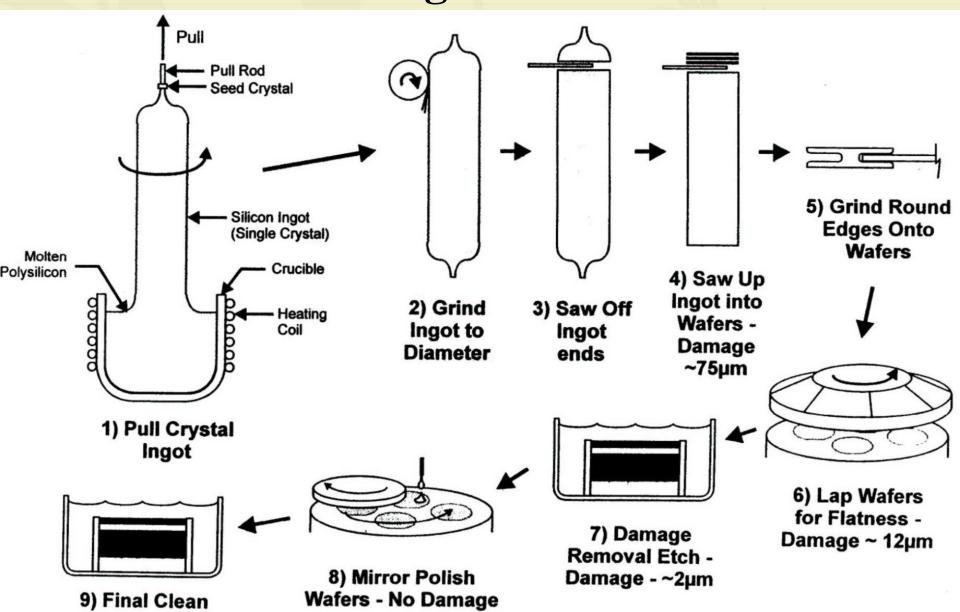

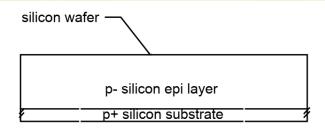

#### WAFER PREPARATION

- Polysilicon Refining

- Crystal Pulling

- Wafer Slicing & Polishing

- Epitaxial Silicon Deposition

#### WAFER PREPARATION – SAND/INGOT

With about 25% (mass) Silicon is – after Oxygen – the second most frequent chemical element in the earth's crust. Sand – especially Quartz - has high percentages of Silicon in the form of Silicon dioxide (SiO<sub>2</sub>) and is the base ingredient for semiconductor manufacturing.

Melted Silicon -

scale: wafer level (~300mm / 12 inch)

Silicon is purified in multiple steps to

finally reach semiconductor manufacturing

quality which is called Electronic Grade

Silicon. Electronic Grade Silicon may only

have one alien atom every one billion

Silicon atoms. In this picture you can see

how one big crystal is grown from the

purified silicon melt. The resulting mono

Mono-crystal Silicon Ingot – scale: wafer level (~300mm / 12 inch)

An ingot has been produced from Electronic Grade Silicon. One ingot weights about 100 kilograms (=220 pounds) and has a Silicon purity of 99.9999%.

#### WAFER PREPARATION – CRYSTAL PULLING

#### **Process Conditions**

Flow Rate: 20 to 50 liters/min

Time: 18 to 24 hours

Temperature: >1,300 degrees C

Pressure: 20 Torr

#### **Materials**

Polysilicon Nodules \*

Ar \*

$H_2$

<sup>\*</sup> High proportion of the total product use

## WAFER PREPARATION –INGOT/WAFER

Ingot Slicing – scale: wafer level (~300mm / 12 inch)

The Ingot is cut into individual silicon discs called wafers.

Wafer -

scale: wafer level (~300mm / 12 inch)

The wafers are polished until they have flawless, mirror-smooth surfaces. Intel buys those manufacturing ready wafers from third party companies. Intel's highly advanced 45nm High-K/Metal Gate process uses wafers with a diameter of 300 millimeter (~12 inches). When Intel first began making chips, the company printed circuits on 2-inch (50mm) wafers. Now the company uses 300mm wafers, resulting in decreased costs per chip.

# WAFER PREPARATION – Wafer Slicing & Polishing

The silicon ingot is sliced into individual wafers, polished, and cleaned.

# WAFER PREPARATION – Wafer Manufacturing Process Overview

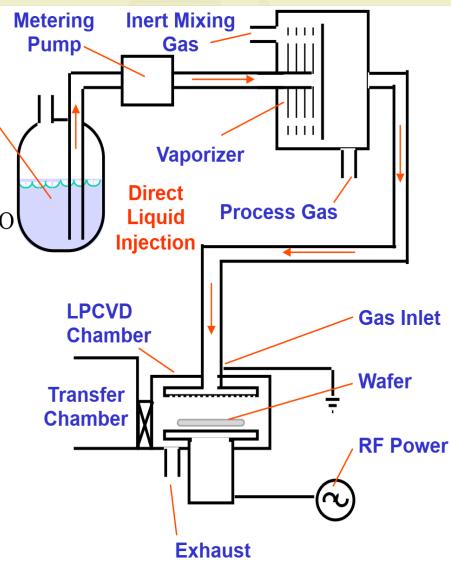

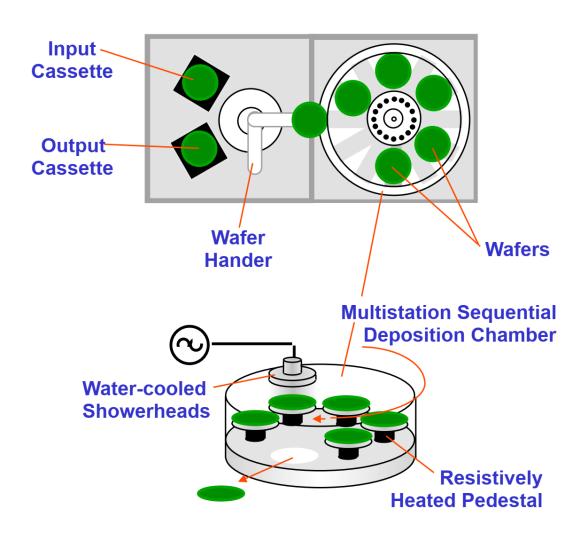

### THIN FILMS

- Chemical Vapor Deposition (CVD) Dielectric

- CVD Tungsten

- Physical Vapor Deposition (PVD)

- Chamber Cleaning

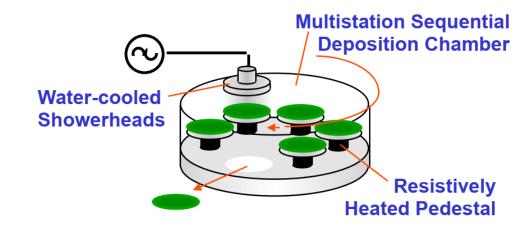

### THIN FILMS - CVD

- Chemical Vapor Deposition (CVD) thermally reacts gases to deposit films.

- CVD can be performed over a variety of temperatures from around 400°C on the low end to over 1,200°C on the high end.

- CVD films can be deposited over a variety of different material layers.

- Compared to oxidation, CVD films can be deposited at lower temperatures, can be deposited over material layers other than silicon and do not consume any of the underlying substrate material the way oxidation does.

- CVD can deposit a wide variety of Insulating, Conducting and Semiconducting films.

### THIN FILMS – CVD DIELECTRIC

TEOS Source

#### **Chemical Reactions**

$Si(OC_2H_5)_4 + 9O_3 \rightarrow SiO_2 + 5CO + 3CO_2 + 10H_2O$

**Process Conditions (ILD)**

Flow Rate: 100 to 300 sccm

Pressure: 50 Torr to Atmospheric

#### **CVD Dielectric**

$O_2$

$O_3$

TEOS \*

TMP \*

## THIN FILMS – CVD TUNGSTEN

#### **Chemical Reactions**

$WF_6 + 3 H_2 \rightarrow W + 6 HF$

#### **Process Conditions**

Flow Rate: 100 to 300 sccm

Pressure: 100 mTorr

Temperature: 400 degrees C.

#### **CVD Dielectric**

WF<sub>6</sub> \*

Ar

$H_2$

$N_2$

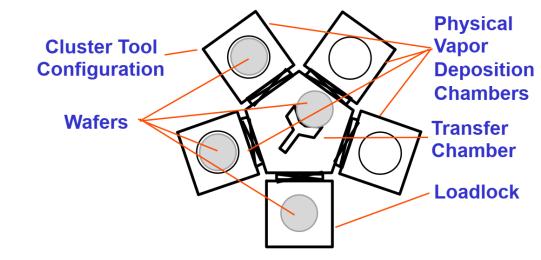

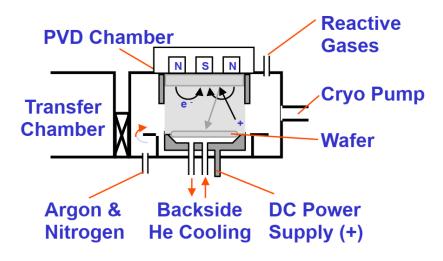

### THIN FILMS - PVD

#### **Process Conditions**

Pressure: < 5 mTorr

Temperature: 200 degrees C.

RF Power:

#### **Barrier Metals**

SiH<sub>4</sub> Ar N<sub>2</sub> N<sub>2</sub>

Ti PVD Targets \*

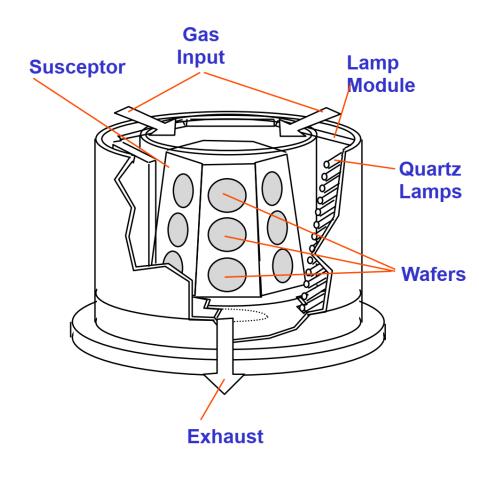

## THIN FILMS – EPITAXIAL SILICON DEPOSITION

#### **Chemical Reactions**

Silicon Deposition:  $HSiCl_3 + H_2 \rightarrow Si + 3 HCl$

#### **Process Conditions**

Flow Rates: 5 to 50 liters/min

Temperature: 900 to 1,100 degrees C. Pressure: 100 Torr to Atmospheric

#### **Silicon Sources**

SiH<sub>4</sub> H<sub>2</sub>SiCl<sub>2</sub> HSiCl<sub>3</sub> \* SiCl<sub>4</sub> \*

#### **Dopants**

$AsH_3$   $B_2H_6$   $PH_3$

#### Etchant HCl

**Carriers**

Ar H<sub>2</sub> \*

$N_2$

<sup>\*</sup> High proportion of the total product use

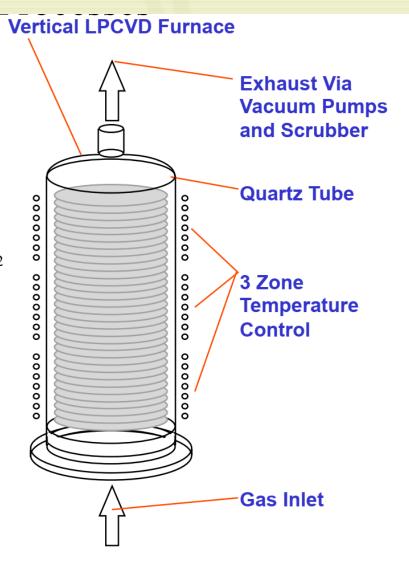

## FRONT-END PROCESSES

- Thermal Oxidation

- Silicon Nitride Deposition

- Low Pressure Chemical Vapor Deposition (LPCVD)

- Polysilicon Deposition

- Low Pressure Chemical Vapor Deposition (LPCVD)

- Annealing

## FRONT-END PROCESSES

#### **Chemical Reactions**

Thermal Oxidation:  $Si + O_2 \rightarrow SiO_2$

Nitride Deposition:  $3 \text{ SiH}_4 + 4 \text{ NH}_3 \rightarrow \text{Si}_3 \text{N}_4 + 12 \text{ H}_2$

Polysilicon Deposition:  $SiH_4 \rightarrow Si + 2 H_2$

#### **Process Conditions (Silicon Nitride LPCVD)**

Flow Rates: 10 - 300 sccm

Temperature: 600 degrees C.

Pressure: 100 mTorr

Dichloroethene \*

| Oxidation                | Polysilicon        | Nitride                            | Annealing      |

|--------------------------|--------------------|------------------------------------|----------------|

| Ar                       | $\mathrm{H_2}$     | NH <sub>3</sub> *                  | Ar             |

| $N_2$                    | $N_2$              | H <sub>2</sub> SiCl <sub>2</sub> * | He             |

| $H_2^{-}O$               | SiH <sub>4</sub> * | $N_2$                              | $\mathrm{H}_2$ |

| $\overline{\text{Cl}_2}$ | $AsH_3$            | SiH <sub>4</sub> *                 | $N_2$          |

| $H_2$                    | $B_2H_6$           | $SiCl_4$                           |                |

| HC1 *                    | $PH_3$             | ·                                  |                |

<sup>\*</sup> High proportion of the total product use

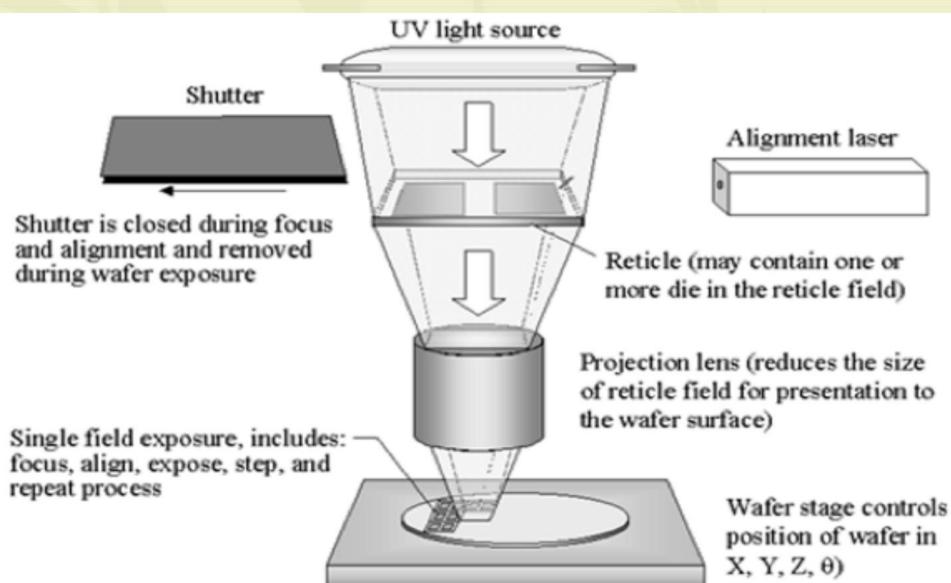

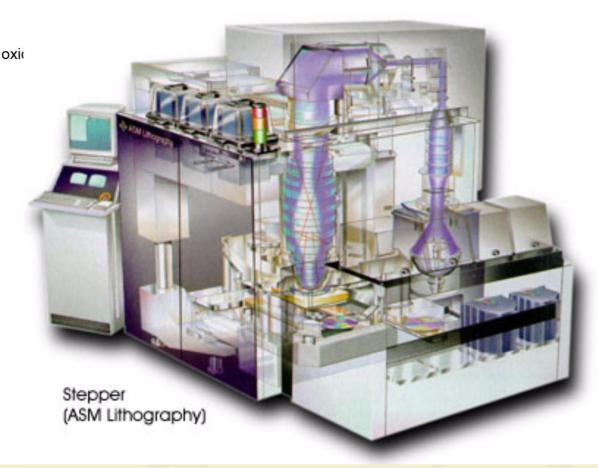

## **PHOTOLITHOGRAPHY**

- Photoresist Coating Processes

- Exposure Processes

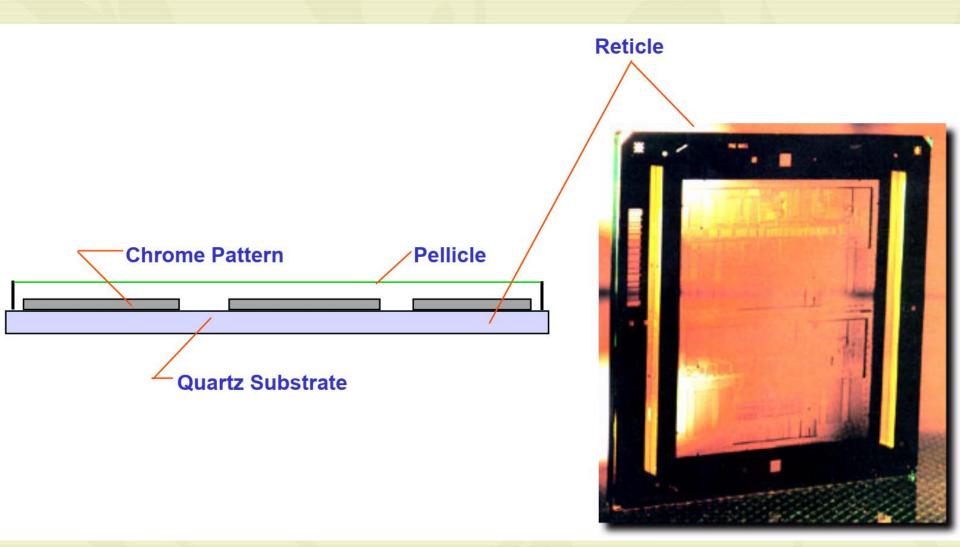

# PHOTOLITHOGRAPHY – ALIGNMENT & EXPOSURE

## PHOTOLITHOGRAPHY – Lithography Pattern Preparation

## **PHOTOLITHOGRAPHY**

#### Applying Photo Resist -

scale: wafer level (~300mm / 12 inch)

The liquid (blue here) that's poured

onto the wafer while it spins is a photo

resist finish similar as the one known

from film photography. The wafer

spins during this step to allow very

thin and even application of this photo

resist layer.

#### Exposure -

scale: wafer level (~300mm / 12 inch)

The photo resist finish is exposed to ultra violet (UV) light. The chemical reaction triggered by that process step is similar to what happens to film material in a film camera the moment you press the shutter button. The photo resist finish that's exposed to UV light will become soluble. The exposure is done using masks that act like stencils in this process step. When used with UV light, masks create the various circuit patterns on each layer of the microprocessor. A lens (middle) reduces the mask's image. So what gets printed on the wafer is typically four times smaller linearly than the mask's pattern.

#### Exposure -

scale: transistor level (~50-200nm)

Although usually hundreds of microprocessors are built on a single wafer, this picture story will only focus on a small piece of a microprocessor from now on – on a transistor or parts thereof. A transistor acts as a switch, controlling the flow of electrical current in a computer chip. Intel researchers have developed transistors so small that about 30 million of them could fit on the head of a pin.

## PHOTOLITHOGRAPHY - Photoresist Coating Processes

#### **Photoresists**

Negative Photoresist \*

Positive Photoresist \*

#### **Other Ancillary Materials (Liquids)**

Edge Bead Removers \*

Anti-Reflective Coatings \*

Adhesion Promoters/Primers (HMDS) \*

Rinsers/Thinners/Corrosion Inhibitors \*

Contrast Enhancement Materials \*

#### **Developers**

TMAH \*

Specialty Developers \*

#### **Inert Gases**

Ar

$N_2$

# PHOTOLITHOGRAPHY – EXPOSURE PROCESSES

$Kr + F_2 (gas) *$

#### **Inert Gases**

$N_2$

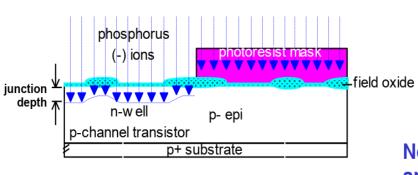

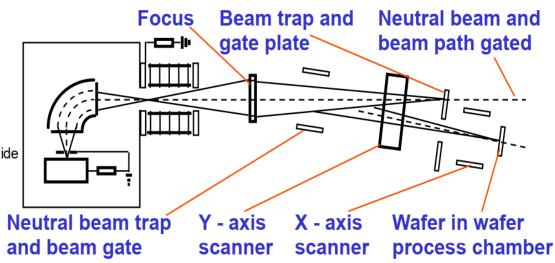

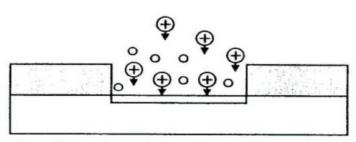

## **ION IMPLANTATION**

- Well Implants

- Channel Implants

- Source/Drain Implants

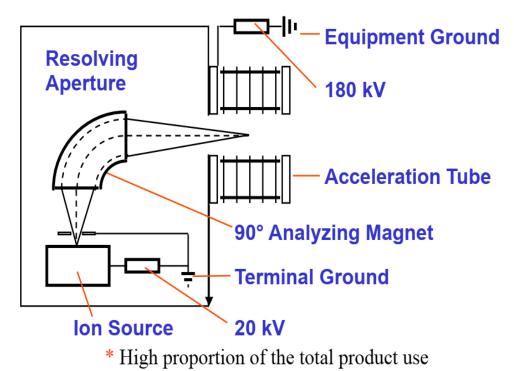

## Ion Implantation

#### **Process Conditions**

Flow Rate: 5 sccm Pressure: 10<sup>-5</sup> Torr

Accelerating Voltage: 5 to 200 keV

| Gases            | <b>Solids</b> |

|------------------|---------------|

| Ar               | Ga            |

| $AsH_3$          | In            |

| $B^{11}F_3^*$    | Sb            |

| He               | Liquids       |

| $N_2$            | $Al(CH_3)_3$  |

| $PH_3$           |               |

| $SiH_4$          |               |

| $\mathrm{SiF}_4$ |               |

| $GeH_4$          |               |

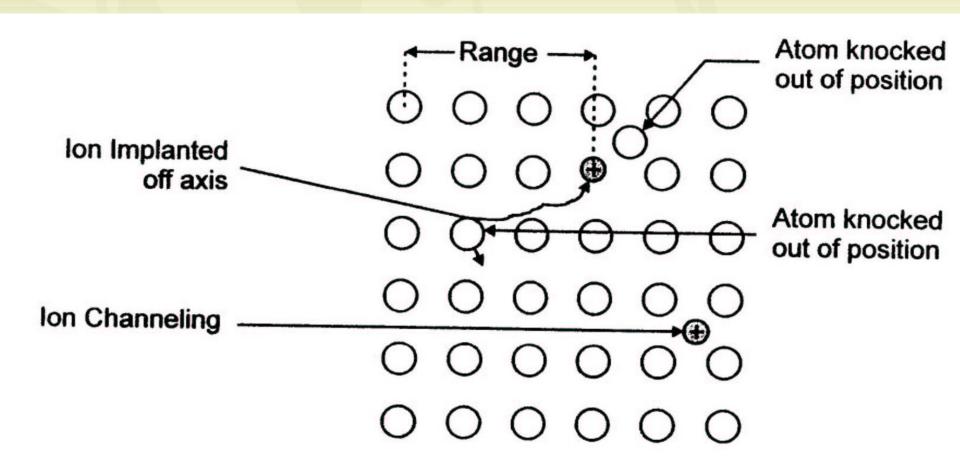

## ION IMPLANTATION – Implanted Ion Path

#### **Typical Values**

| Deep Retrograde Well | = 8 | 800-1000 KcV or 1-3 x 10 <sup>13</sup> ions/cm <sup>3</sup> |

|----------------------|-----|-------------------------------------------------------------|

| N-Well               | =   | 200 KeV or $1 \times 10^{13}$ ions/cm <sup>3</sup>          |

| Source-Drain         | =   | 30 KeV or 3-5 x 1015 ions/cm3                               |

| <b>Buried Layer</b>  | =   | 80-100 KeV or 1-5 x 10 <sup>15</sup> ions/cm <sup>3</sup>   |

| Resistors            | _   | 50 KeV or 1-10 x 1013 ions/cm                               |

## ION IMPLANTATION

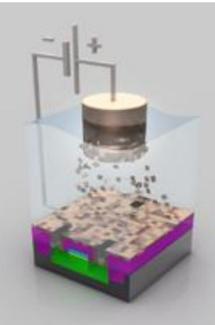

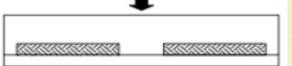

## Applying Photo Resist - scale: transistor level (~50-200nm)

implanted.

There's photo resist (blue color) applied, exposed and exposed photo resist is being washed off before the next step. The photo resist will protect

material that should not get ions

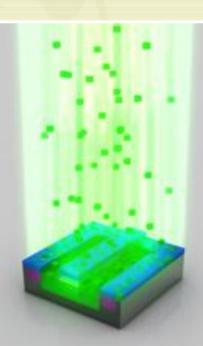

#### Ion Implantation -

scale: transistor level (~50-200nm)

Through a process called ion implantation (one form of a process called doping), the exposed areas of the silicon wafer are bombarded with various chemical impurities called lons. Ions are implanted in the silicon wafer to alter the way silicon in these areas conducts electricity. Ions are shot onto the surface of the wafer at very high speed. An electrical field accelerates the ions to a speed of over 300,000 km/h (~185,000 mph)

#### Removing Photo Resist -

scale: transistor level (~50-200nm)

After the ion implantation the photo resist will be removed and the material that should have been doped (green) has alien atoms implanted now (notice slight variations in color)

## **ETCHING**

- Conductor Etch

- Poly Etch and Silicon Trench Etch

- Metal Etch

- Dielectric Etch

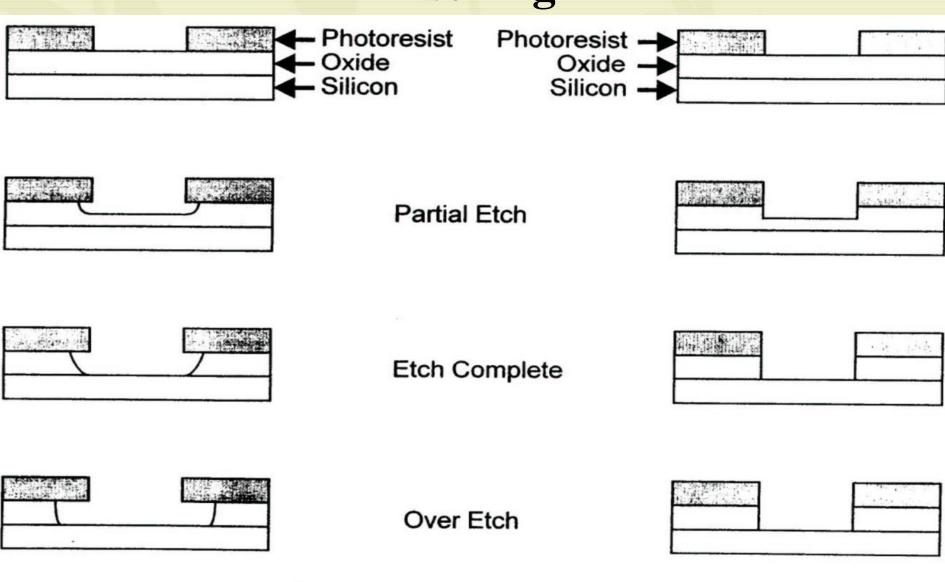

## ETCHING - ETCHING TERMINOLOGY

- Isotropic Etching Etching which is not directional. The etchant etches down and sideways at the same rate. Most wet etches are Isotropic.

- Anisotropic Etching Etching which proceeds faster in one direction than in other directions, i.e., a directional etch. Some plasma and ion beam etches are directional.

- Selectivity The relative etch rate for an etchant for one material versus another material. For example, hydrofluoric acid etches oxide but not silicon; hydrofluoric acid, therefore, has a high selectivity for oxide over silicon.

## **ETCHING**

Washing off of Photo Resist – scale: transistor level (~50-200nm)

The gooey photo resist is completely dissolved by a solvent. This reveals a pattern of photo resist made by the mask.

Etching – scale: transistor level (~50-200nm)

The photo resist is protecting material that should not be etched away. Revealed material will be etched away with chemicals.

Removing Photo Resist – scale: transistor level (~50-200nm)

After the etching the photo resist is removed and the desired shape becomes visible.

# ETCHING – Isotropic Versus Anisotropic Etching

Isotropic Etch Anisotropic Etch

## ETCHING – Anisotropic Etch Mechanisms

lon bombardment creates a surface damage layer.

Chemical etchants - etch away the damage layer, ion bombardment creates a new damage layer.

Damage Layer

Inhibitor covers the whole surface inhibiting etching.

Ion bombardment removes the inhibitor from the bottom of the exposed area.

Chemical etchants - etch the area where the inhibitor has been removed by ion bombardment

#### Inhibitor

## **CLEANING**

- Critical Cleaning

- Photoresist Strips

- Pre-Deposition Cleans

## CRITICAL CLEANING

3

المنافقة المنافقة

#### **Process Conditions**

Temperature: Piranha Strip is 180 degrees C.

H<sub>2</sub>O Rinse

#### **RCA Clean**

SC1 Clean

$$(H_2O + NH_4OH + H_2O_2)$$

\*

\* SC2 Clean  $(H_2O + HCl + H_2O_2)$  \*

#### Piranha Strip

\*  $H_2SO_4 + H_2O_2$  \*

#### **Nitride Strip**

$$HF + H_2O^*$$

#### **Dry Strip**

$$N_2O$$

$O_2$

$CF_4 + O_2$

#### **Solvent Cleans**

NMP

Proprietary Amines (liquid)

Dry Cleans

HF

O<sub>2</sub> Plasma

Alcohol + O<sub>3</sub>

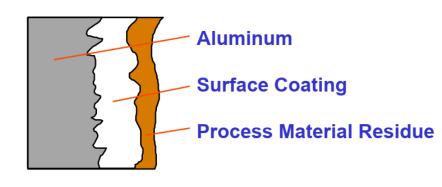

## **CLEANING**

## **Chamber Cleaning**

#### **Chemical Reactions**

Oxide Etch:  $SiO_2 + C_2F_6 \rightarrow SiF_4 + CO_2 + CF_4 + 2 CO$

#### **Process Conditions**

Flow Rates: 10 to 300 sccm Pressure: 10 to 100 mTorr RF Power: 100 to 200 Watts

#### **Chamber Cleaning**

C<sub>2</sub>F<sub>6</sub> \* NF<sub>3</sub> ClF<sub>3</sub>

**Chamber Wall Cross-Section**

## **PLANARIZATION**

- Electroplating

- Oxide planarization

- Metal Planarization

## **METAL DEPOSITION**

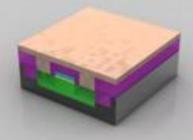

#### Ready Transistor -

scale: transistor level (~50-200nm)

This transistor is close to being finished. Three holes have been etched into the insulation layer (magenta color) above the transistor. These three holes will be filled with copper which will make up the connections to other transistors.

#### Electroplating -

scale: transistor level (~50-200nm)

The wafers are put into a copper sulphate solution as this stage. The copper ions are deposited onto the transistor thru a process called electroplating. The copper ions travel from the positive terminal (anode) to the negative terminal (cathode) which is represented by the wafer.

#### After Electroplating -

scale: transistor level (~50-200nm)

On the wafer surface the copper ions settle as a thin layer of copper.

## **METAL LAYERS**

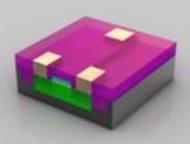

**Polishing** - scale: transistor level (~50-200nm) The excess material is polished off.

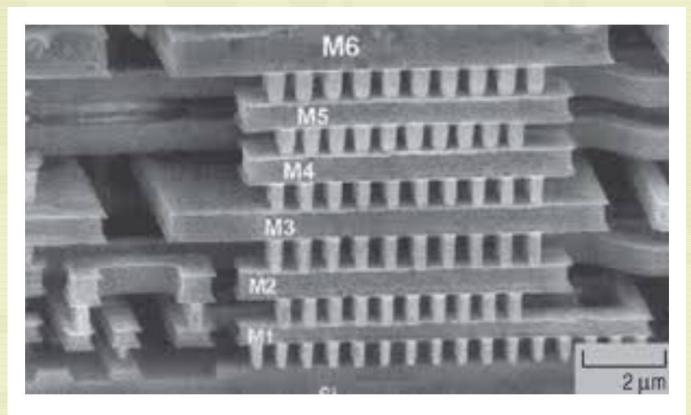

Metal Layers – scale: transistor level (six transistors combined ~500nm)

Multiple metal layers are created to interconnect (think: wires) in between the various transistors. How these connections have to be "wired" is determined by the architecture and design teams that develop the functionality of the respective processor (e.g. Intel® Core™ i7 Processor ). While computer chips look extremely flat, they may actually have over 20 layers to form complex circuitry. If you look at a magnified view of a chip, you will see an intricate network of circuit lines and transistors that look like a futuristic, multi-layered highway system.

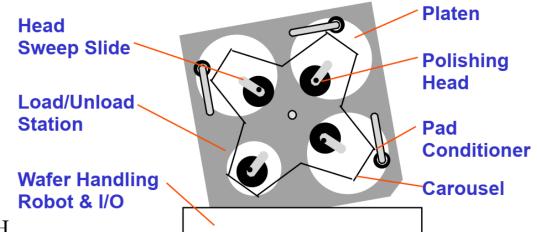

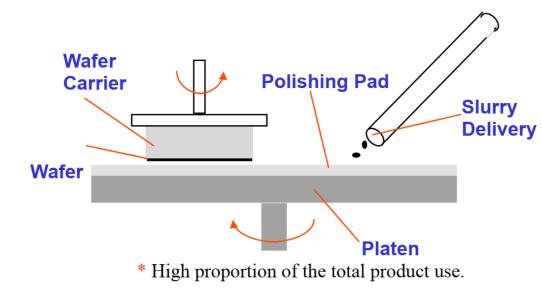

## Chemical Mechanical Planarization (CMP)

#### **Process Conditions (Oxide)**

Flow: 250 to 1000 ml/min Particle Size: 100 to 250 nm

Concentration: 10 to 15%, 10.5 to 11.3 pH

#### **Process Conditions (Metal)**

Flow: 50 to 100 ml/min

Particle Size: 180 to 280 nm

Concentration: 3 to 7%, 4.1 - 4.4 pH

#### **Backing (Carrier) Film**

Polyurethane

#### **Pad**

Polyurethane

#### **Pad Conditioner**

Abrasive

#### CMP (Oxide)

Silica Slurry \*

KOH \*

$NH_4OH$

H<sub>2</sub>O

#### CMP (Metal)

Alumina \* FeNO<sub>3</sub>

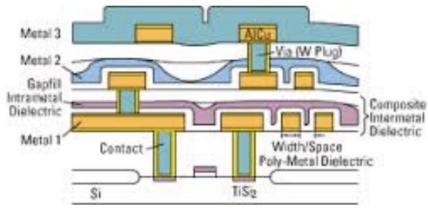

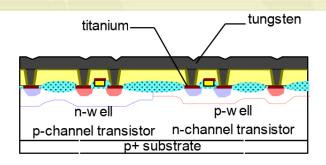

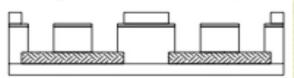

### **METALLIZATION**

#### Traditional Interconnect Flow

Cap ILD layer and CMP

Oxide Via-2 etch

Tungsten deposition + CMP

Metal-2 deposition + etch

#### Dual Damascene Flow

Cap ILD layer and CMP

Nitride etch-stop layer (patterned and etched)

Second ILD layer deposition and etch through two oxide layers

Copper fill

Copper CMP

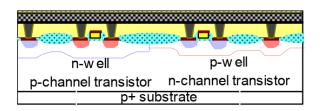

## **Example CMOS process flow**