PAPER

INVITED

# Magnetoresistive Random Access Memory

Magnetoresistive random access memory (MRAM) and particularly spin-transfer-torque MRAM is a nonvolatile memory with very high endurance and scalability. It is based on an array of magnetic tunnel junctions with magnetoresistive readout of the state of device and uses spin-transfer torque to efficiently rewrite the memory.

By DMYTRO APALKOV, BERNARD DIENY, Fellow IEEE, AND J. M. SLAUGHTER

ABSTRACT | In this paper, a review of the developments in MRAM technology over the past 20 years is presented. The various MRAM generations are described with a particular focus on spin-transfer torque MRAM (STT-MRAM) which is currently receiving the greatest attention. The working principles of these various MRAM generations, the status of their developments, and demonstrations of working circuits, including already commercialized MRAM products, are discussed.

**KEYWORDS** | Magnetic tunnel junctions (MTJs); MRAM; spin electronics; spin-transfer torque (STT); spintronics; STT-MRAM; thermally assisted MRAM; toggle; tunnel magnetoresistance

# I. INTRODUCTION TO MRAM TECHNOLOGY

Magnetoresistive random access memory (MRAM) is a class of solid-state storage circuits that store data as stable magnetic states of magnetoresistive devices, and read data by measuring the resistance of the devices to determine their magnetic states. In practice, the magnetoresistive devices are integrated with complementary metal–oxide– semiconductor (CMOS) circuitry to make chips that are compatible with mass-produced semiconductor electronics. Such circuits have been designed around a variety of magnetoresistive devices, but commercially-produced MRAM products, and the vast majority of MRAM technologies being developed for future commercial MRAM technologies,

Digital Object Identifier: 10.1109/JPROC.2016.2590142

are based on magnetic tunnel junction (MTJ) devices. All of these circuits are resistive memories in terms of the read operation; it is the method of writing the magnetic state that sets apart the different types of MRAM technology. Some of the heavily studied write methods include Stoner–Wolfarthtype field switching, Savtchenko switching (also a fieldswitching method), spin-torque switching, and thermally assisted switching (heat with field or spin torque). Two methods have so far been commercialized: toggle MRAM, which uses Savtchenko switching [1], has been in mass production since 2006, [2] and spin-torque switched MRAM is in the early stages commercial production [3].

Advances in MRAM technology have been closely linked with advances in the understanding of magnetic and magnetotransport properties of ultrathin films, including: tunneling magnetoresistance (TMR), MgO-based MTJ materials for giant TMR, synthetic antiferromagnet (SAF) structures, interfacial perpendicular magnetic anisotropy (PMA), and spin-transfer torque (STT). The application of scientific discovery to commercial technology seen in this field is striking in its breadth and speed of adoption. In this paper, we review the major developments that are driving accelerating interest and adoption of MRAM, key considerations for functionality and scaling to higher densities, and the status of the major technology types.

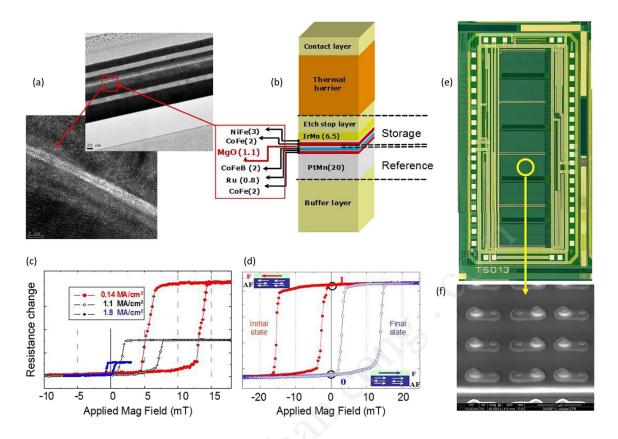

# A. MTJ Devices for MRAM

Fig. 1 shows the most basic MTJ structure, two ferromagnetic layers separated by a dielectric spacer layer, the tunnel barrier. When the tunnel barrier is very thin, typically < 2 nm, quantum mechanical tunneling of electrons through the barrier makes the MTJ behave like a resistor having a resistance that depends exponentially on the barrier thickness and is proportional to the inverse of the in-plane barrier area. The tunneling current is spin republication/redistribution requires IEEE permission

0018-9219 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received December 7, 2015; revised May 29, 2016; accepted July 3, 2016. Date of publication August 29, 2016; date of current version September 16, 2016. **D. Apalkov** is with the Semiconductor R&D Center, Samsung Electronics, San Jose, CA 95134 USA.

**B. Dieny** is with SPINTEC, Grenoble Alpes University, CEA, CNRS, CEA/Grenoble, INAC, Grenoble, France (e-mail: bernard.dieny@cea.fr).

J. M. Slaughter is with Everspin Technologies, Inc., Chandler, AZ 85224 USA.

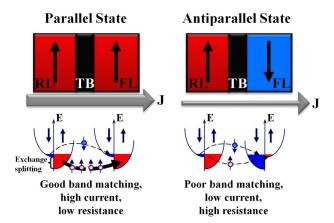

Fig. 1. Sketch of a MTJ: two ferromagnetic layers (in red/blue) typically made of CoFe-based alloys separated by a tunnel barrier (black) most often made of MgO about 1 nm thick. Explanation of the TMR effect: parallel state has good band matching and low resistance, whereas antiparallel state has poor band matching: either absence of available carriers of a given spin or inadequacy of available states in the receiving electrode.

polarized, due to the asymmetric band structure of the ferromagnetic electrodes, giving rise to the TMR as shown in Fig. 1. The relative orientation of the magnetizations in these two layers determines the resistance of the MTJ device. For most materials, the resistance is low when the magnetizations of the two layers are parallel, because the majority band electrons can tunnel into the majority band on the opposite side of the barrier. When the orientation is antiparallel, the resistance is high since the majority band electrons have to tunnel into the minority band of the opposite electrode.

The simplest possible STT-MRAM design has the following components:

- free layer (FL);

- tunnel barrier (TB);

- reference layer (RL).

The free layer, sometimes called the recording layer or the storage layer, is the ferromagnetic layer retaining the stored information. This layer is often made of CoFeB material of different compositions [4]. The tunnel barrier is a thin (around 1 nm) insulating nonmagnetic layer that provides means to switch and read the state of the free layer with a spin-polarized tunneling current. In the past ten years, MgO tunneling barriers have been most heavily studied due to the giant TMR effect, though other materials, such as AlOx, and TiO, have been used [5] and AlOx is used in production toggle MRAM. The other magnetic layer-the reference layer-provides a stable reference magnetization direction for the FL reading and switching. This layer is designed to have magnetic anisotropy much higher than the FL so that it never switches during memory operation.

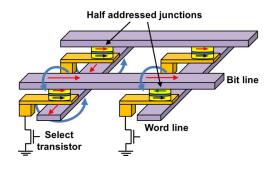

Fig. 2. Sketch of the organization of field-written MRAM. Each cell comprises an MTJ connected in series with a select transistor.

Although multibit concepts exist, the MTJ devices that have been demonstrated in practical MRAM circuits have two stable magnetic states that store one bit of data as a parallel/antiparallel magnetic state with a low/high resistance as described above. To achieve this, such a magnetic device has a free layer engineered to have a uniaxial magnetic anisotropy, so that the magnetization tends to lie along an easy axis in one or the other direction. Since the magnetization of ordinary ferromagnetic thin films is constrained to be in the film plane by the thin-film shape anisotropy, the in-plane easy axis is created mainly by patterning the free layer into a shape with a long direction (easy axis) and a short direction (hard axis). The intrinsic anisotropy of the material may also contribute to the total uniaxial anisotropy. On the other hand, devices having their easy axis perpendicular to the film plane can have a number of advantages, discussed further in the sections that follow. A free layer engineered to have a perpendicular easy axis has stable states with the magnetization either up or down, with respect to a horizontal film plane, and the in-plane directions are hard. Such layers employ materials having a strong perpendicular anisotropy that can overcome the thin-film shape anisotropy, also discussed below. For any of these devices, the stability of the stored data over time and temperature is determined by the energy barrier between the two stable magnetic states, which is in turn related to the strength of the uniaxial anisotropy and the volume of magnetic material involved in the reversal process.

To create a memory array from MTJ devices, each device is typically integrated with an isolation transistor (see Fig. 2) that can be turned on to pass a current selectively through the MTJ devices of interest, such as during the read operation. For spin-torque MRAM, the same transistor is used to pass the switching current through the target MTJ devices. Since each memory cell typically has one transistor and one MTJ, this particular architecture is known as the 1T-1MTJ MRAM architecture. Other architectures have been proposed and evaluated for various purposes, but the 1T-1MTJ cell is the most commonly used.

#### **B.** Overview of MRAM Technology Generations

MRAM technology can be classified by the switching method employed to write data. First-generation MRAM is generally understood to include methods using magnetic fields to program the array. Toggle MRAM is the only first-generation MRAM in mass production [2], [6], [7]. A strong advantage of field switching is unlimited write endurance, since reversing the free-layer magnetization with a magnetic field does not create any wearout effects. A disadvantage is the difficulty in scaling to smaller cell sizes, due to several factors including the magnitude of the required switching currents and the somewhat complex memory cell geometry. A detailed discussion of this technology is presented in the section on field-switched MRAM.

Second-generation MRAM uses STT to program the array. STT switching can be accomplished with reasonable efficiency with MTJ devices having either in-plane or perpendicular-to-the-plane magnetization. STT-MRAM with in-plane devices began commercial production in 2015 with a 64-Mb product [3] and is expected to ramp to volume production in 2016 with a 256-Mb product [8]. STT-MRAM with perpendicular MTJ devices is under intensive development at a number of companies around the world. A discussion of technology demonstration vehicles, the fundamentals of the technology, and relative advantages/disadvantages is presented in several sections below.

A number of physical phenomena are under investigation for use in third-generation MRAM, including: voltage-controlled anisotropy (VCA), voltage-controlled magnetism (VCM) [9]-[12], spin Hall effect (SHE), and spin-orbit torque switching (SOT) [13]-[17]. The potential for improved MRAM scaling and performance comes from idea that switching could be accomplished while passing little or no electrical current through the MTJ device. However, each effect has challenges to overcome for use in practical MRAM circuits. Some examples of those challenges are as follows. VCA does not directly lead to deterministic switching between two stable states, but is more likely to be applied in combination with another innovation for use in an MRAM array. Reliability issues like wear-out and parameter drift need to be better understood for practical VCM devices. SHE does not lend itself to efficient switching in devices with perpendicular magnetization, and SOT appears to require innovation in materials to increase the magnitude of the effect for improved switching efficiency. In many cases, these new devices would need to be deployed in a three-terminal cell configuration that is not compatible with high-density memory arrays. Nonetheless, the possibility of switching with little or no charge current passing through the tunnel barrier is stimulating a growing interest and investment due to the potential for use in low-power circuits and high-endurance applications.

# II. MAJOR ADVANCEMENTS THAT ENABLED MRAM AND STIMULATED COMMERCIAL DEVELOPMENT

#### A. Tunneling Magnetoresistance

The development of MTJ material with high roomtemperature magnetoresistance ratio MR  $\sim 10\%$ , reported in 1995 [18], [19] offered a much improved read signal for MRAM technology. This major development in TMR was followed by intensive work around the world that resulted in dramatic improvements in the techniques and materials, so that record TMR values have increased steadily, most markedly with the development of MgO tunnel barriers [4], [20], [21] to over 600% [22]. In addition to having a high magnetoresistance, MTJ materials also provide the ability to match the resistance of the storage device to that of the CMOS transistors used in the circuitry. This capability is essential to the technology since the transistors used in the MRAM read circuit result in a series resistance, typically in the  $k\Omega$ range, that reduces the relative resistance change at the point of sensing. The giant magnetoresistance (GMR) and anisotropic magnetoresistance (AMR) devices, which were available prior to practical MTJ devices, are inherently low resistance since they are metallic and therefore not well suited to integration with CMOS circuitry.

The promise of practical, high-TMR, materials motivated new MRAM R&D programs around the world, leading to the first commercial product [2], [23] approximately 11 years after the initial discovery [18], [19]. These materials also had a large positive impact on the hard disk drive (HDD) industry where MTJs were quickly commercialized for improved read sensors. Although the detailed requirements for MTJ devices in read sensors are quite different from the MRAM case, there is no doubt that the huge development effort in MTJ materials for HDD readers greatly accelerated the progress in MTJ materials for MRAM.

# B. Synthetic Antiferromagnet (SAF) Structures and Their Application to MRAM

The discovery and intense study of oscillatory magnetic coupling (RKKY coupling) in synthetic layered structures, in the 1980s, showed that it was possible to engineer thin-film structures with separate ferromagnetic layers that are coupled either ferromagnetically or antiferromagnetically to each other through a nonmagnetic spacer layer separating them, with a coupling strength and sign determined by the thickness of the spacer [25]. This understanding led to the use of synthetic antiferromagnet (SAF) structures engineered to provide the required magnetic properties for both reference magnetic layers and free layers in MTJ devices for MRAM. Almost all MTJ devices for MRAM use a SAF for the reference layer. A SAF reference layer has strong antiferromagnetic (AF) coupling between ferromagnetic (FM) layers of

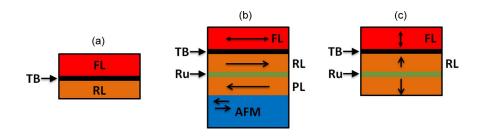

Fig. 3. (a) Simplest MTJ design. (b) Typical in-plane MTJ with a synthetic antiferromagnetic reference layer pinned by an antiferromagnetic (AFM) pinning layer. (c) Perpendicular MTJ with synthetic antiferromagnetic reference layer.

nearly equal magnetic moment, resulting in a magnetically rigid system. When used as a free layer, the spacer layer thickness is set for weaker AF coupling to make a less rigid structure that is more responsive to applied magnetic fields as described further in sections that follow.

The simplest design of an MTJ is represented in Fig. 3(a). It exhibits tunnel magnetoresistance. However it has undesired magnetostatic interactions between the RL and the FL, which tend to bias the FL toward the antiparallel (AP) state (for in-plane magnetization).

A typical in-plane MTJ with a SAF reference structure is illustrated in Fig. 3(b). In this example, the pinned layer of the SAF (PL) is pinned in a specific direction by direct contact with an underlying antiferromagnetic (AFM) material, and the reference layer of the SAF (RL) is in contact with the tunnel barrier providing the reference direction for the MTJ. The SAF performs two major functions: it provides a stable magnetic reference direction since its low net moment is less affected by external fields than a single ferromagnetic layer, and the imbalance of magnetic moment between the two layers can be easily adjusted to provide a negative dipolar field that cancels the positive interlayer coupling between the reference layer and the free layer [26]. The interlayer coupling can include Neel coupling, due to magnetic poles created by correlated roughness at the surfaces of the layers [27], and an electron-mediated coupling associated with the polarized electrons tunneling through the barrier, both of which favor ferromagnetic alignment of the reference and free layers. A typical MTJ with perpendicularly magnetized SAF and free layer is shown in Fig. 3(c). The same principles apply in this geometry although, due to the extremely high anisotropies achievable with engineered perpendicular materials, the pinning AFM layer is not necessary.

A SAF structure for the free layer serves a different purpose and has very different design requirements compared to a SAF reference structure. The main use of a SAF free layer is to enable the Savtchenko switching technique used in toggle MRAM, which is described further in the section below.

#### C. Savtchenko Switching

Writing data into a memory array requires the ability to select the storage devices to be written within a large array of such devices, switch those target devices with extremely high reliability, and leave all other devices unaffected with extremely high reliability. For fieldswitched MRAM, this proved to be a significant challenge [26]. The basic idea of field switching is to use rows and columns of write lines, placed under and over the MTJ devices, that create magnetic fields large enough to reverse the free layer magnetization for the devices located at the cross point where both a row and column line are energized (see Fig. 2). The fundamental problem with this approach is that all of the nontarget bits along the energized lines also see a field that, although smaller in magnitude, causes a nonnegligible probability of switching those half-selected bits. This is known as the "half-select problem."

The half-select problem for field switching was solved with the invention of Savtchenko switching [1], which cleverly employs a SAF free layer and a sequence of write-current pulses that creates a rotating field to switch it. MRAM that uses Savtchenko switching is usually called "toggle MRAM" because the switching technique toggles the SAF free layer from one stable state to the other using the same write pulse sequence, as opposed to using different fields to write the high or low state. The first commercially produced MRAM product was a 4-Mb toggle MRAM which began production in 2006 by Freescale Semiconductor. That part and a family of products based on the same technology platform, now produced by Everspin Technologies, account for nearly all of MRAM production and sales today, with the remainder being Everspin's 64-Mb STT-MRAM product.

#### **D.** Spin-Torque Switching

The STT effect was theoretically predicted independently by Slonczewski [28] and Berger [29] in 1996. When a current is passed between two ferromagnetic layers separated by a nonmagnetic spacer, it exerts a torque on the magnetization of each of the layers. If the current is high enough, this can result in switching of the free layer. The first demonstration of STT-induced magnetization switching was done by Katine *et al.* using a spin valve device made from all-metal GMR stack in 2000 [30]. The first STT switching demonstration with MTJ devices was by Huai, *et al.* [5] in 2004 on AlOx-based tunneling junctions and 2005 on MgO-based MTJ [31]–[33].

# E. Interfacial Perpendicular Magnetic Anisotropy

Magnetic materials can exhibit magnetic anisotropy large enough to overcome the thin-film demagnetization energy and to pull the magnetization of the film out of plane. Many scientific studies in the late 1980s and early 1990s laid the foundations for rapid application of such materials in data storage and later in MRAM development. Perpendicular magnetization has been demonstrated in multilayered ultrathin films and superlattices having a ferromagnetic material layered with a nonmagnetic material, such as Au, Pt, or Pd [34]-[36], and for similar structures made from two different ferromagnetic materials, Co and Ni [37]. This perpendicular anisotropy can have several origins associated with spin-orbit interactions: electronic hybridization effects, interfacial strain, magnetocrystalline anisotropy, etc. A comprehensive survey of experimental studies on these materials can be found in reference [38].

In perpendicular MTJs, both the storage layer and the reference layer are magnetized out of plane [Fig. 3(c)]. For the reference layer, synthetic antiferromagnetic multilayers have become the preferred materials due to their strong and tunable perpendicular anisotropy energy and compatibility with fabrication techniques normally used for MTJ materials. As discussed above, practical use requires a SAF reference structure in MTJ devices for MRAM. Such SAF materials have been successfully and extensively developed and integrated into MgO-based pMTJ materials [39]–[41].

In addition to the SAF reference structure, pMTJ materials for MRAM also require a perpendicular free layer with soft magnetic properties that enable efficient spintorque switching between the two stable states (up and down). Of particular importance for STT-MRAM was the discovery that a quite strong perpendicular anisotropy exists at the interface between magnetic metal and oxides such as (Co/AlOx or CoFe(B)/MgO) [42], [43]. This anisotropy has been shown to result from hybridization effects between the transition metal (Co, Fe) dz<sup>2</sup> orbitals and the oxygen orbitals of the oxide tunnel barrier [44], [45]. In STT-MRAM, this strong interfacial anisotropy provides a good thermal stability of the free layer magnetization together with a sufficiently low write current as explained in Section VI.

Development of CoFeB-based free layers with first one MgO interface [43] and later two MgO interfaces [46], [47], combined with the multilayer-based perpendicular SAF materials, has led to practical pMTJ devices with the desired low switching current and high energy barrier needed for nonvolatile memory. STT-MRAM circuits and technology based on such pMTJ devices are in advanced development at a number of companies worldwide.

# III. DEMONSTRATIONS OF WORKING MRAM CIRCUITS

The major advancements described in the previous section have been successfully incorporated into a number of MRAM demonstration circuits and commercial products. Some notable demonstrations of working circuits are described below, illustrating the rapid progress in technology development over the past 15 years.

In 2000, Scheuerlein *et al.* reported the functionality of a field-switched MRAM circuit using AlOx-based MTJ devices and Stoner–Wolfarth-type writing circuits [48]. Basic read and write functionality were demonstrated in a 1-kb memory array with write pulses as short as 2.5 ns and with read operation as short as 10 ns, using a twincell read configuration.

Durlam *et al.* described the first Toggle MRAM circuit in 2003, a fully functional 4-Mb circuit with 1T1MTJ architecture and AlOx-based MTJ devices, demonstrating the effectiveness of Savtchenko writing to solve the problem of high write error rates due to the half-select in Stoner–Wolfarth-type field switching [49]. This circuit was designed to be a product, not simply a demonstration, with a unique local-bitline array architecture, a cell size of 1.55  $\mu$ m<sup>2</sup>, asynchronous 16-b SRAM interface compatibility, and demonstrated symmetric read and write cycle times of less than 25 ns [6]. This chip was introduced as a commercial product in 2006 and continues to be produced today by Everspin Technologies, Inc.

Significant results from several STT-MRAM demonstration circuits, all using MgO-based MTJ devices, have been published, beginning with a 4-kb test vehicle in 2005 [50] followed by many others including: a 2-Mb circuit and device data in 2007 [51], statistical data on 4-kb integrated arrays with  $70 \times 210 \text{ nm}^2$  b [52] and devices with perpendicular magnetization [53] in 2008, arrays integrated with 54-nm CMOS technology [54], 4-kb MRAM arrays with perpendicular bit switching in 2010 [55].

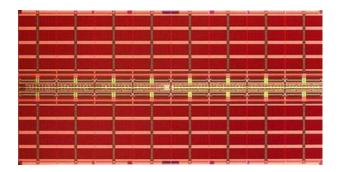

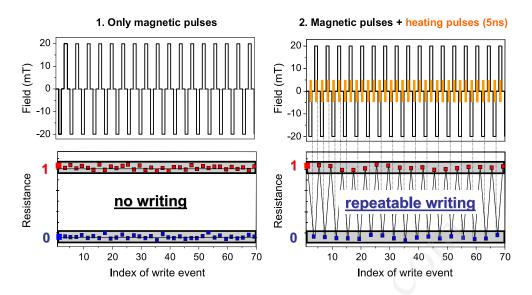

The first STT-MRAM product, announced in 2012, is a 64-Mb, DDR3, STT-MRAM circuit [3], [56]. Shown in Fig. 4, the chip is fabricated using in-plane MTJ devices in a 1T-1MTJ cell, integrated with 90-nm CMOS technology and packaged in a JEDEC standard DDR3 BGA. This chip is compatible with available DDR3 memory controllers and became commercially available from Everspin Technologies, Inc. in 2015.

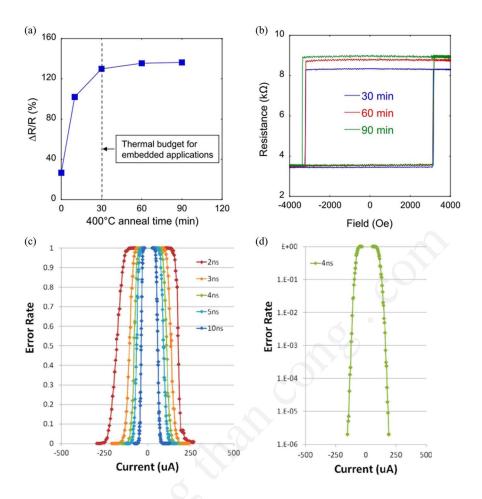

In 2014, Thomas *et al.* reported performance data for an 8-Mb STT-MRAM demonstration chip with high energy barrier for data retention compatible with

Fig. 4. Everspin Technologies' 64-Mb DDR3 STT-MRAM Die Photo. Word line drivers run vertically through the center of each of eight 8-Mb banks. Strips of column circuits run horizontally, dividing each bank into eight subarrays.

automotive applications and MTJ devices that are tolerant to high processing temperatures required for embedded memories [57]. Although CMOS circuitry is 90-nm technology, MTJ devices with diameter as small as 45 nm were used, demonstrating reliable switching with pulses as short as 2 ns in a 1T-1MTJ cell architecture.

The continuous improvement reported in these papers, and many others, reflects significant innovation and progress toward the use of spin-torque switching in a wider range of products, including standalone memories and embedded memory in a multiple applications.

# IV. REQUIREMENTS FOR RELIABLE READ IN AN ARRAY

The MTJ device should have a resistance in the  $k\Omega$  range to minimize the effect of the series resistance from the isolation transistor. This resistance typically leads to a tunnel barrier thickness on the order of 1 nm. The exponential thickness dependence of RA creates a challenge for producing MTJ material that is repeatable and uniform over the area of wafers used in semiconductor production. The issues of cross-wafer uniformity and wafer-to-wafer repeatability have largely been solved by the manufacturers of MTJ productions tools that are capable of < 1% uniformity and repeatability for these ultrathin films. However, array uniformity, which is a measurement of bit-to-bit resistance variation within a memory array, is a continuing challenge as device sizes are scaled ever smaller.

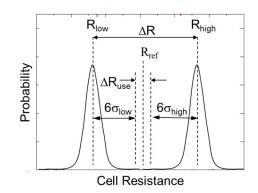

During the read operation, a typical read circuit compares the resistance of the bit to a reference resistance in order to determine if the bit is in the high or low state. Fig. 5 illustrates the effect of random resistance variations within an array on this type of read circuit. In the low state, bits with resistance on the high side of the distribution will fall closer to the reference than the average bit. Conversely, the bits on the low side of the distribution in the high resistance state will also be closer

Fig. 5. Schematic representation of Gaussian resistance distributions for a large array of MTJ cells in the low- and high-resistance states. A midpoint reference, represented here by  $R_{ref}$ , is generated by the read circuitry to evaluate the state of the MTJ device by comparing the measured resistance to  $R_{ref}$ . The average change in resistance from the low to high state is  $\Delta R$ , but the circuit must be capable of determining the resistance change for cells in the tails of the distributions, meaning the resistance change available to the circuit is  $\Delta R_{usc}$ .

to the reference. To have working memories with bit counts of megabit or more, the circuit must be able to correctly read the state of these bits in the tails of the distributions. If bits that are statistically separated  $5\sigma$  from the mean are unreadable, there will be approximately one bad bit in 2 Mb, a marginally unacceptable result requiring error correction.

A reasonable criterion for feasibility is  $6\sigma$  separation from the midpoint, or  $12\sigma$  separation between the mean high and low resistance states. Since the circuit must be able to correctly read the low  $6\sigma$  bits in the  $R_{\text{high}}$  distribution, and the high  $6\sigma$  bits in the  $R_{\text{low}}$  distribution, the usable resistance change for the circuit  $\Delta R_{\text{use}}$  is the difference between the midpoint reference and the  $6\sigma$  tails as illustrated in Fig. 5. A larger  $\Delta R_{\text{use}}$  allows a more aggressive circuit design with faster access time. It will make the read-out more robust, less sensitive to noise, and can be used for higher speed operation. To account for high-speed reading with normal process variations in the circuitry, significantly more than  $12\sigma$  is required. For example, toggle MRAM in production has demonstrated over  $20\sigma$  separation [49].

A number of factors can contribute to the width of the resistance distribution. Any variation in the bit area, e.g., due to lithography or etch variations, will directly cause variations in bit resistance. Process damage or veils created during the etch process also may contribute. However, it has been shown that the quality of the MTJ tunnel barrier itself can make a significant contribution to bit-to-bit resistance variation [23]. As the size (area) of MTJ devices is reduced, a given variation in the MTJ dimensions from the patterning process will create a larger relative bit-to-bit variation in the resistance. In addition, a given level of inhomogeneity in the tunnel barrier will result in a similar increasing relative variation with decreasing device size. As a result, maintaining a given level of separation in the resistance distributions for a robust midpoint read operation requires improvements in both the patterning process and the quality of the tunnel barrier.

For cases when separation between the high and low resistance distributions is not sufficient for reading with a midpoint reference scheme in a 1T-1MTJ architecture, other methods and/or cell architectures can be employed. A twin-cell architecture has two MTJ devices, in a 2T-2MTJ memory cell or in two adjacent 1MTJ cells, that are always written in opposite states to effectively double the resistance change. A circuit employing this cell was used to demonstrate high-speed MRAM read in one of the first MRAM demonstration circuits [48]. The tradeoff for the higher read performance is array area; twice as much area is needed for a given memory density.

Another method for mitigating the effect of wider distributions is the self-referenced read [58]-[62]. There are different techniques for self-referencing, but they all involve comparing the resistance of the MTJ in its initial state (stored data) to its resistance after being switched or rotated to a known state. For example, the resistance can be measured and stored, then compared to its resistance after a known switching pulse. Since the resistance of a device is compared to the same device in a different state, the bit-to-bit resistance distribution no longer plays a primary role. In another approach, based on big differences in resistance dependence on voltage in parallel and antiparallel states, two measurements are done at different voltage values and results are compared [63]. In all the self-referenced read schemes, the tradeoff for the tolerance to wide resistance distributions is longer time for the read operation, due to the extra pulse and the second read access time.

#### V. FIELD-WRITTEN TOGGLE MRAM

A memory array for field-written MRAM typically has rows and columns of copper lines above and below the MTJ devices that generate magnetic fields when current pulses are passed through the lines (see Fig. 2). Three key innovations that enable the successful commercialization of field-written MRAM are: Savtchenko switching for toggle MRAM operation, improvements in tunnel barrier quality and bit patterning fidelity for narrow and well-behaved bit-to-bit MTJ resistance distributions, and the process for cladding of the write lines. As described briefly in Section II-C and in more detail in the section on toggle MRAM below, Savtchenko switching solved the half-select problem through the use of a SAF free layer and timed write pulses. Another method of addressing the half-select problem, by using a combination of magnetic field and heat for thermal-assisted switching, is described in Section VII. The importance of narrow read

distributions is described in the preceding section and is important to all types of MRAM circuits.

Cladding involves the addition of permeable ferromagnetic material around three sides of a write line to focus the magnetic field toward the fourth side [64]. This produces a stronger field at the MTJ devices located near the fourth side, above or below the line, and minimizes the stray fields in other directions. The effect is to significantly reduce currents needed for the write operation and to suppress possible write errors due to stray fields experienced by rows or columns of bits adjacent to the row or column of bits to be written.

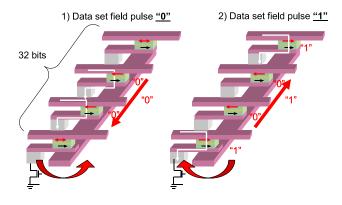

# A. Operating Principle of Toggle MRAM

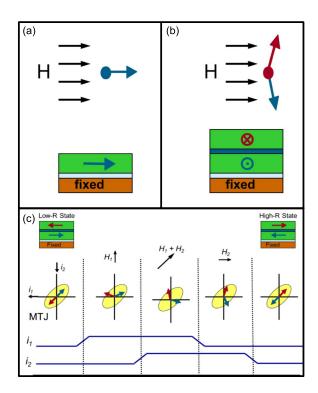

The use of Savtchenko switching in MRAM arrays provides a number of benefits including: low write error rates, reduced sensitivity to external fields, and a wide operating region for the write currents that reduces sensitivity to manufacturing process variations [7]. It relies on the unique behavior of a synthetic antiferromagnet (SAF) free layer, formed from two nearly identical ferromagnetic layers separated by a nonmagnetic coupling spacer layer. As shown schematically in Fig. 6(a) and (b), a single free layer responds to an external field by aligning with it, while the behavior of a SAF free layer is quite different. For a SAF having some net anisotropy  $H_k$ in each layer, there exists a critical spin flop field  $H_{sw}$  at which the two antiparallel layer magnetizations will rotate (flop) to be approximately orthogonal to the applied field H, with each layer scissoring slightly in the direction of *H* [65]. For fields  $H \ge H_{sw}$ , the SAF can lower its total energy by decreasing its dipole energy with a flop and scissor, even though the antiferromagnetic exchange energy is increased by the same scissoring. As the applied field strength is increased, the layers of the SAF will scissor further until they eventually become parallel and aligned with the field at the saturation field  $H_{\text{sat}}$ .

The programming pulse sequence and resulting response of the free layer are shown in Fig. 6(c). To toggle the bit from an initial "0" to a final "1," the currents  $i_1$ and  $i_2$  are pulsed with the timing indicated in the figure, such that the vector sum of the two magnetic fields effectively rotates through 90°. The SAF responds by orienting nominally orthogonal to this field and rotating with it such that, when  $i_2$  is turned off, the moments relax to their easy axis the magnetization of each layer now reversed. Because the TMR only depends on the direction of the layer that is in contact with the tunnel barrier, the resistance switches states each time the toggle pulse sequence is applied.

The toggle write mode requires that the memory circuit first determine the state of the target bit, and execute the toggle pulse sequence only if it is not in the desired state, i.e., only if the new data differ from the existing. If the preread determines that the target bit is already in the desired state for the new data, then that bit

**Fig. 6.** (a) A single layer of ferromagnetic material responds to an external field (H) by aligning with it, while the behavior of a SAF is quite different. A SAF free layer (b) rotates such that the moments of the layers are nearly orthogonal to H when the magnitude of H reaches the flop field of the SAF, with the moments canting to produce a net moment approximately parallel to the field. As the field strength is increased, the moments scissor toward each other until they are parallel when the SAF is saturated. (c) Schematic of a toggle MRAM bit with the field sequence used to switch the free layer from one state to the other. The fields H<sub>1</sub>, H<sub>1</sub> + H<sub>2</sub>, and H<sub>2</sub> are produced by passing currents i<sub>1</sub> and i<sub>2</sub>, through the write lines.

is not toggled. This approach increases the total write cycle time by adding a read operation, but has benefits in limiting the overall power consumption and improves array efficiency because the unipolar current allows the use of smaller transistors in the write drivers.

The elimination of the half-select problem can be understood by considering the energy barrier to reversal of bits experiencing a field from a single line (1/2-selected bits). For a SAF free layer, the single-line field raises the energy barrier of those bits, so that they are stabilized against reversal during the field pulse. This is in marked contrast to the conventional approach using a simple ferromagnetic layer for storage, where all of the 1/2-selected bits have their switching energy reduced and are therefore more susceptible to disturbance (thermal or external field).

# B. Performance of Toggle MRAM

A major feature of toggle MRAM is the essentially unlimited write endurance, since there is no wear-out

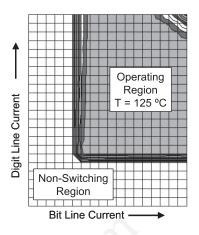

**Fig. 7.** Toggle switching map at elevated temperature (T = 125 °C) showing large operating region. Saturation of the free layer SAF exchange can start to be observed at over driven currents at the upper right in the figure. (From [68].)

mechanism related to switching the magnetization state of the free layer with magnetic fields. During the read operation, the bias applied to the MTJ is at a level far below the breakdown voltage of the device, but finite bias leads to a finite probability of eventual dielectric breakdown. For product reliability, two MTJ barrier failure modes must be controlled: time-dependent dielectric breakdown (TDDB) and resistance drift. Dielectric breakdown is an abrupt drop in resistance, or shorting, of the tunnel barrier, while resistance over time that can eventually lead to increased read error rates.

Many applications in industrial and automotive applications require consistent performance and robust reliability over a broad operating temperature range, typically -40 °C < T < 125 °C. Rigorous reliability analysis done for the Everspin 4Mb MRAM product showed that it exceeds the reliability requirements of industrial and automotive products [66]–[68]. Extensive operational characterization and accelerated stress testing validated its full functionality and high reliability in this environments. Fig. 7 demonstrates that the toggle switching operating region is maintained at the highest temperatures with more than ample margin.

In the operating region, it is possible to reliably read data and write to the array within the 35-ns read/write cycle time for this part. The large region with no switching errors is a demonstration of the ability of Savtchenko switching to eliminate half-select disturbs, even when the elevated temperature (125  $^{\circ}$ C) causes some reduction of the SAF coupling strength.

Everspin's commercial toggle MRAM uses an MTJ device with AlOx tunnel barrier and NiFe SAF free layer. The SRAM-like parts are specified for full cycle time of 35 ns for both read and write, but selected parts have been demonstrated to operate to < 25 ns. Improved read

speed has been demonstrated by replacing AlOx with an MgO-based MTJ [24]. Although the relative resistance distributions with MgO are wider than for AlOx, with sigma ~1.5% as compared to sigma ~0.9% for AlOx, the higher MR provides more separation between the high and low resistance distributions, resulting in more usable signal for the read circuit. The MRAM cells using MgO and the NiFe SAF had double the MR compared to AlOx-NiFe, and 42% larger MR/ $\sigma$ , resulting in a reduction of the read cycle time from 21 ns to a circuit-limited 17 ns. Much faster read times are possible for circuits optimized to take advantage of the higher read signal.

#### C. Applications of Toggle MRAM

Toggle MRAM parts are used in a variety of different markets including: data storage, transportation, networking, and industrial automation. The combination of nonvolatility, unlimited endurance, high random access performance, and a wide operating temperature range provides specific market advantages in many of these applications. Often the MRAM chip is replacing another type of memory as well as a battery or capacitor, providing a significant reliability benefit. The main factor limiting further market penetration is the limited memory density, with 16 Mb being the highest density in production. The next higher density MRAM chip currently in production is the 64-Mb part using STT switching [3]. Toggle MRAM is also used as an embedded memory in system-on-chip (SoC) applications. Embedded memories are often much smaller density than standalone memories, making toggle MRAM competitive with incumbent technologies. Since the MTJ layer is inserted between metal layers in the back-end part of the process, fabricating embedded MRAM is no different than fabricating standalone memory.

The application that consumes the largest number of MRAM chips today is RAID data storage systems. MRAM chips with densities usually in the 1–4-Mb range are used in these systems to store metadata, such as restart vectors, controller parameters, system configuration data, and various tables. In case of power failure, this system information is inherently saved in the nonvolatile memory and can be accessed quickly upon restart. This application requires fast, unlimited reads and writes, combined with nonvolatility and high reliability. In this and similar applications, a toggle MRAM part with a parallel interface often replaces some type of SRAM combined with a battery or capacitor to enable data retention when power is lost, providing higher reliability and a lower cost solution.

In transportation and industrial applications, the wide operating temperature range and impressive data retention time are important factors. Toggle MRAM arrays, based on 180-nm technology, have demonstrated data retention times over 20 years at 125 °C, as well as reliable operation from 40 °C to 125 °C [68]. Since MTJ

devices store data with a magnetic state, rather than charge, they have advantages over charge-based memories for space and military applications where exposure to ionizing radiation is an issue. The same MRAM arrays used for industrial grade MRAM are integrated with special radiation-hard CMOS to address those markets.

The higher densities enabled by STT switching are enabling MRAM technology to move into additional storage applications, including caching and buffering, as well as other sockets typically filled by a DRAM.

# VI. SPIN-TRANSFER TORQUE MRAM (STT-MRAM)

#### A. Introduction

One of the limitations of field-switched MRAM introduced at the beginning of this review is the difficulty of maintaining low error rates and high data retention while reducing the size of the MTJ devices. The first effect of shrinking the device dimension is an increase in the switching field distribution width, affecting write currents and error rates, and further shrinking results in loss of data retention time. Although toggle MRAM at the 180- or 130-nm technology nodes has a very large thermal stability factor  $\Delta$ , maintaining a sufficiently large  $\Delta$  for smaller free-layer volume would eventually require a larger anisotropy field  $H_K$  that is difficult to achieve with shape anisotropy. These two scaling issues have led industry to shift from toggle switching to STT switching for technology nodes of 90 nm and below.

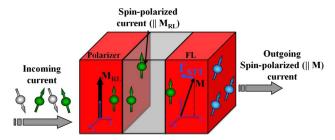

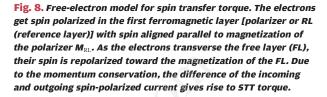

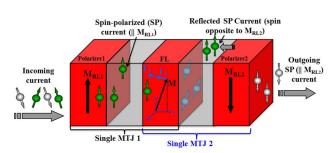

To understand the fundamental physics behind the STT effect, we can use the free-electron model. Let us consider a structure consisting of two ferromagnetic layers separated by a non-magnetic spacer layer (Fig. 8). When a current goes through one ferromagnetic layer, the electrons become spin-polarized along the

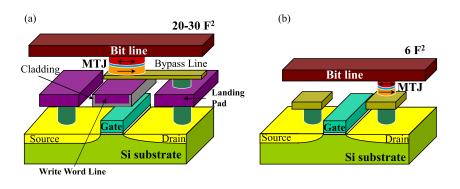

Fig. 9. Structure of conventional field-switched MRAM cell as compared to STT-MRAM cell. (a) Conventional MRAM cell. (b) STT-RAM cell.

magnetization of this layer due to spin-dependent scattering, as shown in Fig. 8. As the spin-polarized current enters the other ferromagnetic layer, the spin of transmitted electrons precesses incoherently around the local exchange field which is along the magnetization of this layer. This exchange field results from the exchange interactions between the spin of the conduction electrons and those responsible for the local magnetization. As a result of that, within a very short distance of the order of 1 nm, the electron current becomes repolarized along the magnetization of the second ferromagnetic layer. Due to momentum conservation, the difference between the momentum of the incoming and outgoing electron currents yields a torque acting on the magnetization of the second ferromagnet-this torque is known as spintransfer torque [28], [29]. Several materials can be used to separate the two ferromagnetic layers. When this material is conducting, the corresponding trilayer structure (ferromagnet-conductor-ferromagnet) is called a spin valve (SV) [69]. Alternatively, if the material is insulating the resultant structure becomes an MTJ.

Magnetoresistance and STT can be viewed as closely related effects. In magnetoresistance, the magnetic structure (parallel or antiparallel orientation of magnetizations) affects the electrical properties of the stack, notably resistance (see Fig. 1). In STT effect, it is the electric current being passed through magnetic structure that can change its magnetic state. In both cases, the fundamental origin lies in the exchange interactions between the spin of conduction electrons (determining electrical properties) and the localized spins (responsible for the magnetic properties).

# **B.** Fundamentals of STT-MRAM

The application of STT writing in MRAM allowed a large reduction of switching current as compared to field-switched MRAM (Fig. 9). As the bit becomes smaller, the writing current decreases proportionally to the MTJ area down to a minimum value dependent on the cell thermal stability factor and other parameters characteristic of the material used for the storage layer. In addition to that, STT-MRAM has a simpler geometry (Fig. 9), eliminating landing pad, word and bypass lines that allows scaling down to cell size of  $4-6F^2$ , where F is the semiconductor feature size. For reducing the cell size even further, it is possible to introduce multiple MTJ elements in one STT-MRAM cell [70]. Such multiple-level cell (MLC) designs will pose more challenges to reduce the writing/reading margins and will likely reduce speed of operation.

1) STT-MRAM Trilemma: Any memory including STT-MRAM has to provide the following basic functionalities: writing the data, retaining the written data for a predefined period of time (retention), and reading the recorded information. This section describes challenges of achieving these three properties together.

a) Information recording—STT writing: In order to discuss details of the STT-MRAM operation, it is necessary to introduce how the STT results in switching. The magnetization dynamics of any magnetic layer can be described by the Landau–Lifshitz–Gilbert (LLG) equation [71]

$$\frac{d\mathbf{m}}{dt} = \Gamma_{\text{prec}} + \Gamma_{\text{damp}}$$

$$\Gamma_{\text{prec}} = -\gamma \mu_0 \mathbf{m} \times \mathbf{H}$$

$$\Gamma_{\text{damp}} = -\alpha \gamma \mu_0 \mathbf{m} \times (\mathbf{m} \times \mathbf{H})$$

(1)

where  $\mathbf{m} \equiv \mathbf{M}/M_{\rm S}$  is the normalized vector along the magnetization  $\mathbf{M}$  of the magnetic layer with saturation magnetization  $M_{\rm S}$ ,  $\mathbf{H}$  is the total effective magnetic field (including anisotropy and applied fields),  $\alpha$  is Gilbert damping,  $\gamma$  is the gyromagnetic ratio, and  $\mu_0$  is the vacuum permeability. The first term  $\Gamma_{\rm prec}$  in (1) describes the precessional motion of magnetization around the effective field  $\mathbf{H}$  while the second term  $\Gamma_{\rm damp}$  describes the gradual damping of the magnetiz field  $\mathbf{H}$ , hence reducing its total energy.

When STT acts on a magnetic layer such as the storage layer in STT-MRAM, two additional terms appear in the LLG equation [28]

$$\frac{d\mathbf{m}}{dt} = \Gamma_{\text{prec}} + \Gamma_{\text{damp}} + \Gamma_{\text{IP}}^{\text{STT}} + \Gamma_{P}^{\text{STT}}$$

$$\Gamma_{\text{STT}}^{\text{IP}} = \gamma \mu_{0} \eta \frac{\hbar J}{2 e} \frac{1}{M_{S} t} \mathbf{m} \times (\mathbf{m} \times \mathbf{m}_{\text{RL}})$$

$$\Gamma_{\text{STT}}^{P} = \gamma \mu_{0} \eta' \frac{\hbar J}{2 e} \frac{1}{M_{S} t} \mathbf{m} \times \mathbf{m}_{\text{RL}} \qquad (2)$$

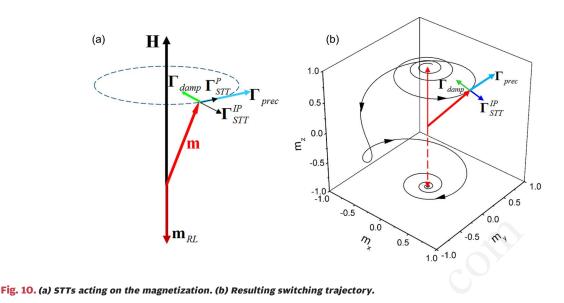

where J is the current density, t is the thickness of the free layer, e is the electron charge,  $\hbar$  is the Planck constant, and  $\eta$  is the spin-transfer efficiency (directly related to the current spin polarization).  $\Gamma_{\text{STT}}^{\text{IP}}$  is the torque lying in the plane defined by the two vectors  $\mathbf{m}$  and  $\mathbf{m}_{RL}$ and hence often called in-plane torque, or damping-like torque (since it has the same form as the Gilbert damping but can change sign depending on the current direction and therefore can behave as an antidamping torque) or Slonczewski torque. The second torque  $\Gamma_{STT}^{P}$  lies perpendicular to this plane and hence is often called perpendicular spin torque or field-like torque. Concerning the magnetization dynamics induced by STT, in the most relevant case of axial symmetry when  $\mathbf{m}_{RL} \| \mathbf{H}$ , the perpendicular STT has the same effect as the precessional torque term, i.e., its main effect is to change the frequency of the magnetization precession. In contrast, the in-plane STT can either enhance or reduce the damping torque, as depicted in Fig. 10. When the in-plane STT opposes the damping torque and overcomes it in magnitude, the amplitude of the precession increases to a point where magnetization switching can occur as illustrated

in Fig. 10(b). The current at which this happens is commonly referred to as critical switching current  $J_{c0}$ .

This action of in-plane STT is often described as a "negative damping" or an "antidamping" [72], [73]. For switching consideration, usually the in-plane torque is most important. However, the perpendicular torque can become relevant in certain specific problems [74]. An example of the switching trajectory for the case of spin torque overcoming damping torque is shown in Fig. 10(b). The initial orientation of the magnetization is along the +Z-axis. The notable change in precession chirality as  $m_z$  crosses zero (counterclockwise to clockwise looking downwards on the XY-plane) is a signature of spin-torque switching and is due to the change of sign of the anisotropy field between upper and lower hemispheres (pointing along +Z for  $m_z > 0$  and -Z for  $m_z < 0$ ).

By solving the LLG equation, the following expressions for the critical switching current of in-plane (IP) and perpendicular to plane (PP) magnetized storage layer [respectively, the case of Fig. 3(b) and (c)] were derived [75]:

$$J_{c0}^{IP} = \frac{1}{\eta} \frac{2\alpha e\mu_0}{\hbar} (M_s t) \left(\frac{H_{\perp eff}}{2} + H_K\right)$$

$$J_{c0}^{PP} = \frac{1}{\eta} \frac{2\alpha e\mu_0}{\hbar} (M_s t) (H_K)$$

(3)

where  $\eta$  is the spin-transfer efficiency, and  $\alpha$ , t,  $H_K$ , and  $H_{\perp eff}$  are, respectively, the magnetic damping constant, thickness, in-plane anisotropy field, and out-of-plane demagnetizing field of the FL, respectively. At this value of the current, effective damping is equal to zero and any infinitesimal precession of magnetization becomes unstable. However, the switching time strongly depends on

#### 1806 PROCEEDINGS OF THE IEEE | Vol. 104, No. 10, October 2016 CuuDuongThanCong.com

#### https://fb.com/tailieudientucntt

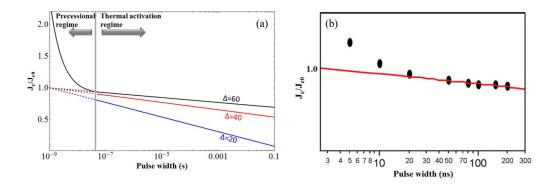

**Fig. 11.** (a) Dependence of switching current density on current pulse width: precessional and thermally activated regimes by modeling and (b) typical experiment. Behavior of the STT-MRAM cells with equal  $J_{co}$  but different thermal stability factor  $\Delta$  is shown in thermally activated regime (a). The data correspond to in-plane magnetized FL. Perpendicular FL exhibit qualitatively similar behavior.

the actual value of the current density with respect to the value of  $J_{c0}$ . As a rule of thumb, if the measurements are done at T = 300 K,  $J_{c0}$  is close to the average switching current density for pulse width  $t_p \sim 10-20$  ns. For longer pulse width, the average switching current density reduces due to thermal fluctuations, which help the magnetization to overcome the energy barrier. Two regimes in  $J_c(t_p)$  are commonly observed, as shown in Fig. 11.

— For very short pulses  $(t_p < 10 \text{ ns})$ , the switching current density is larger than  $J_{c0}$  and during switching, details of individual magnetization precession are important—this is commonly referred as "precessional or ballistic regime." In this precessional regime at T = 0 K, switching current for a given pulse width  $t_p$  is given by [76]

$$J_c^{\rm PP} = J_{c0}^{\rm PP} \left( 1 + \frac{\tau}{t_p} \ln \frac{\pi}{2\theta_0} \right) \tag{4}$$

where  $\tau = (\alpha \gamma \mu_0 H_K)^{-1}$  is the characteristic relaxation time, and  $\theta_0$  is the initial angle between the magnetization and the easy axis when the current pulse is turned on.

From (3), it is clearly seen that for a given damping, spin-torque efficiency and memory retention (the latter being directly related to  $H_k$ ), STT-MRAM with perpendicular anisotropy should operate with lower switching current density. This and other reasons described below explain why most of the R&D in STT-MRAM is focused on cells based on out-of-plane magnetized MTJs. If the switching is performed at nonzero temperature, there will be two important effects due to random thermal fluctuations. First, the initial angle  $\theta_0$  will be distributed according to Maxwell–Boltzmann distribution [73], introducing distribution of switching current for a given

pulse width. This effect is most important for short pulse width, typically for  $t_p < 20-50$  ns; see Fig. 11. Second, thermal fluctuations will affect the switching process itself.

For longer pulse width values, usually for  $t_p > 50-100$  ns, this switching regime is called thermally activated regime (Fig. 11). In this case, STT effect starts to play a secondary role by increasing effective temperature of the magnetization, thus increasing thermal fluctuations, which in turn, help the magnetization to overcome the energy barrier. The boundary between the two regimes is not very well defined and depends on the FL properties but usually this boundary corresponds to switching current near but less than  $J_{c0}$ . Based on thermal activation model, the following expression has been derived for STT-MRAM in thermally activated regime: [76]–[78]

$$J_{c} = J_{c0} \left( 1 - \left( \frac{1}{\Delta} \ln \frac{t_{pw}}{\tau_{0}} \right)^{\frac{1}{\xi}} \right)$$

$$\xi = \begin{cases} 1 \text{ for IP FL} \\ 2 \text{ for PP FL} \end{cases}$$

(5)

where  $\Delta$  is the thermal stability factor (ratio of energy barrier for switching in standby  $E_b = \mu_0 M_s H_k V/2$  divided by the thermal activation  $k_B T$ , V being the volume,  $k_B$  the Boltzmann constant, and T the temperature),  $\tau_0$  is an intrinsic attempt time of the order of 1 ns and the parameter  $\xi$  is equal to 1 or 2 for respectively in-plane and out-of-plane magnetized FL [77]–[79]. This dependence is often used to experimentally determine  $J_{c0}$  and  $\Delta$  for IP FL by measuring median  $J_c$  at different pulse width spanning a few decades, and fitting  $J_c$  as a function of  $\log(t_p)$ and extrapolating to 1 ns: the slope yields the thermal stability  $\Delta$  and the extrapolated  $J_c$  (1 ns) gives  $J_{c0}$ . This approach (with  $\xi = 1$ ) has also been used for PP FL. However, it was shown to give inaccurate results unless fitting with  $\xi = 2$  is used [78].

b) Information storing: Similar to field-switched MRAM discussed earlier in this review, the information retention capability is determined by the energy barrier  $E_b$  that the free layer magnetization has to overcome to switch to opposite state in standby divided by the thermal activation energy at the operation temperature [80]

$$\Delta = \frac{E_b}{k_B T}.$$

(6)

This expression holds for both in-plane and perpendicular STT-MRAM free layers. For small dimensions and high density, perpendicular STT-MRAM is preferred, as will be discussed later.

Typically,  $\Delta > 60-80$  is needed to guarantee reliable data retention for ten years. For IP free layer, the energy barrier is provided by shape anisotropy (thus requiring elongated shapes) and is given by

$$\Delta^{\rm IP} = \frac{E_b}{k_B T} = \frac{\mu_0 H_K M_S V}{2k_B T}.$$

(7)

For in-plane free layer with elliptical cross section with short axis of dimension *w*, one can derive a simplified expression for the effective anisotropy field

$$H_K^{\rm IP} = 2 \frac{M_S t (\rm AR} - 1)}{\rm wAR}$$

(8)

where AR is the in-plane aspect ratio: length divided by width. Thus, the thermal stability becomes

$$\Delta^{\rm IP} = \frac{\mu_0 \pi (M_S t)^2 w (AR - 1)}{8k_B T}.$$

(9)

From this expression, we can see that the stability of in-plane magnetized cells is proportional to the square of the moment per unit surface  $(M_s t)$  and width of the cell.  $M_s t$  is a quantity that can easily be measured by VSM magnetometry. This expression, which is derived based on assumption that the free layer magnetization switches uniformly (macrospin approximation) is in good agreement with experimental observations, provided that AR is not excessively large (< 2.5–3) and macrospin approximation is valid.

For FL with perpendicular magnetization, a general expression for the anisotropy energy density can be written as follows:

$$K^{\rm PP} = K_b^{\rm PP} + \frac{\sigma_i}{t} - \frac{1}{2}\mu_0 M_S^2 = \frac{\mu_0 H_K^{\rm PP} M_S}{2}$$

(10)

where  $\sigma_i$  is the perpendicular surface anisotropy per unit surface taking into account the two interfaces of the FL, and  $K_b^{\rm PP}$  is the bulk anisotropy (per unit volume). The term  $-1/2 \ \mu_0 M_s^2$  is the demagnetizing energy which tends to bring back the magnetization in-plane.

Two classes of PMA materials are often distinguished based on the dominant origin of anisotropy [81]:

- bulk perpendicular magnetic anisotropy (B-PMA);

- interfacial perpendicular magnetic anisotropy (I-PMA).

The former usually involves materials, which have crystalline anisotropy due to reduced crystalline symmetry, making in-plane and out-of-plane directions not equivalent. Examples of such materials are FePt and CoPt alloys or multilayers. In most of these materials, binary or ternary alloys are used and at least one constituent material has high atomic (Z) number, which provides high spin-orbit coupling and correlatively large damping. While strong anisotropy is beneficial for perpendicular STT-MRAM free layer, large damping is not desired since switching current is proportional to damping (3).

The latter, I-PMA anisotropy, is related to interaction between the ferromagnetic film and the adjacent layer. An important class of I-PMA materials are based on the interface between a metallic ferromagnet and an oxide, which was demonstrated in 2002 using Pt/CoFe/AlOx structures [44], [82], [83]. Since the presence of Pt is undesirable due to an increase in damping from the spinpumping effect, the same I-PMA at magnetic metal/oxide interface was later demonstrated in Pt-free structures suitable for STT-MRAM, namely Ta/CoFeB/MgO structures [41], [43]. This material has several important advantages as compared to B-PMA materials: very good lattice matching with MgO, low damping combined with large interfacial anisotropy, and high spin-polarization yielding a large TMR amplitude. However, one challenge when using I-PMA materials is to obtain a sufficiently high thermal stability, especially at small (sub-20-nm) dimensions. In B-PMA material, increasing the FL thickness while keeping everything else the same provides an easy and effective way to increase the thermal stability of the FL

$$\Delta_{\rm QU}^{\rm PP-B} = \left(K_b^{\rm PP} - \frac{\mu_0}{2}M_s^2\right) \frac{\pi D^2 t}{4k_B T} \tag{11}$$

https://fb.com/tailieudientucntt

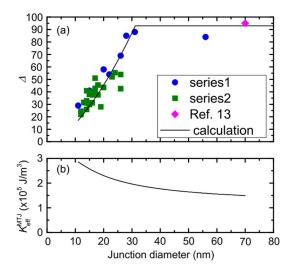

Fig. 12. Experimental dependence of thermal stability  $\triangle$  on the junction size (reprinted from [47] with permission). These data exhibit saturation of  $\triangle$  at larger diameters indicating nonuniform magnetization reversal.

where *B* stands for B-PMA, *QU* stands for quasi-uniform approximation (i.e., assuming that the magnetization of the FL switches uniformly), and *D* is the diameter of the free layer.

In contrast, for I-PMA, assuming that the interfacial anisotropy is a property of the interface and does not change as the thickness of the ferromagnetic layer increases, the thermal stability decreases with thickness according to

$$\Delta_{\rm QU}^{\rm PP-I} = \left(\sigma_i - \frac{\mu_0}{2}M_S^2 t\right) \frac{\pi D^2}{4k_B T} = \kappa_i \frac{\pi D^2}{4k_B T} \qquad (12)$$

where we have introduced  $\kappa_i = \sigma_i - (\mu_0/2)M_S^2 t$  as the perpendicular magnetic anisotropy per unit area. This parameter plays a very important role in PMA free layer. It directly determines how small a given free layer can be made while still being stable, as will be discussed later in the text. The expressions of  $\Delta$  in the two equations above were derived assuming coherent macrospin switching of the free layer, which works well at very small cell dimensions (typically below 30 nm in diameter). Both I-PMA and B-PMA materials have significant discrepancies with experimental data at larger dimensions (see Fig. 12) [84]. Indeed, at large dimensions, the evolution of  $\Delta$  versus the cell dimension observed experimentally is different from the  $D^2$  quadratic behavior predicted by (11) and (12). Rather, it exhibits a saturation for D > 40 nm, as illustrated in Fig. 12.

The two main approaches to increasing  $\Delta$  for I-PMA free layers include increasing  $\sigma_i$  and reducing  $M_s$ . A useful approach for obtaining more interfacial anisotropy energy includes the use of two MgO interfaces, one on each surface

of the FL [46], [85]. This enables the approximate doubling interfacial anisotropy acting on the FL magnetization.

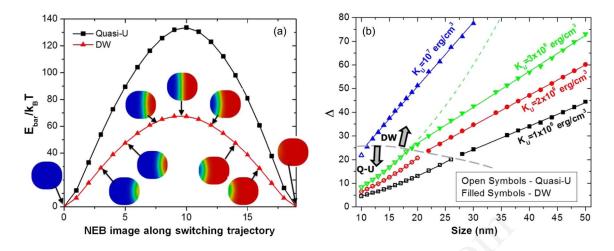

This change of behavior in the evolution of  $\Delta$  versus the diameter between small and large dimensions is related to a change in switching mode from coherent rotation at small dimensions to nucleation/propagation reversal of magnetization at larger dimensions [86]. As a matter of fact, at dimensions above 40 nm, much less energy is required to reverse the FL magnetization by nucleating a reversed domain in the FL and propagating a domain wall (DW) across the FL than to switch the magnetization coherently. This can be demonstrated by a nudged elastic band (NEB) simulation [87]. This method consists in constructing a series of magnetic states of the free layer connecting the initial and final states (e.g., magnetization "up" and magnetization "down"). Then, each image is moved along local energy gradient while keeping the images equidistant. This procedure is repeated until convergence is found. The resultant series of images corresponds to a switching path that has minimum energy barrier. This procedure was applied to a perpendicular FL with typical parameters and it was found that even for relatively small dimensions (20-30 nm), switching by a quasi-uniform rotation results in a much larger energy barrier than switching by DW formation and propagation [46], [86] (see Fig. 13). Thus, equations (11) and (12) must be replaced by the following approximate expression that describes the energy needed to create a DW across the diameter of the free layer:

$$\Delta_{\rm DW}^{\rm PP} \approx \frac{4\sqrt{A_{\rm ex}K^{\rm PP}}Dt}{k_{\rm B}T} \tag{13}$$

where  $A_{ex}$  is the exchange stiffness in the free layer. In this expression,  $K^{PP}$  is given by (10).

As the diameter of the free layer changes, the energy to create a DW reduces linearly with the diameter, whereas the energy for coherent rotation scales as the square of the diameter. Thus, at some critical dimension, the two energies cross each other yielding the observed crossover in switching behavior. For small sizes (below 30-nm diameter), quasi-uniform rotation results in smaller energy barrier and thus becomes the primary switching mechanism (see Fig. 13 below 30 nm). The critical dimension corresponding to the change of switching modes depends on the material parameters, e.g., increasing  $K^{PP}$  shifts it to smaller sizes.

In experiments, thermal stability often showed saturation at larger dimensions, as shown in Fig. 12 above 30 nm [47], [57]. This observation is contrary to what is expected from either single-domain model or NEB simulations (Fig. 13). A number of explanations were proposed over the years in order to improve the model to better match experimental observations, such as effective subvolume nucleation mechanism [88], edge nucleation mode [89], and others.

Fig. 13. (a) NEB simulation for minimum energy barrier: comparison of quasi-uniform switching (black) to DW switching (red). (b) Dependence of thermal stability on size: smaller dimension-quadratic behavior, larger dimensions-linear. Crossover between quadratic and linear behavior moves to smaller dimensions at larger anisotropy. The short dimension of MTJ cell is 20 nm, and thickness of the free layer is 0.85 nm [86].

In another direction, researchers investigated whether experimental measurement of  $\Delta$  [90] was accurate. For a typical thermal stability (above 60), direct measurement of retention (e.g., by measuring probability of thermally activated switching of a chip at room temperature) is impossible and some acceleration techniques have to be used. Usually, they involve either modifying the energy barrier (by applying external magnetic field, spin torque, or both) or varying the temperature (chip baking at temperature significantly higher than room temperature). In all cases, a model is needed to quantify the dependence of  $\Delta$  on the field, current, or temperature. Until recently, the researchers have been using models which have two important assumptions:

- uniform switching (or macrospin-like switching);

- energy barrier dependent on current with exponent of  $\xi = 1$  [see (5)] [78] for both in-plane and perpendicular designs.

Both assumptions are not generally well justified for perpendicular MTJs. On the contrary, modeling shows that the thermally activated switching occurs by DW propagation (Fig. 13) and that the dependence of  $\Delta$  on the field is more complicated than what was derived assuming macrospin behavior [91], [84, eq. (11)]. Extension of the  $\Delta$  (*H*) model to DW-mitigated switching was performed recently [92, eq. (2)] and evaluation of  $\Delta$  using this model showed that indeed thermal stability is increasing linearly with increasing dimensions even well above 40 nm with excellent agreement with NEB simulations and chip data retention measurements at higher temperature without external field [92], solving the long-standing paradox of inconsistent behavior of thermal stability at larger dimensions.

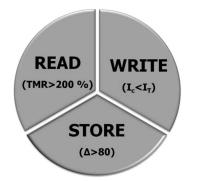

c) Simultaneous achievement of writability, readability, and retention—STT-MRAM trilemma: A key challenge for STT-MRAM is the simultaneous achievement of low switching current, high thermal stability, and large TMR. For reading, some minimum TMR is needed to have a sufficient signal for determination of the resistance state by the read circuit. The actual TMR needed is dependent on the details of the read scheme and the bit-to-bit resistance distributions, but a common requirements for minimum TMR in MRAM arrays are between 150% and 300%, sometimes more. For STT writing, the desired case is to have a switching current that is less than the saturation current of a minimum-sized transistor at the specified technology node. For storing the information, a typical requirement is to have thermal stability factor  $\Delta$  > 80 for 1-Gb memory array. The issue of engineering devices to meet all three of the above requirements is sometimes called the "STT-MRAM trilemma" (Fig. 14), since it is often possible to improve one or two of the properties but at the expense of another. For example, for in-plane STT-MRAM, increasing the thickness of the FL provides an easy way to improve TMR and thermal stability, but the switching current increases as well. In the next section, we will discuss some approaches toward overcoming the boundaries of the trilemma using special designs.

#### 2) Breaking STT-MRAM Trilemma

a) Material improvements—Damping and STT efficiency: One important approach to improve STT-MRAM characteristics involves development of better materials for MTJ structure. From (3), reducing damping helps and increasing STT efficiency and polarization also contributes to reducing  $J_{c0}$ . Historically, for these reasons, CoFeB materials with various compositions have been used. They provide low damping constant of 0.005– 0.015, good spin polarization, and high TMR. At this

Fig. 14. An example STT-MRAM trilemma. Simultaneously three properties have to be satisfied: reading, writing, and storing. In this example, it is necessary to have TMR > 200% for reliable reading, switching current less than that supplied by a small transistor for small cell size, and thermal stability factor  $\Delta$  > 80 to meet a desired data retention goal.

moment, the highest TMR achieved at room temperature is 604% for CoFeB/MgO/CoFeB structure [22]. Damping has been shown to be strongly dependent on film thickness, increasing greatly for the thinnest films due to a spin-pumping contribution that can be mitigated by using an insulating capping material [93].

In addition to CoFeB, there has been significant work on developing alternative materials to reduce damping and increase polarization. The most famous example include half-metallic materials, which, at Fermi energy, have energy gap in one of the sub-bands (e.g., for spindown) and thus not only should provide 100% polarization, which translates to infinite TMR (at 0 K), but also should give very low intrinsic damping. Very high values of TMR (> 2000%) were indeed achieved at low temperatures (4 K). However, at room temperature, the halfmetallic materials have failed to exceed or even reach the TMR provided by CoFeB alloys. There are a few fundamental difficulties with half-metallic materials that have to be overcome. Most of these materials are predicted or demonstrated to have half-metallicity in bulk form. However, once these materials are made as thin films (compatible with STT-MRAM FL requirements) and incorporated next to MgO, or another tunneling barrier, half-metallicity can be lost due to lattice modifications and electronic density of state changes. In addition, the majority of half-metallic materials are cubic and do not possess perpendicular magnetic anisotropy, limiting their potential use to in-plane STT-MRAM. There have been a few approaches to address this, e.g., by using interfacial anisotropy [43] or creating a superlattice of two alternating distinct half-metallic materials [94].

b) Design improvements

In-plane (IP) STT-MRAM with PPMA: One interesting approach to go beyond the boundaries of STT-MRAM trilemma consists in partially balancing the demagnetizing energy of the in-plane magnetized storage layer by a perpendicular anisotropy which has to be smaller than the demagnetizing energy. This anisotropy is often called partial perpendicular anisotropy (PPMA). If we look at (3) for  $J_{c0}$  of the in-plane FL, the term in the parenthesis involves  $H_{\perp eff}$ . This is the field which is needed to saturate the FL magnetization in the direction perpendicular to the plane. Without any PPMA, this field is equal to  $\mu_0 M_S$ . If PPMA with effective anisotropy field  $H_{K\perp}$  is introduced, it becomes

$$H_{\perp eff} = M_S - H_{K\perp} = M_S \left( 1 - \frac{H_{K\perp}}{M_S} \right) = M_S (1 - h_{K\perp})$$

(14)

where we have introduced dimensionless PPMA effective field  $h_{K\perp}$  as the perpendicular anisotropy field normalized by the demagnetizing field

$$h_{K\perp} = \frac{H_{K\perp}}{M_S}.$$

(15)

For increasing PPMA, the switching current  $J_{c0}$  can be reduced

$$J_{c0}^{\rm IP} = \frac{1}{\eta} \frac{2\mu_0 \alpha e}{\hbar} (M_s t) M_s \left(\frac{1 - h_{K\perp}}{2} + h_K\right) \tag{16}$$

where dimensionless in-plane (shape) anisotropy field  $h_K = H_K/M_S$  was introduced. As can be seen from (16), effectiveness of PPMA to reduce  $J_{c0}$  is larger for smaller in-plane  $H_K$  value, thus for larger dimensions. For smaller dimensions, we need larger  $H_K$  to maintain stability and PPMA effectiveness is reduced.

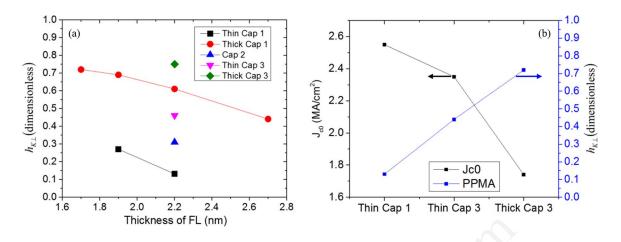

An important advantage of PPMA is that it can be introduced without change in thermal stability or TMR and can fundamentally change the boundaries of STT-MRAM trilemma. One efficient way to introduce PPMA into an existing FL is by using different capping material. This has been experimentally demonstrated [95], [96], where PPMA level was varied from 10% to 80% by modifications of the cap material and thickness. PPMA is decreasing as the thickness of the FL is reducing [Fig. 15(a)], which suggests its interfacial origin. Fig. 15(b) demonstrates that device switching critical current  $J_{c0}$  follows the trend of PPMA.

Despite the fact that PPMA was shown to be very effective to break STT-MRAM trilemma and reduce  $J_{c0}$  without changes to thermal stability or TMR, it has a few limitations. One of the limitations is that at large PPMA ( $h_{K\perp} > 0.85$  for short axis of 50–60 nm), thermal stability starts to degrade. This is due to reduced

**Fig. 15.** (a) Experimental demonstration of PPMA due to different capping materials used. (b) Reduction of J<sub>c0</sub> by different capping materials.

demagnetizing field at edges of the FL that results in small out-of-plane tilting of the magnetization that, respectively, reduces in-plane component and shape anisotropy. In addition to that, even though large PPMA reduces  $J_{c0}$  and  $J_c$  at long pulses quite significantly, it becomes less effective in the precessional regime for  $t_p < 20$  ns. This is due to a reduction of critical relaxation time  $\tau$  that determines the switching dynamics in the precessional regime. Hence, effectiveness of PPMA depends heavily on target application of the STT-MRAM product, including cell dimensions, switching time, and retention requirements, and will likely be most applicable to dimensions above 40 nm.

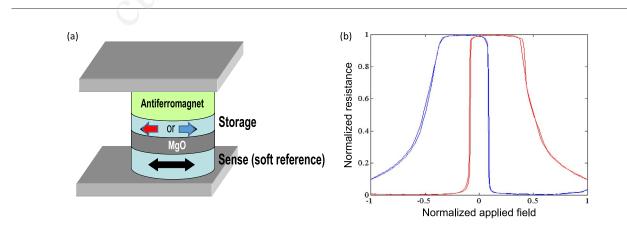

Perpendicular MTJ design (P-STT-MRAM): In the previous section, we have been focusing on in-plane MTJ designs with equilibrium magnetization states in the plane of the free layer film. However, increasing PMA until it exceeds the thin-film demagnetizing energy results in a free layer magnetization with an easy axis perpendicular to the film plane, providing additional benefits. First, the switching current can be reduced, compared to in-plane magnetized free layers, for the same thermal stability [see (3)]. Second, elongated bit shapes are not needed since the perpendicular anisotropy is an intrinsic property of the free layer material. This not only alleviates patterning and size control requirements but also helps to reduce the memory cell size, increasing the achievable array density in an STT-MRAM circuit. Such devices are practical because interfacial perpendicular anisotropy as high as 2 mJ/m<sup>2</sup> has been demonstrated, enough to make a stable free layer with sub-10-nm dimensions. These benefits make perpendicular STT-MRAM most desirable for high-density (e.g., DRAM) applications.

The first observation of STT switching in perpendicular MTJ was achieved independently by Tohoku University and HGST in 2006 on GMR structures [97], [98],

using Co/Ni, Co/Pt, or FePt materials. Materials with high Z number, such as Pt or Pd, introduce high spinorbit interactions which increase the perpendicular anisotropy but also increase the free layer damping, which is highly undesirable. Even though the perpendicular configuration was expected to improve current density compared to in-plane devices, the high damping of these particular perpendicular materials seems to have offset the potential improvement. In addition to high damping, these PMA materials usually have threefold in-plane lattice symmetry, for example, from FCC (111) textured film growth, which is not inherently compatible with the fourfold symmetry of the (001) oriented MgO tunnel barrier needed for high TMR and high spin-torque efficiency. The interfacial epitaxy problem can be mitigated by including amorphous CoFeB alloy in the free layer, separated from the polycrystalline layers by inserting another material, such as Ta, to break crystallographic coherence between the bulk-PMA material and CoFeB, but with a penalty in complexity and limitations on the free layer design.

The demonstration in 2010 of fully perpendicular CoFeB-based free layers employing only the interfacial anisotropy at the magnetic metal/oxide interface [42] showed it was possible to combine large anisotropy with weak damping and good symmetry matching. Beginning with this demonstration in a simple structure with MgO on one side (Ta/CoFeB/MgO), [43], [55], this approach was further developed and widely adopted for perpendicular STT-MRAM development by researchers in industry and academia. Achieving a stable free layer in this system required the use of very thin CoFeB layers, which resulted in a significant damping increase compared to thicker layers. In addition, the achievable anisotropy strength of such free layers was found to be insufficient to provide adequate  $\Delta$  for small (< 30 nm) device dimensions. Both of these problems were solved

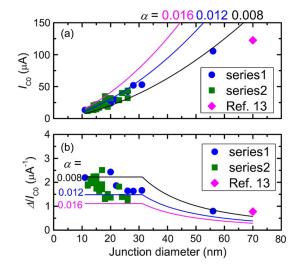

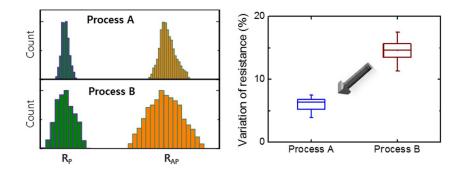

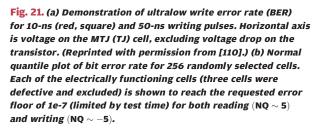

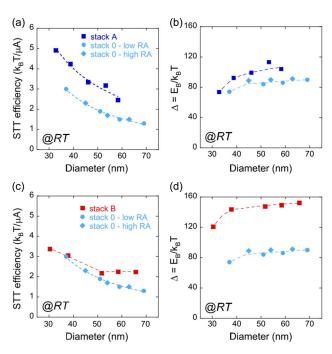

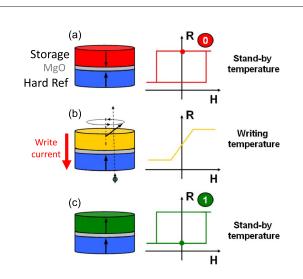

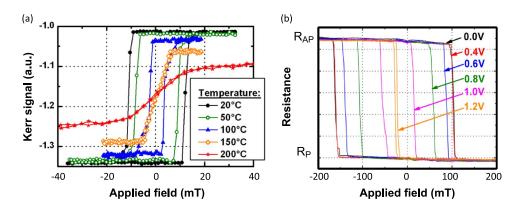

**Fig. 16.** Critical switching current (a) and figure of merit  $(\Delta/ICO)$  (b) as a function of MTJ diameter. (Reprinted with permission from [47].)