# 2.1

#### Introduction

instruction set The vocabulary of commands understood by a given architecture.

To command a computer's hardware, you must speak its language. The words of a computer's language are called *instructions*, and its vocabulary is called an **instruction set**. In this chapter, you will see the instruction set of a real computer, both in the form written by humans and in the form read by the computer. We introduce instructions in a top-down fashion. Starting from a notation that looks like a restricted programming language, we refine it step-by-step until you see the real language of a real computer. Chapter 3 continues our downward descent, unveiling the representation of integer and floating-point numbers and the hardware that operates on them.

You might think that the languages of computers would be as diverse as those of humans, but in reality computer languages are quite similar, more like regional dialects than like independent languages. Hence, once you learn one, it is easy to pick up others. This similarity occurs because all computers are constructed from hardware technologies based on similar underlying principles and because there are a few basic operations that all computers must provide. Moreover, computer designers have a common goal: to find a language that makes it easy to build the hardware and the compiler while maximizing performance and minimizing cost. This goal is time-honored; the following quote was written before you could buy a computer, and it is as true today as it was in 1947:

It is easy to see by formal-logical methods that there exist certain [instruction sets] that are in abstract adequate to control and cause the execution of any sequence of operations.... The really decisive considerations from the present point of view, in selecting an [instruction set], are more of a practical nature: simplicity of the equipment demanded by the [instruction set], and the clarity of its application to the actually important problems together with the speed of its handling of those problems.

Burks, Goldstine, and von Neumann, 1947

The "simplicity of the equipment" is as valuable a consideration for computers of the 2000s as it was for those of the 1950s. The goal of this chapter is to teach an instruction set that follows this advice, showing both how it is represented in hardware and the relationship between high-level programming languages and this more primitive one. Our examples are in the C programming language; Section 2.14 shows how these would change for an object-oriented language like Java.

By learning how to represent instructions, you will also discover the secret of computing: the **stored-program concept**. Moreover you will exercise your "foreign language" skills by writing programs in the language of the computer and running them on the simulator that comes with this book. You will also see the impact of programming languages and compiler optimization on performance. We conclude with a look at the historical evolution of instruction sets and an overview of other computer dialects.

The chosen instruction set comes from MIPS, which is typical of instruction sets designed since the 1980s. Almost 100 million of these popular microprocessors were manufactured in 2002, and they are found in products from ATI Technologies, Broadcom, Cisco, NEC, Nintendo, Silicon Graphics, Sony, Texas Instruments, and Toshiba, among others.

We reveal the MIPS instruction set a piece at a time, giving the rationale along with the computer structures. This top-down, step-by-step tutorial weaves the components with their explanations, making assembly language more palatable. To keep the overall picture in mind, each section ends with a figure summarizing the MIPS instruction set revealed thus far, highlighting the portions presented in that section.

stored-program concept The idea that instructions and data of many types can be stored in memory as numbers, leading to the stored program computer.

# 2.2

# **Operations of the Computer Hardware**

Every computer must be able to perform arithmetic. The MIPS assembly language notation

```

add a, b, c

```

instructs a computer to add the two variables b and c and to put their sum in a.

This notation is rigid in that each MIPS arithmetic instruction performs only one operation and must always have exactly three variables. For example, suppose we want to place the sum of variables b, c, d, and e into variable a. (In this section we are being deliberately vague about what a "variable" is; in the next section we'll explain in detail.)

The following sequence of instructions adds the four variables:

```

add a, b, c # The sum of b and c is placed in a.

add a, a, d # The sum of b, c, and d is now in a.

add a, a, e # The sum of b, c, d, and e is now in a.

```

There must certainly be instructions for performing the fundamental arithmetic operations.

Burks, Goldstine, and von Neumann, 1947 Thus, it takes three instructions to take the sum of four variables.

The words to the right of the sharp symbol (#) on each line above are *comments* for the human reader, and the computer ignores them. Note that unlike other programming languages, each line of this language can contain at most one instruction. Another difference from C is that comments always terminate at the end of a line.

The natural number of operands for an operation like addition is three: the two numbers being added together and a place to put the sum. Requiring every instruction to have exactly three operands, no more and no less, conforms to the philosophy of keeping the hardware simple: hardware for a variable number of operands is more complicated than hardware for a fixed number. This situation illustrates the first of four underlying principles of hardware design:

Design Principle 1: Simplicity favors regularity.

We can now show, in the two examples that follow, the relationship of programs written in higher-level programming languages to programs in this more primitive notation.

#### Compiling Two C Assignment Statements into MIPS

This segment of a C program contains the five variables a, b, c, d, and e. Since Java evolved from C, this example and the next few work for either high-level programming language:

```

a = b + c;

d = a - e;

```

The translation from C to MIPS assembly language instructions is performed by the *compiler*. Show the MIPS code produced by a compiler.

A MIPS instruction operates on two source operands and places the result in one destination operand. Hence, the two simple statements above compile directly into these two MIPS assembly language instructions:

```

add a, b, c sub d, a, e

```

#### **EXAMPLE**

#### **Compiling a Complex C Assignment into MIPS**

A somewhat complex statement contains the five variables f, g, h, i, and j:

$$f = (q + h) - (i + j);$$

What might a C compiler produce?

The compiler must break this statement into several assembly instructions since only one operation is performed per MIPS instruction. The first MIPS instruction calculates the sum of g and h. We must place the result somewhere, so the compiler creates a temporary variable, called t0:

```

add t0,g,h # temporary variable t0 contains g + h

```

Although the next operation is subtract, we need to calculate the sum of i and j before we can subtract. Thus, the second instruction places the sum i and j in another temporary variable created by the compiler, called t1:

```

add t1,i,j # temporary variable t1 contains i + j

```

Finally, the subtract instruction subtracts the second sum from the first and places the difference in the variable f, completing the compiled code:

```

sub f,t0,t1 \# f gets t0 - t1, which is (g + h)-(i + j)

```

Figure 2.1 summarizes the portions of MIPS assembly language described in this section. These instructions are symbolic representations of what the MIPS processor actually understands. In the next few sections, we will evolve this symbolic representation into the real language of MIPS, with each step making the symbolic representation more concrete.

#### MIPS assembly language

| Category   | Instruction | Example   | Meaning   | Comments              |

|------------|-------------|-----------|-----------|-----------------------|

| Arithmetic | add         | add a,b,c | a = b + c | Always three operands |

|            | subtract    | sub a,b,c | a = b - c | Always three operands |

**FIGURE 2.1 MIPS architecture revealed in Section 2.2.** The real computer operands will be unveiled in the next section. Highlighted portions in such summaries show MIPS assembly language structures introduced in this section; for this first figure, all is new.

**EXAMPLE**

### Check Yourself

For a given function, which programming language likely takes the most lines of code? Put the three representations below in order.

- 1. Java

- 2. C

- 3. MIPS assembly language

**Elaboration:** To increase portability, Java was originally envisioned as relying on a software interpreter. The instruction set of this interpreter is called *Java bytecodes*, which is quite different from the MIPS instruction set. To get performance close to the equivalent C program, Java systems today typically compile Java bytecodes into the native instruction sets like MIPS. Because this compilation is normally done much later than for C programs, such Java compilers are often called *Just-In-Time* (JIT) compilers. Section 2.10 shows how JITs are used later than C compilers in the startup process, and Section 2.13 shows the performance consequences of compiling versus interpreting Java programs. The Java examples in this chapter skip the Java bytecode step and just show the MIPS code that are produced by a compiler.

# 2.3

# **Operands of the Computer Hardware**

Unlike programs in high-level languages, the operands of arithmetic instructions are restricted; they must be from a limited number of special locations built directly in hardware called *registers*. Registers are the bricks of computer construction: registers are primitives used in hardware design that are also visible to the programmer when the computer is completed. The size of a register in the MIPS architecture is 32 bits; groups of 32 bits occur so frequently that they are given the name word in the MIPS architecture.

One major difference between the variables of a programming language and registers is the limited number of registers, typically 32 on current computers. MIPS has 32 registers. (See Section 2.19 for the history of the number of registers.) Thus, continuing in our top-down, stepwise evolution of the symbolic representation of the MIPS language, in this section we have added the restriction that the three operands of MIPS arithmetic instructions must each be chosen from one of the 32 32-bit registers.

The reason for the limit of 32 registers may be found in the second of our four underlying design principles of hardware technology:

word The natural unit of access in a computer, usually a group of 32 bits; corresponds to the size of a register in the MIPS architecture.

Design Principle 2: Smaller is faster.

A very large number of registers may increase the clock cycle time simply because it takes electronic signals longer when they must travel farther.

Guidelines such as "smaller is faster" are not absolutes; 31 registers may not be faster than 32. Yet, the truth behind such observations causes computer designers to take them seriously. In this case, the designer must balance the craving of programs for more registers with the designer's desire to keep the clock cycle fast. Another reason for not using more than 32 is the number of bits it would take in the instruction format, as Section 2.4 demonstrates.

Chapters 5 and 6 show the central role that registers play in hardware construction; as we shall see in this chapter, effective use of registers is key to program performance.

Although we could simply write instructions using numbers for registers, from 0 to 31, the MIPS convention is to use two-character names following a dollar sign to represent a register. Section 2.7 will explain the reasons behind these names. For now, we will use \$\$0, \$\$1,... for registers that correspond to variables in C and Java programs and \$\$t0, \$\$t1,... for temporary registers needed to compile the program into MIPS instructions.

#### **Compiling a C Assignment Using Registers**

It is the compiler's job to associate program variables with registers. Take, for instance, the assignment statement from our earlier example:

```

f = (g + h) - (i + j);

```

The variables f, g, h, i, and j are assigned to the registers \$50, \$51, \$52, \$53, and \$54, respectively. What is the compiled MIPS code?

The compiled program is very similar to the prior example, except we replace the variables with the register names mentioned above plus two temporary registers, \$t0 and \$t1, which correspond to the temporary variables above:

```

add t0,s1,s2 \# register t0 contains g + h

add t1,s3,s4 \# register t1 contains i + j

sub s0,t0,t1 \# f gets t0 - t1, which is (g + h)-(i + j)

```

**EXAMPLE**

#### **Memory Operands**

Programming languages have simple variables that contain single data elements as in these examples, but they also have more complex data structures—arrays and structures. These complex data structures can contain many more data elements than there are registers in a computer. How can a computer represent and access such large structures?

Recall the five components of a computer introduced in Chapter 1 and depicted on page 47. The processor can keep only a small amount of data in registers, but computer memory contains millions of data elements. Hence, data structures (arrays and structures) are kept in memory.

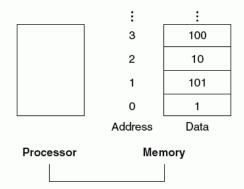

As explained above, arithmetic operations occur only on registers in MIPS instructions; thus, MIPS must include instructions that transfer data between memory and registers. Such instructions are called **data transfer instructions**. To access a word in memory, the instruction must supply the memory **address**. Memory is just a large, single-dimensional array, with the address acting as the index to that array, starting at 0. For example, in Figure 2.2, the address of the third data element is 2, and the value of Memory[2] is 10.

The data transfer instruction that copies data from memory to a register is traditionally called *load*. The format of the load instruction is the name of the operation followed by the register to be loaded, then a constant and register used to access memory. The sum of the constant portion of the instruction and the contents of the second register forms the memory address. The actual MIPS name for this instruction is <code>lw</code>, standing for *load word*.

data transfer instruction A command that moves data between memory and registers.

address A value used to delineate the location of a specific data element within a memory array.

**FIGURE 2.2** Memory addresses and contents of memory at those locations. This is a simplification of the MIPS addressing; Figure 2.3 shows the actual MIPS addressing for sequential word addresses in memory.

#### Compiling an Assignment When an Operand Is in Memory

Let's assume that A is an array of 100 words and that the compiler has associated the variables g and h with the registers \$s1 and \$s2 as before. Let's also assume that the starting address, or *base address*, of the array is in \$s3. Compile this C assignment statement:

```

q = h + A[8];

```

Although there is a single operation in this assignment statement, one of the operands is in memory, so we must first transfer A[8] to a register. The address of this array element is the sum of the base of the array A, found in register \$53, plus the number to select element 8. The data should be placed in a temporary register for use in the next instruction. Based on Figure 2.2, the first compiled instruction is

```

lw $t0,8($s3) # Temporary reg $t0 gets A[8]

```

(On the next page we'll make a slight adjustment to this instruction, but we'll use this simplified version for now.) The following instruction can operate on the value in \$t0 (which equals A[8]) since it is in a register. The instruction must add h (contained in \$s2) to A[8] (\$t0) and put the sum in the register corresponding to g (associated with \$s1):

```

add $s1,$s2,$t0 # g = h + A[8]

```

The constant in a data transfer instruction is called the *offset*, and the register added to form the address is called the *base register*.

**EXAMPLE**

# Hardware Software Interface

#### alignment restriction

A requirement that data be aligned in memory on natural boundaries In addition to associating variables with registers, the compiler allocates data structures like arrays and structures to locations in memory. The compiler can then place the proper starting address into the data transfer instructions.

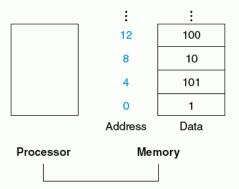

Since 8-bit *bytes* are useful in many programs, most architectures address individual bytes. Therefore, the address of a word matches the address of one of the 4 bytes within the word. Hence, addresses of sequential words differ by 4. For example, Figure 2.3 shows the actual MIPS addresses for Figure 2.2; the byte address of the third word is 8.

In MIPS, words must start at addresses that are multiples of 4. This requirement is called an **alignment restriction**, and many architectures have it. (Chapter 5 suggests why alignment leads to faster data transfers.)

Computers divide into those that use the address of the leftmost or "big end" byte as the word address versus those that use the rightmost or "little end" byte. MIPS is in the *Big Endian* camp. (Appendix A, page A-43, shows the two options to number bytes in a word.)

Byte addressing also affects the array index. To get the proper byte address in the code above, the offset to be added to the base register \$s3 must be  $4 \times 8$ , or 32, so that the load address will select A[8] and not A[8/4]. (See the related pitfall of page 144 of Section 2.17.)

**FIGURE 2.3** Actual MIPS memory addresses and contents of memory for those words. The changed addresses are highlighted to contrast with Figure 2.2. Since MIPS addresses each byte, word addresses are multiples of four: there are four bytes in a word.

The instruction complementary to load is traditionally called *store*; it copies data from a register to memory. The format of a store is similar to that of a load: the name of the operation, followed by the register to be stored, then offset to select the array element, and finally the base register. Once again, the MIPS address is specified in part by a constant and in part by the contents of a register. The actual MIPS name is SW, standing for *store word*.

#### **Compiling Using Load and Store**

Assume variable h is associated with register \$52 and the base address of the array A is in \$53. What is the MIPS assembly code for the C assignment statement below?

```

A[12] = h + A[8];

```

Although there is a single operation in the C statement, now two of the operands are in memory, so we need even more MIPS instructions. The first two instructions are the same as the prior example, except this time we use the proper offset for byte addressing in the load word instruction to select A[8], and the add instruction places the sum in \$t0:

```

1w $t0,32($s3)  # Temporary reg $t0 gets A[8]

add $t0,$s2,$t0  # Temporary reg $t0 gets h + A[8]

```

The final instruction stores the sum into A[12], using 48 as the offset and register \$ s 3 as the base register.

```

sw $t0,48($s3) # Stores h + A[8] back into A[12]

```

#### **Constant or Immediate Operands**

Many times a program will use a constant in an operation—for example, incrementing an index to point to the next element of an array. In fact, more than half of the MIPS arithmetic instructions have a constant as an operand when running the SPEC2000 benchmarks.

**EXAMPLE**

# Hardware Software Interface

Many programs have more variables than computers have registers. Consequently, the compiler tries to keep the most frequently used variables in registers and places the rest in memory, using loads and stores to move variables between registers and memory. The process of putting less commonly used variables (or those needed later) into memory is called *spilling* registers.

The hardware principle relating size and speed suggests that memory must be slower than registers since registers are smaller. This is indeed the case; data accesses are faster if data is in registers instead of memory.

Moreover, data is more useful when in a register. A MIPS arithmetic instruction can read two registers, operate on them, and write the result. A MIPS data transfer instruction only reads one operand or writes one operand, without operating on it.

Thus, MIPS registers take both less time to access *and* have higher throughput than memory—a rare combination—making data in registers both faster to access and simpler to use. To achieve highest performance, compilers must use registers efficiently.

Using only the instructions we have seen so far, we would have to load a constant from memory to use one. (The constants would have been placed in memory when the program was loaded.) For example, to add the constant 4 to register \$53, we could use the code

```

lw $t0, AddrConstant4($s1) \# $t0 = constant 4

add $s3,$s3,$t0 \# $s3 = $s3 + $t0 ($t0 == 4)

```

assuming that AddrConstant4 is the memory address of the constant 4.

An alternative that avoids the load instruction is to offer versions of the arithmetic instructions in which one operand is a constant. This quick add instruction with one constant operand is called *add immediate* or add i. To add 4 to register \$s3, we just write

```

addi $s3.$s3.4 # $s3 = $s3 + 4

```

Immediate instructions illustrate the third hardware design principle, first mentioned in the Fallacies and Pitfalls of Chapter 1:

Design Principle 3: Make the common case fast.

Constant operands occur frequently, and by including constants inside arithmetic instructions, they are much faster than if constants were loaded from memory.

#### **MIPS** operands

| Name                            | Example                      | Comments                                                                           |  |

|---------------------------------|------------------------------|------------------------------------------------------------------------------------|--|

| 32 registers                    | \$s0, \$s1, ,<br>\$t0, \$t1, | Fast locations for data. In MIPS, data must be in registers to perform arithmetic. |  |

| 32 legisters                    | \$t0,\$t1,                   |                                                                                    |  |

| -30                             | Memory[0],                   | Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so  |  |

| 2 <sup>30</sup> memory<br>words | Memory[4], ,                 | sequential word addresses differ by 4. Memory holds data structures, arrays, and   |  |

| words                           | Memory[4294967292]           | spilled registers.                                                                 |  |

#### **MIPS** assembly language

| Category      | Instruction   | Example            | Meaning                   | Comments                          |

|---------------|---------------|--------------------|---------------------------|-----------------------------------|

|               | add           | add \$s1,\$s2,\$s3 | \$s1 = \$s2 + \$s3        | Three operands; data in registers |

| Arithmetic    | subtract      | sub \$s1,\$s2,\$s3 | \$s1 = \$s2 - \$s3        | Three operands; data in registers |

|               | add immediate | addi \$s1,\$s2,100 | \$s1 = \$s2 + 100         | Used to add constants             |

| Data transfer | load word     | lw \$s1,100(\$s2)  | s1 = Memory[s2 + 100]     | Data from memory to register      |

| Data transfer | store word    | sw \$s1,100(\$s2)  | Memory[\$s2 + 100] = \$s1 | Data from register to memory      |

**FIGURE 2.4 MIPS architecture revealed through Section 2.3.** Highlighted portions show MIPS assembly language structures introduced in Section 2.3.

Figure 2.4 summarizes the portions of the symbolic representation of the MIPS instruction set described in this section. Load word and store word are the instructions that copy words between memory and registers in the MIPS architecture. Other brands of computers use instructions along with load and store to transfer data. An architecture with such alternatives is the Intel IA-32, described in Section 2.16.

Given the importance of registers, what is the rate of increase in the number of registers in a chip over time?

## Check Yourself

- 1. Very fast: They increase as fast as Moore's law, which predicts doubling the number of transistors on a chip every 18 months.

- 2. Very slow: Since programs are usually distributed in the language of the computer, there is inertia in instruction set architecture, and so the number of registers increases only as fast as new instruction sets become viable.

**Elaboration:** Although the MIPS registers in this book are 32 bits wide, there is a 64-bit version of the MIPS instruction set with 32 64-bit registers. To keep them straight, they are officially called MIPS-32 and MIPS-64. In this chapter, we use a subset of MIPS-32. Appendix D shows the differences between MIPS-32 and MIPS-64.

The MIPS offset plus base register addressing is an excellent match to structures as well as arrays, since the register can point to the beginning of the structure and the offset can select the desired element. We'll see such an example in Section 2.13.

The register in the data transfer instructions was originally invented to hold an index of an array with the offset used for the starting address of an array. Thus, the base register is also called the *index register*. Today's memories are much larger and the software model of data allocation is more sophisticated, so the base address of the array is normally passed in a register since it won't fit in the offset, as we shall see.

Section 2.4 explains that since MIPS supports negative constants, there is no need for subtract immediate in MIPS.

# 2.4

# Representing Instructions in the Computer

We are now ready to explain the difference between the way humans instruct computers and the way computers see instructions. First, let's quickly review how a computer represents numbers.

Humans are taught to think in base 10, but numbers may be represented in any base. For example, 123 base 10 = 1111011 base 2.

Numbers are kept in computer hardware as a series of high and low electronic signals, and so they are considered base 2 numbers. (Just as base 10 numbers are called *decimal* numbers, base 2 numbers are called *binary* numbers.) A single digit of a binary number is thus the "atom" of computing, since all information is composed of **binary digits** or *bits*. This fundamental building block can be one of two values, which can be thought of as several alternatives: high or low, on or off, true or false, or 1 or 0.

Instructions are also kept in the computer as a series of high and low electronic signals and may be represented as numbers. In fact, each piece of an instruction can be considered as an individual number, and placing these numbers side by side forms the instruction.

Since registers are part of almost all instructions, there must be a convention to map register names into numbers. In MIPS assembly language, registers \$50 to \$57 map onto registers 16 to 23, and registers \$10 to \$17 map onto registers 8 to 15. Hence, \$50 means register 16, \$51 means register 17, \$52 means register 18,..., \$10 means register 8, \$11 means register 9, and so on. We'll describe the convention for the rest of the 32 registers in the following sections.

binary digit Also called binary bit. One of the two numbers in base 2, 0 or 1, that are the components of information.

#### Translating a MIPS Assembly Instruction into a Machine Instruction

Let's do the next step in the refinement of the MIPS language as an example. We'll show the real MIPS language version of the instruction represented symbolically as

add \$t0,\$s1,\$s2

first as a combination of decimal numbers and then of binary numbers.

The decimal representation is

| 0 | 17 | 18 | 8 | 0 | 32 |

|---|----|----|---|---|----|

Each of these segments of an instruction is called a *field*. The first and last fields (containing 0 and 32 in this case) in combination tell the MIPS computer that this instruction performs addition. The second field gives the number of the register that is the first source operand of the addition operation (17 = \$ \$ 1), and the third field gives the other source operand for the addition (18 = \$ \$ 2). The fourth field contains the number of the register that is to receive the sum (8 = \$ \$ 1). The fifth field is unused in this instruction, so it is set to 0. Thus, this instruction adds register \$ \$ 1 to register \$ 3 1 to regis

This instruction can also be represented as fields of binary numbers as opposed to decimal:

| 000000 | 10001  | 10010  | 01000  | 00000  | 100000 |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

To distinguish it from assembly language, we call the numeric version of instructions machine language and a sequence of such instructions machine code.

This layout of the instruction is called the **instruction format**. As you can see from counting the number of bits, this MIPS instruction takes exactly 32 bits—the same size as a data word. In keeping with our design principle that simplicity favors regularity, all MIPS instructions are 32 bits long.

It would appear that you would now be reading and writing long, tedious strings of binary numbers. We avoid that tedium by using a higher base than binary that con**EXAMPLE**

**ANSWER**

machine language Binary representation used for communication within a computer system.

instruction format A form of representation of an instruction composed of fields of binary numbers.

| Hexadecimal      | Binary              | Hexadecimal      | Binary              | Hexadecimal      | Binary              | Hexadecimal      | Binary              |

|------------------|---------------------|------------------|---------------------|------------------|---------------------|------------------|---------------------|

| O <sub>hex</sub> | 0000 <sub>two</sub> | 4 <sub>hex</sub> | 0100 <sub>two</sub> | 8 <sub>hex</sub> | 1000 <sub>two</sub> | C <sub>hex</sub> | 1100 <sub>two</sub> |

| 1 <sub>hex</sub> | 0001 <sub>two</sub> | 5 <sub>hex</sub> | 0101 <sub>two</sub> | 9 <sub>hex</sub> | 1001 <sub>two</sub> | d <sub>hex</sub> | 1101 <sub>two</sub> |

| 2 <sub>hex</sub> | 0010 <sub>two</sub> | 6 <sub>hex</sub> | 0110 <sub>two</sub> | a <sub>hex</sub> | 1010 <sub>two</sub> | e <sub>hex</sub> | $1110_{two}$        |

| 3 <sub>hex</sub> | 0011 <sub>two</sub> | 7 <sub>hex</sub> | 0111 <sub>two</sub> | b <sub>hex</sub> | 1011 <sub>two</sub> | f <sub>hex</sub> | 1111 <sub>two</sub> |

**FIGURE 2.5** The hexadecimal-binary conversion table. Just replace one hexadecimal digit by the corresponding four binary digits, and vice versa. If the length of the binary number is not a multiple of 4, go from right to left.

hexadecimal Numbers in base 16.

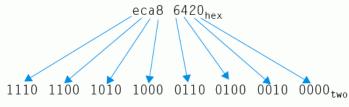

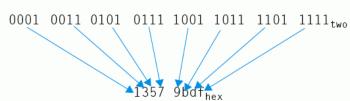

verts easily into binary. Since almost all computer data sizes are multiples of 4, hexadecimal (base 16) numbers are popular. Since base 16 is a power of 2, we can trivially convert by replacing each group of four binary digits by a single hexadecimal digit, and vice versa. Figure 2.5 converts hexadecimal to binary, and vice versa.

Because we frequently deal with different number bases, to avoid confusion we will subscript decimal numbers with *ten*, binary numbers with *two*, and hexadecimal numbers with *hex*. (If there is no subscript, the default is base 10.) By the way, C and Java use the notation 0xnnnn for hexadecimal numbers.

### **EXAMPLE**

#### **ANSWER**

#### **Binary-to-Hexadecimal and Back**

Convert the following hexadecimal and binary numbers into the other base:  $eca8 6420_{hex}$

0001 0011 0101 0111 1001 1011 1101 1111<sub>two</sub>

Just a table lookup one way:

And then the other direction too:

#### **MIPS Fields**

MIPS fields are given names to make them easier to discuss:

| ор     | rs     | rt     | rd     | shamt  | funct  |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

Here is the meaning of each name of the fields in MIPS instructions:

- op: Basic operation of the instruction, traditionally called the opcode.

- rs: The first register source operand.

- rt: The second register source operand.

- rd: The register destination operand. It gets the result of the operation.

- *shamt:* Shift amount. (Section 2.5 explains shift instructions and this term; it will not be used until then, and hence the field contains zero.)

- *funct:* Function. This field selects the specific variant of the operation in the op field and is sometimes called the *function code*.

A problem occurs when an instruction needs longer fields than those shown above. For example, the load word instruction must specify two registers and a constant. If the address were to use one of the 5-bit fields in the format above, the constant within the load word instruction would be limited to only 2<sup>5</sup> or 32. This constant is used to select elements from arrays or data structures, and it often needs to be much larger than 32. This 5-bit field is too small to be useful.

Hence, we have a conflict between the desire to keep all instructions the same length and the desire to have a single instruction format. This leads us to the final hardware design principle:

Design Principle 4: Good design demands good compromises.

The compromise chosen by the MIPS designers is to keep all instructions the same length, thereby requiring different kinds of instruction formats for different kinds of instructions. For example, the format above is called *R-type* (for register) or *R-format*. A second type of instruction format is called *I-type* (for immediate) or *I-format* and is used by the immediate and data transfer instructions. The fields of I-format are

| ор     | rs     | rt     | constant or address |

|--------|--------|--------|---------------------|

| 6 bits | 5 bits | 5 bits | 16 bits             |

**opcode** The field that denotes the operation and format of an instruction.

The 16-bit address means a load word instruction can load any word within a region of  $\pm 2^{15}$  or 32,768 bytes ( $\pm 2^{13}$  or 8192 words) of the address in the base register rs. Similarly, add immediate is limited to constants no larger than  $\pm 2^{15}$ . (Chapter 3 explains how to represent negative numbers.) We see that more than 32 registers would be difficult in this format, as the rs and rt fields would each need another bit, making it harder to fit everything in one word.

Let's look at the load word instruction from page 57:

```

lw $t0,32($s3)  # Temporary reg $t0 gets A[8]

```

Here, 19 (for \$\$3) is placed in the rs field, 8 (for \$\$t0) is placed in the rt field, and 32 is placed in the address field. Note that the meaning of the rt field has changed for this instruction: in a load word instruction, the rt field specifies the *destination* register, which receives the result of the load.

Although multiple formats complicate the hardware, we can reduce the complexity by keeping the formats similar. For example, the first three fields of the R-type and I-type formats are the same size and have the same names; the fourth field in I-type is equal to the length of the last three fields of R-type.

In case you were wondering, the formats are distinguished by the values in the first field: each format is assigned a distinct set of values in the first field (op) so that the hardware knows whether to treat the last half of the instruction as three fields (R-type) or as a single field (I-type). Figure 2.6 shows the numbers used in each field for the MIPS instructions covered through Section 2.3.

| Instruction     | Format | ор                | rs  | rt  | rd   | shamt | funct             | address  |

|-----------------|--------|-------------------|-----|-----|------|-------|-------------------|----------|

| add             | R      | 0                 | reg | reg | reg  | 0     | 32 <sub>ten</sub> | n.a.     |

| sub (subtract)  | R      | 0                 | reg | reg | reg  | 0     | 34 <sub>ten</sub> | n.a.     |

| addimmediate    | I      | 8 <sub>ten</sub>  | reg | reg | n.a. | n.a.  | n.a.              | constant |

| l w (load word) | I      | 35 <sub>ten</sub> | reg | reg | n.a. | n.a.  | n.a.              | address  |

| SW (store word) | I      | 43 <sub>ten</sub> | reg | reg | n.a. | n.a.  | n.a.              | address  |

**FIGURE 2.6** MIPS instruction encoding. In the table above, "reg" means a register number between 0 and 31, "address" means a 16-bit address, and "n.a." (not applicable) means this field does not appear in this format. Note that add and sub instructions have the same value in the op field; the hardware uses the funct field to decide the variant of the operation: add (32) or subtract (34).

#### Translating MIPS Assembly Language into Machine Language

We can now take an example all the way from what the programmer writes to what the computer executes. If \$t1 has the base of the array A and \$s2 corresponds to h, the assignment statement

A[300] = h + A[300];

is compiled into

SW

```

$t0,1200($t1) # Temporary reg $t0 gets A[300]

1w

add $t0,$s2,$t0

# Temporary reg $t0 gets h + A[300]

t0,1200(t1) # Stores h + A[300] back into A[300]

```

What is the MIPS machine language code for these three instructions?

For convenience, let's first represent the machine language instructions using decimal numbers. From Figure 2.6, we can determine the three machine language instructions:

| ор | rs | rt | rd | address/<br>shamt | funct |

|----|----|----|----|-------------------|-------|

| 35 | 9  | 8  |    | 1200              |       |

| 0  | 18 | 8  | 8  | 0                 | 32    |

| 43 | 9  | 8  |    | 1200              |       |

The 1w instruction is identified by 35 (see Figure 2.6) in the first field (op). The base register 9 (\$t1) is specified in the second field (rs), and the destination register 8 (\$t0) is specified in the third field (rt). The offset to select A[300] (1200 =  $300 \times 4$ ) is found in the final field (address).

The add instruction that follows is specified with 0 in the first field (op) and 32 in the last field (funct). The three register operands (18, 8, and 8) are found in the second, third, and fourth fields and correspond to \$52, \$t0, and \$t0.

**EXAMPLE**

The sw instruction is identified with 43 in the first field. The rest of this final instruction is identical to the lw instruction.

The binary equivalent to the decimal form is the following (1200 in base 10 is 0000 0100 1011 0000 base 2):

| 100011 | 01001 | 01000 | 000   | 0 0100 1011 0 | 000    |

|--------|-------|-------|-------|---------------|--------|

| 000000 | 10010 | 01000 | 01000 | 00000         | 100000 |

| 101011 | 01001 | 01000 | 000   | 0 0100 1011 0 | 000    |

Note the similarity of the binary representations of the first and last instructions. The only difference is in the third bit from the left.

Figure 2.7 summarizes the portions of MIPS assembly language described in this section. As we shall see in Chapters 5 and 6, the similarity of the binary representations of related instructions simplifies hardware design. These instructions are another example of regularity in the MIPS architecture.

## Check Yourself

Why doesn't MIPS have a subtract immediate instruction?

- 1. Negative constants appear much less frequently in C and Java, so they are not the common case and do not merit special support.

- 2. Since the immediate field holds both negative and positive constants, add immediate with a negative number is equivalent to subtract immediate with a positive number, so subtract immediate is superfluous.

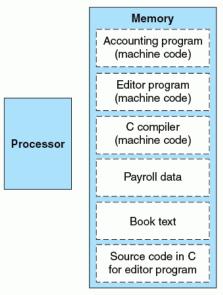

Today's computers are built on two key principles:

- Instructions are represented as numbers.

- 2. Programs are stored in memory to be read or written, just like numbers.

These principles lead to the *stored-program* concept; its invention let the computing genie out of its bottle. Figure 2.8 shows the power of the concept; specifically, memory can contain the source code for an editor program, the corresponding compiled machine code, the text that the compiled program is using, and even the compiler that generated the machine code.

One consequence of instructions as numbers is that programs are often shipped as files of binary numbers. The commercial implication is that computers can inherit ready-made software provided they are compatible with an existing instruction set. Such "binary compatibility" often leads industry to align around a small number of instruction set architectures.

#### MIPS operands

| Name                               | Example                                          | Comments                                                                                                                                                                              |

|------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32<br>registers                    | \$s0, \$s1,, \$s7<br>\$t0, \$t1,, \$t7           | Fast locations for data. In MIPS, data must be in registers to perform arithmetic. Registers $$50-\$57$ map to $16-23$ and $$t0-\$t7$ map to $8-15$ .                                 |

| 2 <sup>30</sup><br>memory<br>words | Memory[0],<br>Memory[4], ,<br>Memory[4294967292] | Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so sequential word addresses differ by 4. Memory holds data structures, arrays, and spilled registers. |

#### MIPS assembly language

| Category         | Instruction | Example            | Meaning                   | Comments                          |

|------------------|-------------|--------------------|---------------------------|-----------------------------------|

| Arithmetic       | add         | add \$s1,\$s2,\$s3 | \$s1 = \$s2 + \$s3        | Three operands; data in registers |

|                  | subtract    | sub \$s1,\$s2,\$s3 | \$s1 = \$s2 - \$s3        | Three operands; data in registers |

| Data<br>transfer | load word   | lw \$s1,100(\$s2)  | \$s1 = Memory[\$s2 + 100] | Data from memory to register      |

|                  | store word  | sw \$s1,100(\$s2)  | Memory[\$s2 + 100] = \$s1 | Data from register to memory      |

#### MIPS machine language

| Name       | Format | Example |        |        |                |        | Comments |                               |

|------------|--------|---------|--------|--------|----------------|--------|----------|-------------------------------|

| add        | R      | 0       | 18     | 19     | 17             | 0      | 32       | add \$s1,\$s2,\$s3            |

| sub        | R      | 0       | 18     | 19     | 17             | 0      | 34       | sub \$s1,\$s2,\$s3            |

| addi       | I      | 8       | 18     | 17     | 100            |        |          | addi \$s1,\$s2,100            |

| 1w         | I      | 35      | 18     | 17     | 100            |        |          | lw \$s1,100(\$s2)             |

| SW         | I      | 43      | 18     | 17     | 100            |        |          | sw \$s1,100(\$s2)             |

| Field size |        | 6 bits  | 5 bits | 5 bits | 5 bits         | 5 bits | 6 bits   | All MIPS instructions 32 bits |

| R-format   | R      | ор      | rs     | rt     | rd shamt funct |        | funct    | Arithmetic instruction format |

| l-format   | 1      | ор      | rs     | rt     | address        |        | •        | Data transfer format          |

**FIGURE 2.7 MIPS architecture revealed through Section 2.4.** Highlighted portions show MIPS machine language structures introduced in Section 2.4. The two MIPS instruction formats so far are R and I. The first 16 bits are the same: both contain an *op* field, giving the base operation; an *rs* field, giving one of the sources; and the *rt* field, which specifies the other source operand, except for load word, where it specifies the destination register. R-format divides the last 16 bits into an *rd* field, specifying the destination register; *shamt* field, which Section 2.5 explains; and the *funct* field, which specifies the specific operation of R-format instructions. I-format keeps the last 16 bits as a single *address* field.

**Elaboration:** Representing decimal numbers in base 2 gives an easy way to represent positive integers in computer words. Chapter 3 explains how to represent negative numbers, but for now take it on faith that a 32-bit word can represent integers between  $-2^{31}$  and  $+2^{31}-1$  or -2,147,483,648 to +2,147,483,647, and the 16-bit constant field really holds  $-2^{15}$  to  $+2^{15}-1$  or -32,768 to 32,767. Such integers are called *two's complement* numbers. Chapter 3 shows how we would encode addi t0,t0,t0,-1 or t0,t0,-1 or t0,t0,t0,t0, which require negative numbers in the constant field of the immediate format.

**FIGURE 2.8** The stored-program concept. Stored programs allow a computer that performs accounting to become, in the blink of an eye, a computer that helps an author write a book. The switch happens simply by loading memory with programs and data and then telling the computer to begin executing at a given location in memory. Treating instructions in the same way as data greatly simplifies both the memory hardware and the software of computer systems. Specifically, the memory technology needed for data can also be used for programs, and programs like compilers, for instance, can translate code written in a notation far more convenient for humans into code that the computer can understand.

"Contrariwise," continued Tweedledee, "if it was so, it might be; and if it were so, it would be; but as it isn't, it ain't. That's logic."

Lewis Carroll, Alice's Adventures in Wonderland, 1865

# 2.5

# **Logical Operations**

Although the first computers concentrated on full words, it soon became clear that it was useful to operate on fields of bits within a word or even on individual bits. Examining characters within a word, each of which are stored as 8 bits, is one example of such an operation. It follows that instructions were added to simplify, among other things, the packing and unpacking of bits into words. These instructions are called logical operations. Figure 2.9 shows logical operations in C and Java.

2.5 Logical Operations 69

| Logical operations | C operators | Java operators | MIPS instructions |

|--------------------|-------------|----------------|-------------------|

| Shift left         | <<          | <<             | sll               |

| Shift right        | >>          | >>>            | srl               |

| Bit-by-bit AND     | &           | &              | and, andi         |

| Bit-by-bit OR      |             |                | or, ori           |

| Bit-by-bit NOT     | ~           | ~              | nor               |

FIGURE 2.9 C and Java logical operators and their corresponding MIPS instructions.

The first class of such operations is called *shifts*. They move all the bits in a word to the left or right, filling the emptied bits with 0s. For example, if register \$50 contained

and the instruction to shift left by 4 was executed, the new value would look like this:

The dual of a shift left is a shift right. The actual name of the two MIPS shift instructions are called *shift left logical* (sll) and *shift right logical* (srl). The following instruction performs the operation above, assuming that the result should go in register \$t2:

$$$11 $t2,$s0,4 # reg $t2 = reg $s0 << 4 bits$$

We delayed explaining the *shamt* field in the R-format. It stands for *shift* amount and is used in shift instructions. Hence, the machine language version of the instruction above is

| op | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

| 0  | 0  | 16 | 10 | 4     | 0     |

The encoding of sll is 0 in both the op and funct fields, rd contains \$t2, rt contains \$s0, and shamt contains 4. The rs field is unused, and thus is set to 0.

Shift left logical provides a bonus benefit. Shifting left by i bits gives the same result as multiplying by  $2^i$  (Chapter 3 explains why). For example, the above sll shifts by 4, which gives the same result as multiplying by  $2^4$  or 16.

The first bit pattern above represents 9, and  $9 \times 16 = 144$ , the value of the second bit pattern.

Another useful operation that isolates fields is *AND*. (We capitalize the word to avoid confusion between the operation and the English conjunction.) AND is a bit-by-bit operation that leaves a 1 in the result only if both bits of the operands are 1. For example, if register \$t2 still contains

$000000000000000000000110100000000_{two}$

and register \$t1 contains

$0000000000000000000111100000000000_{two}$

then, after executing the MIPS instruction

and \$t0,\$t1,\$t2 # reg \$t0 = reg \$t1 & reg \$t2

the value of register \$t0 would be

As you can see, AND can apply a bit pattern to a set of bits to force 0s where there is a 0 in the bit pattern. Such a bit pattern in conjunction with AND is traditionally called a *mask*, since the mask "conceals" some bits.

To place a value into one of these seas of 0s, there is the dual to AND, called *OR*. It is a bit-by-bit operation that places a 1 in the result if *either* operand bit is a 1. To elaborate, if the registers \$t1 and \$t2 are unchanged from the preceding example, the result of the MIPS instruction

or \$t0,\$t1,\$t2 # reg \$t0 = reg \$t1 | reg \$t2

is this value in register \$t0:

$00000000000000000011110100000000_{two}$

The final logical operation is a contrarian. **NOT** takes one operand and places a 1 in the result if one operand bit is a 0, and vice versa. In keeping with the two-operand format, the designers of MIPS decided to include the instruction **NOR** (NOT OR) instead of NOT. If one operand is zero, then it is equivalent to NOT. For example, A NOR 0 = NOT (A OR 0 = NOT (A).

If the register \$t1 is unchanged from the preceding example and register \$t3 has the value 0, the result of the MIPS instruction

nor  $t0,t1,t3 \# reg t0 = \sim (reg t1 | reg t3)$

NOT A logical bit-by-bit operation with one operand that inverts the bits; that is, it replaces every 1 with a 0, and every 0 with a 1.

NOR A logical bit-by-bit operation with two operands that calculates the NOT of the OR of the two operands.

2.5 Logical Operations 71

is this value in register \$t0:

Figure 2.9 above shows the relationship between the C and Java operators and the MIPS instructions. Constants are useful in AND and OR logical operations as well as in arithmetic operations, so MIPS also provides the instructions *and immediate* (andi) and *or immediate* (ori). Constants are rare for NOR, since its main use is to invert the bits of a single operand; thus, the hardware has no immediate version. Figure 2.10, which summarizes the MIPS instructions seen thus far, highlights the logical instructions.

#### MIPS operands

| Name            | Example            | Comments                                                                           |

|-----------------|--------------------|------------------------------------------------------------------------------------|

| 32              | \$s0, \$s1,,\$s7   | Fast locations for data. In MIPS, data must be in registers to perform arithmetic. |

| registers       | \$t0,\$t1,,\$t7    | Registers \$s0-\$s7 map to 16–23 and \$t0-\$t7 map to 8–15.                        |

| 2 <sup>30</sup> | Memory[0],         | Accessed only by data transfer instructions. MIPS uses byte addresses, so          |

| memory          | Memory[4], ,       | sequential word addresses differ by 4. Memory holds data structures, arrays, and   |

| words           | Memory[4294967292] | spilled registers.                                                                 |

#### MIPS assembly language

| Category   | Instruction         | Example |                | Meaning                       | Comments                            |

|------------|---------------------|---------|----------------|-------------------------------|-------------------------------------|

| Arithmetic | add                 | add     | \$s1,\$s2,\$s3 | \$s1 = \$s2 + \$s3            | Three operands; overflow detected   |

|            | subtract            | sub     | \$s1,\$s2,\$s3 | \$s1 = \$s2 - \$s3            | Three operands; overflow detected   |

|            | add immediate       | addi    | \$s1,\$s2,100  | \$s1 = \$s2 + 100             | + constant; overflow detected       |

|            | and                 | and     | \$s1,\$s2,\$s3 | \$s1 = \$s2 & \$s3            | Three reg. operands; bit-by-bit AND |

|            | or                  | or      | \$s1,\$s2,\$s3 | \$s1 = \$s2   \$s3            | Three reg. operands; bit-by-bit OR  |

|            | nor                 | nor     | \$s1,\$s2,\$s3 | \$s1 = ~ (\$s2  \$s3)         | Three reg. operands; bit-by-bit NOR |

| Logical    | and immediate       | andi    | \$s1,\$s2,100  | \$s1 = \$s2 & 100             | Bit-by-bit AND reg with constant    |

|            | or immediate        | ori     | \$s1,\$s2,100  | \$s1 = \$s2   100             | Bit-by-bit OR reg with constant     |

|            | shift left logical  | sll     | \$s1,\$s2,10   | \$s1 = \$s2 << <b>10</b>      | Shift left by constant              |

|            | shift right logical | srl     | \$\$s1,\$s2,10 | \$s1 = \$s2 >> <b>10</b>      | Shift right by constant             |

| Data       | load word           | lw      | \$s1,100(\$s2) | \$s1 = Memory[\$s2 + 100]     | Word from memory to register        |

| transfer   | store word          | SW      | \$s1,100(\$s2) | Memory[ $$s2 + 100$ ] = $$s1$ | Word from register to memory        |

**FIGURE 2.10** MIPS architecture revealed thus far. Color indicates the portions introduced since Figure 2.7 on page 67. The back endpapers of this book also list the MIPS machine language.

The utility of an automatic computer lies in the possibility of using a given sequence of instructions repeatedly, the number of times it is iterated being dependent upon the results of the computation. When the iteration is completed a different sequence of [instructions] is to be followed, so we must, in most cases, give two parallel trains of [instructions] preceded by an instruction as to which routine is to be followed. This choice can be made to depend upon the sign of a number (zero being reckoned as plus for machine purposes). Consequently, we introduce an [instruction] (the conditional transfer [instruction]) which will, depending on the sign of a given number, cause the proper one of two routines to be executed.

Burks, Goldstine, and von Neumann, 1947

#### **EXAMPLE**

#### **ANSWER**

# 2.6

## **Instructions for Making Decisions**

What distinguishes a computer from a simple calculator is its ability to make decisions. Based on the input data and the values created during computation, different instructions execute. Decision making is commonly represented in programming languages using the *if* statement, sometimes combined with *go to* statements and labels. MIPS assembly language includes two decision-making instructions, similar to an *if* statement with a *go to*. The first instruction is

```

beg register1, register2, L1

```

This instruction means go to the statement labeled L1 if the value in register1 equals the value in register2. The mnemonic beq stands for *branch if equal*. The second instruction is

```

bne register1, register2, L1

```

It means go to the statement labeled L1 if the value in register1 does *not* equal the value in register2. The mnemonic bne stands for *branch if not equal*. These two instructions are traditionally called **conditional branches**.

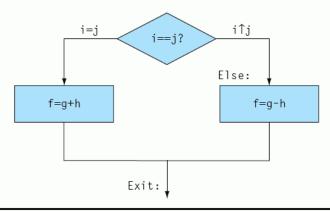

#### Compiling if-then-else into Conditional Branches

In the following code segment, f, g, h, i, and j are variables. If the five variables f through j correspond to the five registers \$50 through \$54, what is the compiled MIPS code for this C *if* statement?

```

if (i == j) f = q + h; else f = q - h;

```

Figure 2.11 is a flowchart of what the MIPS code should do. The first expression compares for equality, so it would seem that we would want beq. In general, the code will be more efficient if we test for the opposite condition to branch over the code that performs the subsequent *then* part of the *if* (the label Else is defined below):.

```

bne $s3,$s4,Else \# go to Else if i \neq j

```

The next assignment statement performs a single operation, and if all the operands are allocated to registers, it is just one instruction:

```

add s0,s1,s2 # f = g + h (skipped if i \neq j)

```

We now need to go to the end of the *if* statement. This example introduces another kind of branch, often called an *unconditional branch*. This instruction says that the processor always follows the branch. To distinguish between conditional and unconditional branches, the MIPS name for this type of instruction is *jump*, abbreviated as j (the label Exit is defined below).

```

j Exit # go to Exit

```

The assignment statement in the *else* portion of the *if* statement can again be compiled into a single instruction. We just need to append the label Else to this instruction. We also show the label Exit that is after this instruction, showing the end of the *if-then-else* compiled code:

```

Else:sub s0,s1,s2 # f = g - h (skipped if i = j) Exit:

```

Notice that the assembler relieves the compiler and the assembly language programmer from the tedium of calculating addresses for branches, just as it does for calculating data addresses for loads and stores (see Section 2.10).

**FIGURE 2.11 Illustration of the options in the** *if* **statement above.** The left box corresponds to the *then* part of the *if* statement, and the right box corresponds to the *else* part.

conditional branch An instruction that requires the comparison of two values and that allows for a subsequent transfer of control to a new address in the program based on the outcome of the comparison.

# Hardware Software Interface

Compilers frequently create branches and labels where they do not appear in the programming language. Avoiding the burden of writing explicit labels and branches is one benefit of writing in high-level programming languages and is a reason coding is faster at that level.

#### Loops

Decisions are important both for choosing between two alternatives—found in *if* statements—and for iterating a computation—found in loops. The same assembly instructions are the building blocks for both cases.

#### EXAMPLE

#### **ANSWER**

#### Compiling a while Loop in C

Here is a traditional loop in C:

```

while (save[i] == k)

i += 1;

```

Assume that i and k correspond to registers \$53 and \$55 and the base of the array save is in \$56. What is the MIPS assembly code corresponding to this C segment?

The first step is to load <code>save[i]</code> into a temporary register. Before we can load <code>save[i]</code> into a temporary register, we need to have its address. Before we can add <code>i</code> to the base of array <code>save</code> to form the address, we must multiply the index <code>i</code> by 4 due to the byte addressing problem. Fortunately, we can use shift left logical since shifting left by 2 bits multiplies by 4 (see page 69 in Section 2.5). We need to add the label <code>Loop</code> to it so that we can branch back to that instruction at the end of the loop:

```

Loop: sll $t1,$s3,2 # Temp reg $t1 = 4 * i

```

To get the address of Save[i], we need to add \$t1 and the base of Save in \$s6:

```

add t1,t1,s6 # t1 = address of save[i]

```

Now we can use that address to load Save[i] into a temporary register:

```

1w $t0,0($t1) # Temp reg $t0 = save[i]

```

The next instruction performs the loop test, exiting if  $save[i] \neq k$ :

bne

$$t0,s5$$

, Exit # go to Exit if save[i]  $\neq k$

The next instruction adds 1 to i:

add

$$$s3.$s3.1$$

# i = i + 1

The end of the loop branches back to the *while* test at the top of the loop. We just add the Exit label after it, and we're done:

(See Exercise 2.33 for an optimization of this sequence.)

Such sequences of instructions that end in a branch are so fundamental to compiling that they are given their own buzzword: a **basic block** is a sequence of instructions without branches, except possibly at the end, and without branch targets or branch labels, except possibly at the beginning. One of the first early phases of compilation is breaking the program into basic blocks

# Hardware Software Interface

The test for equality or inequality is probably the most popular test, but sometimes it is useful to see if a variable is less than another variable. For example, a *for* loop may want to test to see if the index variable is less than 0. Such comparisons are accomplished in MIPS assembly language with an instruction that compares two registers and sets a third register to 1 if the first is less than the second; otherwise, it is set to 0. The MIPS instruction is called set on less than, or slt. For example,

means that register \$t0 is set to 1 if the value in register \$s3 is less than the value in register \$s4; otherwise, register \$t0 is set to 0.

Constant operands are popular in comparisons. Since register \$zero always has 0, we can already compare to 0. To compare to other values, there is an immediate version of the set on less than instruction. To test if register \$s2 is less than the constant 10, we can just write

$$t0.$$

\$1ti  $t0.$ \$2.10 #  $t0 = 1$  if  $t0 < t0$

Heeding von Neumann's warning about the simplicity of the "equipment," the MIPS architecture doesn't include branch on less than because it is too complicated; either it would stretch the clock cycle time or it would take extra clock cycles per instruction. Two faster instructions are more useful.

basic block A sequence of instructions without branches (except possibly at the end) and without branch targets or branch labels (except possibly at the beginning).

# Hardware Software Interface

MIPS compilers use the slt, slti, beq, bne, and the fixed value of 0 (always available by reading register \$zero) to create all relative conditions: equal, not equal, less than, less than or equal, greater than, greater than or equal. (As you might expect, register \$zero maps to register 0.)

### **Case/Switch Statement**

Most programming languages have a *case* or *switch* statement that allows the programmer to select one of many alternatives depending on a single value. The simplest way to implement *switch* is via a sequence of conditional tests, turning the *switch* statement into a chain of *if-then-else* statements.

Sometimes the alternatives may be more efficiently encoded as a table of addresses of alternative instruction sequences, called a **jump address table**, and the program needs only to index into the table and then jump to the appropriate sequence. The jump table is then just an array of words containing addresses that correspond to labels in the code. See the In More Depth exercises in Section 2.20 for more details on jump address tables.

To support such situations, computers like MIPS include a *jump register* instruction (jr), meaning an unconditional jump to the address specified in a register. The program loads the appropriate entry from the jump table into a register, and then it jumps to the proper address using a jump register. This instruction is described in Section 2.7.

jump address table Also called jump table. A table of addresses of alternative instruction sequences.

# Hardware Software Interface

Although there are many statements for decisions and loops in programming languages like C and Java, the bedrock statement that implements them at the next lower level is the conditional branch.

Figure 2.12 summarizes the portions of MIPS assembly language described in this section, and Figure 2.13 summarizes the corresponding MIPS machine language. This step along the evolution of the MIPS language has added branches and jumps to our symbolic representation, and fixes the useful value 0 permanently in a register.

**Elaboration:** If you have heard about *delayed branches*, covered in Chapter 6, don't worry: The MIPS assembler makes them invisible to the assembly language programmer.