## Clock Signals and Clocked Flip-Flops

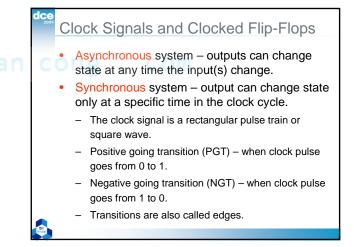

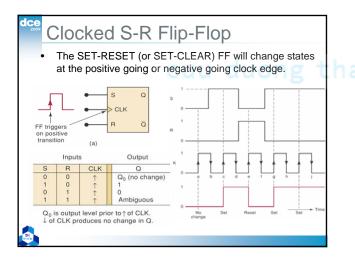

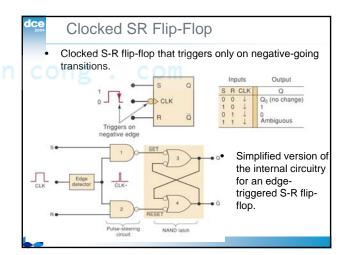

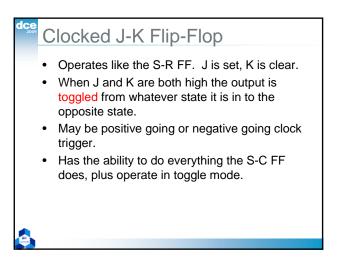

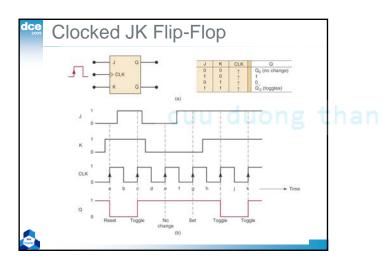

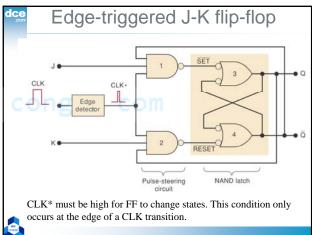

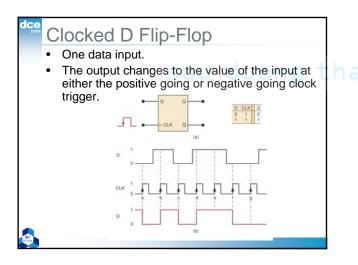

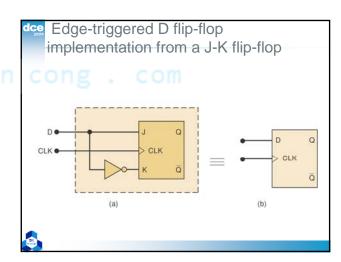

- Clocked FFs change state on one or the other clock transitions. Some common characteristics:

- Clock inputs are labeled CLK, CK, or CP.

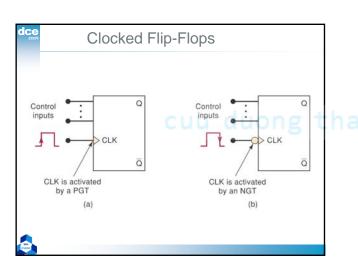

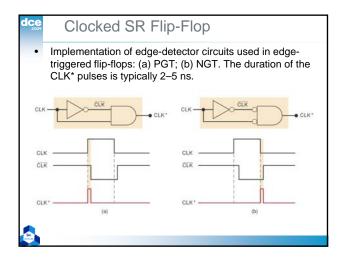

- A small triangle at the CLK input indicates that the input is activated with a PGT.

- A bubble and a triangle indicates that the CLK input is activated with a NGT.

- Control inputs have an effect on the output only at the active clock transition (NGT or PGT). These are also called synchronous control inputs.

- The control inputs get the FF outputs ready to change, but the change is not triggered until the CLK edge.

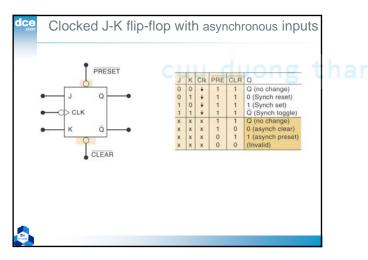

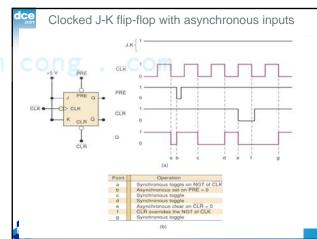

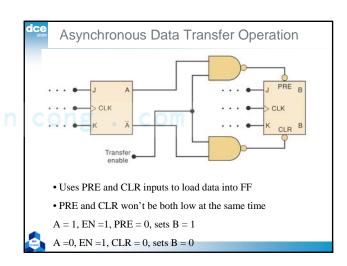

Asynchronous Inputs

Inputs that depend on the clock are synchronous.

Most clocked FFs have asynchronous inputs that do not depend on the clock.

The labels PRE and CLR are used for asynchronous inputs.

Active low asynchronous inputs will have a bar over the labels and inversion bubbles.

If the asynchronous inputs are not used they will be tied to their inactive state.

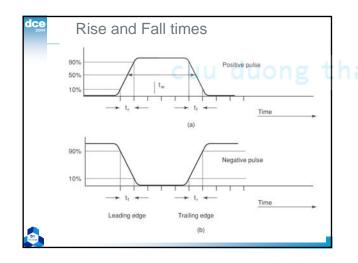

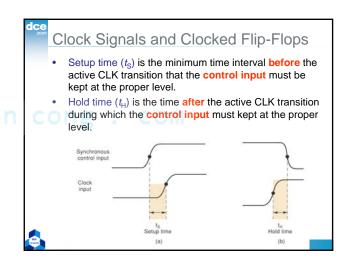

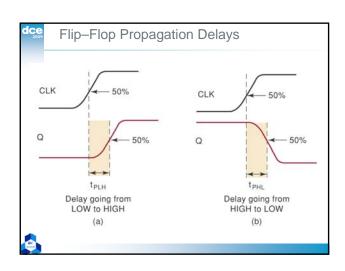

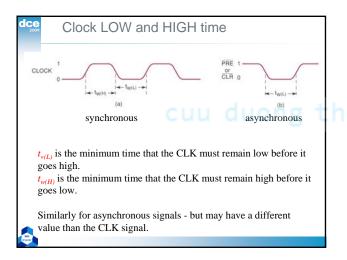

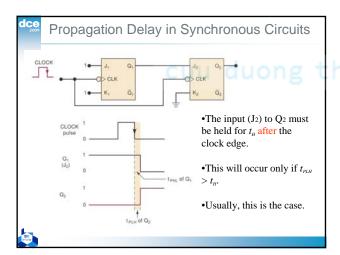

## Flip-Flop Timing Considerations Important timing parameters: Setup and hold times Propagation delay: the time for a signal at the input to be shown at the output. Maximum clocking frequency: highest clock frequency that will give a reliable output. Clock pulse high and low times: minimum time that the clock must be high before going low, and low before going high. Asynchronous active pulse width: the minimum time PRESET or CLEAR must be held for the FF to set or clear reliably. Clock transition times: maximum time for the clock transitions, generally less than 50 ns for TTL, or 200 ns for CMOS devices.

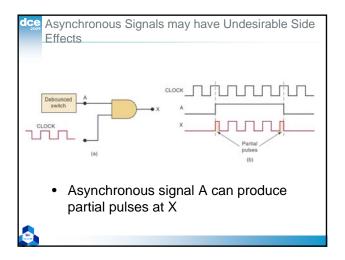

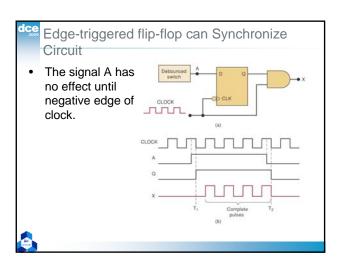

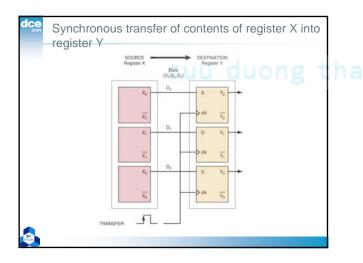

## Flip-Flop Synchronization Most systems are primarily synchronous in operation, in that changes depend on the clock. Asynchronous and synchronous operations are often combined. The random nature of asynchronous inputs can result in unpredictable results.

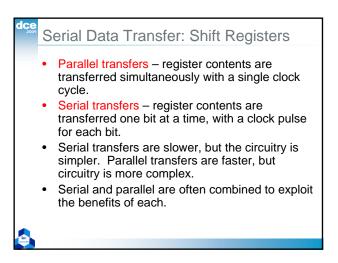

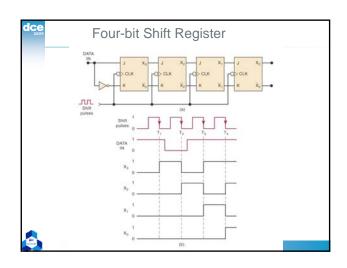

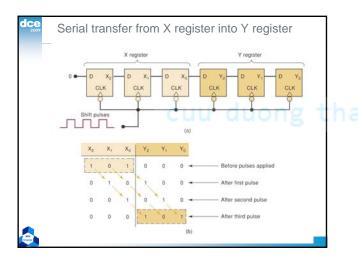

Serial Data Transfer: Shift Registers

When FFs are arranged as a shift register, bits will shift with each clock pulse.

FFs used as shift registers must have very low hold time parameters to perform predictably. Modern FFs have t<sub>H</sub> values well within what is required.

The direction of data shifts will depend on the circuit requirements and the design.

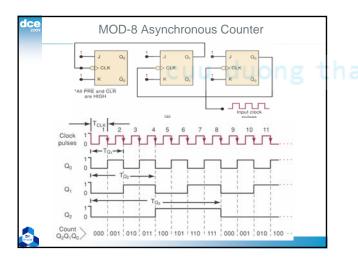

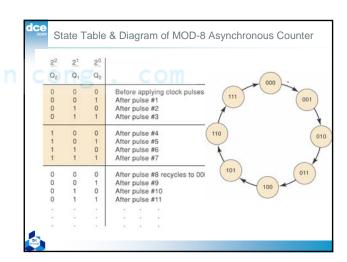

Frequency Division and Counting

FFs are often used to divide a frequency as illustrated in next slide. Here the output frequency is 1/8th the input (clock) frequency.

The same circuit is also acting as a binary counter. The outputs will count from 000<sub>2</sub> to 111<sub>2</sub>

The number of states possible in a counter is the modulus or MOD number. Next slide is a MOD-8 (2³) counter. If another FF is added it would become a MOD-16 (2⁴) counter.

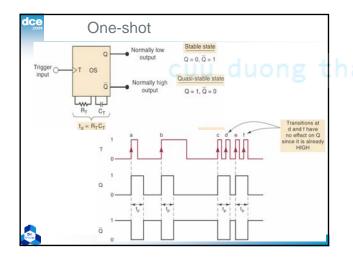

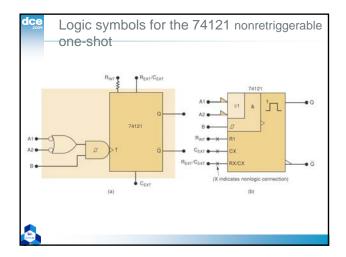

One-shot (Monostable Multivibrator)

• Changes from stable state to quasi-stable state for a period of time determined by external components (usually resistors and capacitors).

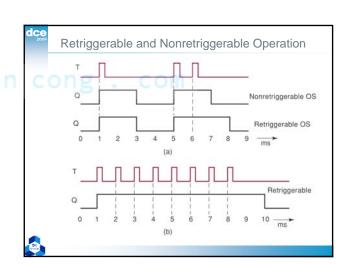

• Nonretriggerable devices will trigger and return to stable state.

• Retriggerable devices can be triggered while in the quasi-stable state to begin another pulse.

• One shots are called monostable multivibrators because they have only one stable state.

• They are prone to triggering by noise so, tend to be used in simple timing applications.

cuu duong than cong . com