CuuDuongThanCong.com

https://fb.com/tailieudientucntt

1

So what are microcontrollers?

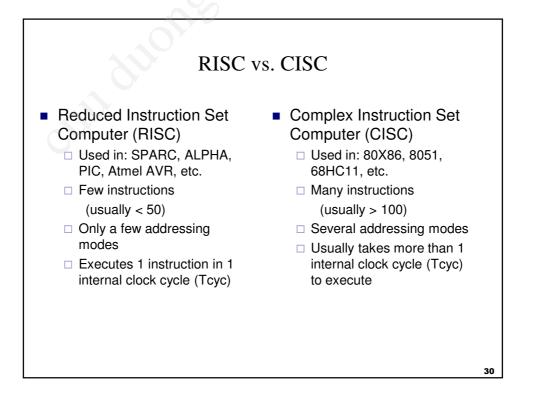

| Main 8-bit Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

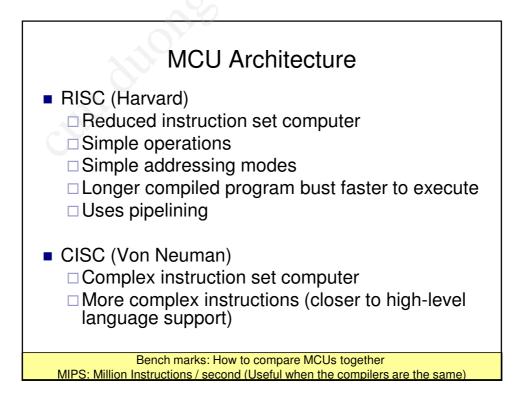

| <ul> <li>Microchip <ul> <li>RISC architecture (reduced instruction set computer)</li> <li>Has sold over 2 billion as of 2002</li> <li>Cost effective and rich in peripherals</li> </ul> </li> <li>Motorola <ul> <li>CISC architecture</li> <li>Has hundreds of instructions</li> <li>Examples: 68HC05, 68HC08, 68HC11</li> </ul> </li> <li>Intel <ul> <li>CISC architecture</li> <li>Has hundreds of instructions</li> <li>Examples: 8051, 8052</li> <li>Many difference manufacturers: Philips, Dallas/MAXIM Semiconductor, etc.</li> </ul> </li> <li>Atmel <ul> <li>RISC architecture (reduced instruction set computer) –</li> <li>Cost effective and rich in peripherals</li> <li>AVR</li> </ul> </li> </ul> |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

35

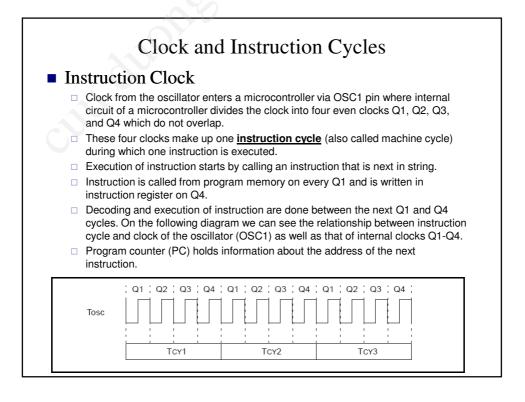

- Clock from the oscillator enters the microcontroller via OSC1 pin.

- Internal circuit divides the clock into four even clocks Q1, Q2, Q3, and Q4 which do not overlap.

- These four clocks make up one instruction cycle during which one instruction is executed.

- On the following diagram we can see the relationship between instruction cycle and clock of the oscillator (OSC1) as well as that of internal clocks Q1-Q4.

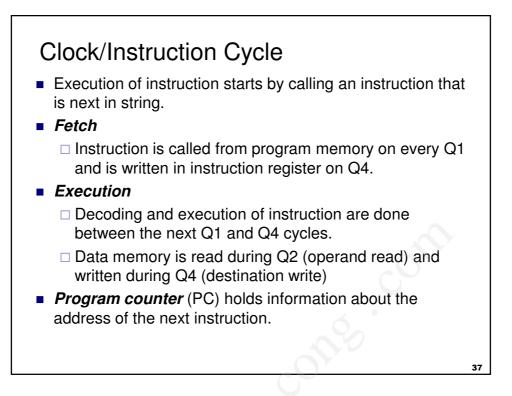

**Clock/Instruction Cycle** Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 OSC 1 Q1 Q2 Q3 Q4 PC PC PC+1 PC+2 Fetch Instruction (PC+1) Fetch Instruction (PC+2) Fetch Instruction (PC) Pipeline Execute Inst (PC-1) Execute Inst (PC) Execute Inst (PC+1)  $T_{MC1}$  $T_{MC2}$  $T_{MC3}$ Clock signals in PIC microcontrollers. OSC1 is the main oscillator from which the internal signals Q1, Q2, Q3, and Q4 are derived. These signals synchronize fetching, decode, and execute of instructions.  $T_{MC}$  is the duration of a machine cycle. It uses four OSC1 pulses. 36

| Table 2.3 PIC 16 Se   | eries instruction | n cycle dura |  |  |

|-----------------------|-------------------|--------------|--|--|

| ions for various cloo |                   | ,            |  |  |

| Clock frequency       | Instruction cycle |              |  |  |

|                       | Frequency         | Period       |  |  |

| 20 MHz                | 5 MHz             | 200 ns       |  |  |

| 4 MHz                 | 1 MHz             | 1 µs         |  |  |

| 1 MHz                 | 250 kHz           | 4 µs         |  |  |

| 32.768 kHz            | 8.192 kHz         | 122.07 µs    |  |  |

38

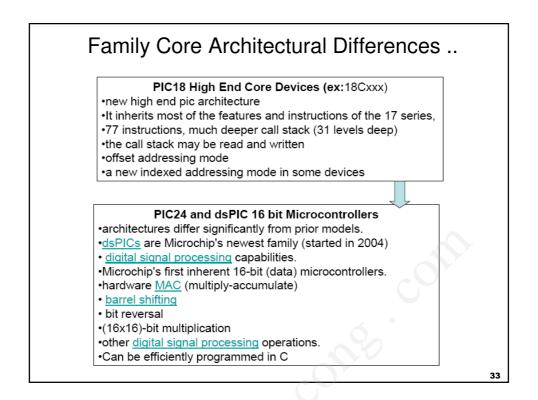

| PIC family    | Stack size (words) | Instruction<br>word size | Number of instructions             | Interrupt vector |

|---------------|--------------------|--------------------------|------------------------------------|------------------|

| 12CXXX/12FXXX | 2                  | 12- or 14-bit            | 33                                 | None             |

| 16C5XX/16F5XX | 2                  | 12-bit                   | 33                                 | None             |

| 16CXXX/16FXXX | 8                  | 14-bit                   | 35                                 | 1                |

| 17CXXX        | 16                 | 16-bit                   | 58, including hardware<br>multiply | 4                |

| 18CXXX/18FXXX | 32                 | 16-bit                   | 75, including hardware multiply    | 2 (prioritised)  |

|               |                    |                          |                                    |                  |

| Device<br>1umber | No. of pins* | Clock speed  | Memory<br>(K = Kbytes, i.e. 1024 bytes)                 | Peripherals/special features                                                                                                                                        |

|------------------|--------------|--------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6F84A            | 18           | DC to 20 MHz | 1K program memory,<br>68 bytes RAM,<br>64 bytes EEPROM  | 1 8-bit timer<br>1 5-bit parallel port<br>1 8-bit parallel port                                                                                                     |

| 6LF84A           | As above     | As above     | As above                                                | As above, with extended supply voltage range                                                                                                                        |

| 6F84A-04         | As above     | DC to 4 MHz  | As above                                                | As above                                                                                                                                                            |

| 6F873A           | 28           | DC to 20 MHz | 4K program memory<br>192 bytes RAM,<br>128 bytes EEPROM | 3 parallel ports,<br>3 counter/timers,<br>2 capture/compare/PWM<br>modules,<br>2 serial communication<br>modules,<br>5 10-bit ADC channels,<br>2 analog comparators |

| 6F874A           | 40           | DC to 20 MHz | 4K program memory<br>192 bytes RAM,<br>128 bytes EEPROM | 5 parallel ports,<br>3 counter/timers,<br>2 capture/compare/PWM<br>modules,<br>2 serial communication<br>modules,<br>8 10-bit ADC channels,<br>2 analog comparators |

|                  |              |              |                                                         |                                                                                                                                                                     |

|                  |              |              |                                                         |                                                                                                                                                                     |

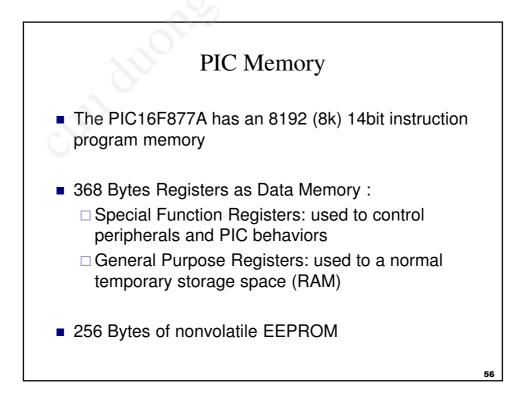

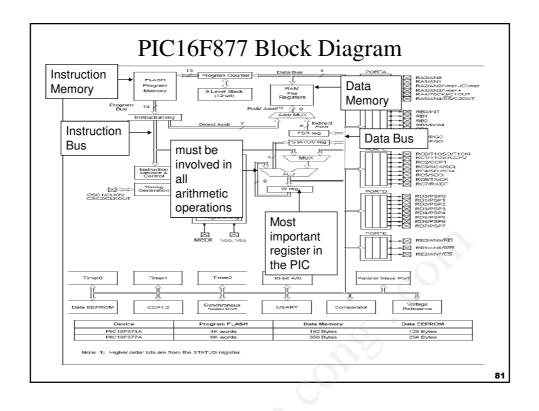

| 6F876A | 28 | DC to 20 MHz | 8K program memory<br>368 bytes RAM,<br>256 bytes EEPROM | <ul> <li>3 parallel ports,</li> <li>3 counter/timers,</li> <li>2 capture/compare/PWM modules,</li> <li>2 serial communication modules,</li> <li>5 10-bit ADC channels,</li> <li>2 analog comparators</li> </ul> |

|--------|----|--------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

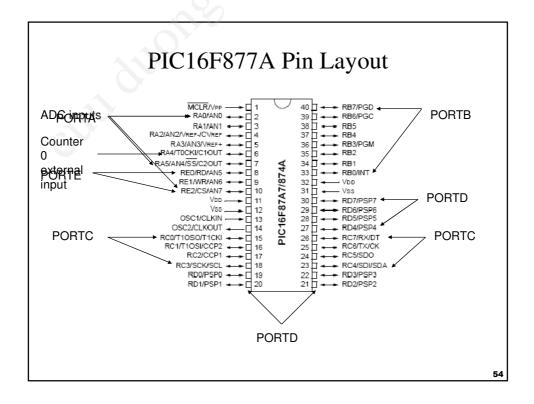

| 6F877A | 40 | DC to 20 MHz | 8K program memory<br>368 bytes RAM,<br>256 bytes EEPROM | 5 parallel ports,<br>3 counter/timers,<br>2 capture/compare/PWM<br>modules,<br>2 serial communication<br>modules,<br>8 10-bit ADC channels,<br>2 analog comparators                                             |

|                    |                                       |                    |                                       | -                  |                                      | _                  |                                      |

|--------------------|---------------------------------------|--------------------|---------------------------------------|--------------------|--------------------------------------|--------------------|--------------------------------------|

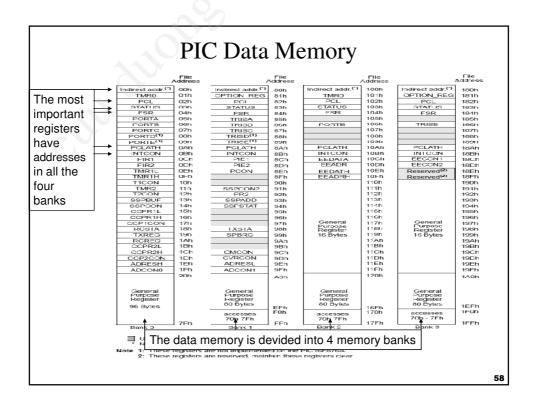

| Bank               | 0 (000 – 07F)                         | Bank               | 1 (080 – 0FF)                         | Ban                | k 2 (100-180)                        | Ban                | k 3(180-1FF)                         |

| Address            | Register                              | Address            | Register                              | Address            | Register                             | Address            | Register                             |

| 000h               | Indirect                              | 080h               | Indirect                              | 100h               | Indirect                             | 180h               | Indirect                             |

| 001h               | Timer0                                | 081h               | Option                                | 101h               | Timer0                               | 181h               | Option                               |

| 002h               | PC Low                                | 082h               | PC Low                                | 102h               | PC Low                               | 182h               | PC Low                               |

| 003h               | Status Reg                            | 083h               | Status Reg                            | 103h               | Status Reg                           | 183h               | Status Reg                           |

| 004h               | File Select                           | 084h               | File Select                           | 104h               | File Select                          | 184h               | File Select                          |

| 005h               | Port A data                           | 085h               | PortA direction                       | 105h               | -                                    | 185h               | -                                    |

| 006h               | Port B data                           | 086h               | PortB direction                       | 106h               | Port B data                          | 186h               | PortB direction                      |

| 007h               | Port C data                           | 087h               | PortC direction                       | 107h               | -                                    | 187h               | -                                    |

| 008h               | Port D data                           | 088h               | PortD direction                       | 108h               | -                                    | 188h               | -                                    |

| 009h               | Port E data                           | 089h               | PortE direction                       | 109h               | -                                    | 189h               | - /                                  |

| 00Ah               | PC High                               | 08Ah               | PC High                               | 10Ah               | PC High                              | 18Ah               | PC High                              |

| 00Bh               | Interrupt Control                     | 08Bh               | Interrupt Control                     | 10Bh               | Interrupt Control                    | 18Bh               | Interrupt Control                    |

| 00Ch<br>to<br>01Fh | 20 Peripheral<br>Control<br>Registers | 08Ch<br>to<br>09Fh | 20 Peripheral<br>Control<br>Registers | 10Ch<br>to<br>10Fh | 4 Peripheral<br>Control<br>Registers | 18Ch<br>to<br>18Fh | 4 Peripheral<br>Control<br>Registers |

| 020h<br>to<br>06Fh | 80 General<br>Purpose<br>Registers    | 0A0h<br>to<br>0EFh | 80 General<br>Purpose<br>Registers    | 110h<br>to<br>16Fh | 96 General<br>Purpose<br>Registers   | 190h<br>to<br>1EFh | 96 General<br>Purpose<br>Registers   |

| 070h<br>to<br>07Fh | 16 Common<br>Access GPRs              | 0F0h<br>to<br>0FFh | Accesses<br>70h – 7Fh                 | 170h<br>to<br>17Fh | Accesses<br>70h – 7Fh                | 1F0h<br>to<br>1FFh | Accesses<br>70h – 7Fh                |

|                  | Special Function Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                  | "STATUS Register"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                  | R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                  | IRP         RP1         RP0         TO         PD         Z         DC         C           bit 7         bit 0         bit |  |  |  |  |  |  |

| bit 7<br>bit 6-5 | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>o = Bank 0, 1 (00h - FFh)<br>RP1:RP0: Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h - 1FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| bit 4            | 10 = Bank 2 (100h - 17Fn)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes<br>TO: Time-out bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Dit 4            | <ul> <li>a After power-up, CLRWDT Instruction, or SLEEP Instruction</li> <li>o = A WDT time-out occurred</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| bit 3            | PD: Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| bit 2            | Z: Zero bit<br>1 – The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Dit 1            | DC: Digit carry/borrow bit (ADDWP, ADDLW, SUBLW, SUBWP instructions)<br>(for borrow, the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>o = No carry-out from the 4th low order bit of the result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| bit 0            | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                  | Note: For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high, or low order bit of the source register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                  | Legend:         W = Writable bit         U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                  | - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

84

| Literal and | control  | Bit-oriented        | l file register ( | operations<br>76 |                     | 0       |         |               |       |         |

|-------------|----------|---------------------|-------------------|------------------|---------------------|---------|---------|---------------|-------|---------|

|             | contro   | roperations         |                   |                  |                     |         |         |               |       |         |

| General     |          |                     |                   |                  | d Go <b>r</b> o ins |         | is only |               |       |         |

| 13          |          | 8 7                 | 0                 | 13               | 11                  | 10      |         |               |       | 0       |

| OPC         | CODE     | k (                 | literal)          | QP               | CODE                |         | k       | (literal)     |       |         |

| k = 8-ł     | hit imme | ediate value        |                   | k =              | 11-bit imn          | nediate | value   |               |       |         |

| ADDWF       | f, d     | Add W and f         |                   |                  | 1 00                | 0111    | dfff    | ff <b>f</b> f | C,DC, | Z   1,2 |

| ANDWF       | f, d     | AND W with f        |                   |                  | 1 00                | 0101    | dfff    | ff <b>f</b> f | Z     | 1,2     |

| CLRF        | f        | Clear f             |                   |                  | 1 00                | 0001    | lfff    | ff <b>f</b> f | Z.    | 2       |

| ADDLW       | k        | Add literal and W   |                   |                  | 1                   | 11      | 111x    | kkkk          | kkkk  | C,DC,Z  |

| ANDLW       | k        | AND literal with V  | /                 |                  | 1                   | 11      | 1001    | kkkk          | kkkk  | Z       |

| CALL        | k        | Call subroutine     |                   |                  | 2                   | 10      | 0kkk    |               | kkk   |         |

| CLRWDT      | -        | Clear Watchdog      | imer              |                  | 1                   | 00      | 0000    | 0110          | 0100  | TO,PD   |

| GOTO        | k        | Go to address       |                   |                  | 2                   | 10      | 1kkk    | kkkk          | kkkk  |         |

| IORLW       | k        | Inclusive OR liter  | al with W         |                  | 1                   | 11      | 1000    | kkkk          | kkkk  | Z       |

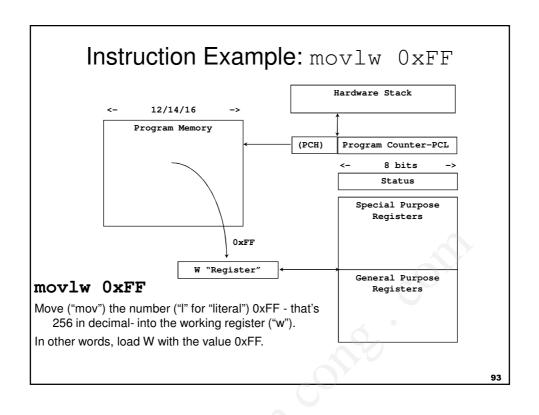

| MOVLW       | k        | Move literal to W   |                   |                  | 1                   | 11      | 00xx    | kkkk          | kkkk  |         |

| RETFIE      | -        | Return from inter   |                   |                  | 2                   |         | 0000    |               | 1001  |         |

| RETLW       | k        | Return with literal |                   |                  | 2                   | 11      | 01xx    | kkk           | kkkk  |         |

| RETURN      | -        | Return from Subr    | e anne            |                  | 2                   |         | 0000    |               | 1000  |         |

| SLEEP       | -        | Go into Standby r   |                   |                  | 1                   | 0.0     | 0000    | 0110          | 0011  | TO, PD  |

| SUBLW       | k        | Subtract W from     |                   |                  | 1                   |         |         |               | kkkk  | C,DC,Z  |

| XORLW       | k        | Exclusive OR lite   | al with W         |                  | 1                   |         | 1010    |               | kkkk  | Z       |

| SWAPF       | f, d     | Swap nibbles in f   |                   |                  | 1 00                | 1110    | dfff    | ff <b>f</b> f |       | 1,2     |

| XORWF       | f, d     | Exclusive OR W with | f                 |                  | 1 00                | 0110    | dfff    | ff <b>f</b> f | Z     | 1,2     |

|         |      | terui      |                             | muo                                                     | Instructions                                 |   |  |

|---------|------|------------|-----------------------------|---------------------------------------------------------|----------------------------------------------|---|--|

| Mnem    | onic |            | Description                 |                                                         | Function                                     |   |  |

| addlw 🔺 | k    | Add lite   | ral to W                    |                                                         | $k + W \rightarrow W$                        |   |  |

| andlw   | k    | AND lite   | eral and W                  |                                                         | $k$ .AND. $W \rightarrow W$                  |   |  |

| call    | k    | Call su    | broutine                    |                                                         | PC + 1 $\rightarrow$ TOS, k $\rightarrow$ PC |   |  |

| clrwdt  |      | Clearw     | atchdog timer               |                                                         | 0 → WDT (and prescaler if assigned)          |   |  |

| goto    | k    | Goto ac    | ldress (k is nine bi        | ts)                                                     | $k \rightarrow PC (9 \text{ bits})$          |   |  |

| iorlw   | k    | Incl. OF   | literal and W               |                                                         | $k .OR. W \rightarrow W$                     |   |  |

| movlw   | k    | Move Li    | teral to W                  |                                                         | $k \rightarrow W$                            |   |  |

| option  |      | Load O     | PTION register              |                                                         | W → OPTION Register                          |   |  |

| retfie  |      | Return     | from Interrupt              |                                                         | TOS $\rightarrow$ PC, 1 $\rightarrow$ GIE    |   |  |

| retlw   | k    | Return     | with literal in W           | h literal in W $k \rightarrow W$ , TOS $\rightarrow PC$ |                                              |   |  |

| return  |      | Return     | from subroutine             |                                                         | $TOS \rightarrow PC$                         |   |  |

| sleep   |      | Go into    | Standby Mode                |                                                         | 0 → WDT, stop oscillator                     |   |  |

| sublw   | k    | Subtrac    | t W from literal            |                                                         | $K - W \rightarrow W$                        |   |  |

| tris    | f    | Configu    | ire port f (downward co     | ompat.instr.)                                           | $W \rightarrow I/0$ control reg f            |   |  |

| xorlw   | k    | Exclusiv   | ve OR literal and W         | 1                                                       | k .XOR. W → W                                |   |  |

|         | Key: |            | -                           |                                                         |                                              | _ |  |

|         |      | Field<br>b | Bit address within an 8-1   |                                                         | ription                                      | - |  |

|         | R    |            |                             | -                                                       |                                              | _ |  |

|         |      | d          | Destination select;         | d = 0                                                   | Store result in W                            |   |  |

|         |      |            |                             | d = 1                                                   | Store result in file register f.             |   |  |

|         |      |            |                             |                                                         | Default is d = 1.                            | _ |  |

|         |      | f          | Register file address (0)   |                                                         |                                              | _ |  |

|         |      | k          | Literal field, constant dat | ta or label                                             |                                              |   |  |

| Mnen   | nonic | Description               | Function                                                                                                                            |

|--------|-------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| addwf  | f,d   | Add W and f               | $W + f \rightarrow d$                                                                                                               |

| andwf  | f,d   | AND W and f               | W .AND. $f \rightarrow d$                                                                                                           |

| clrf   | f     | Clearf                    | $0 \rightarrow f$                                                                                                                   |

| clrw   |       | Clear W                   | $0 \rightarrow W$                                                                                                                   |

| comf   | f,d   | Complement f              | .NOT. $f \rightarrow d$                                                                                                             |

| decf   | f,d   | Decrement f               | $f - \rightarrow d$                                                                                                                 |

| decfsz | f,d   | Decrement f, skip if zero | $f - 1 \rightarrow d$ , skip if 0                                                                                                   |

| ncf    | f,d   | Increment f               | $f + 1 \rightarrow d$                                                                                                               |

| ncfsz  | f,d   | Increment f, skip if zero | $f + 1 \rightarrow d$ , skip if 0                                                                                                   |

| orwf   | f,d   | Inclusive OR W and f      | W .OR. $f \rightarrow d$                                                                                                            |

| movf   | f,d   | Move f                    | $f \rightarrow d$                                                                                                                   |

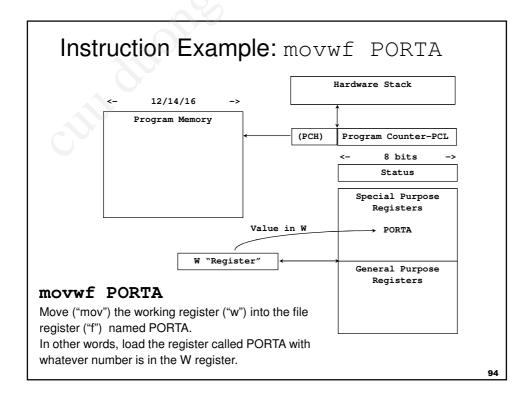

| novwf  | f     | Move W to f               | $W \rightarrow f$                                                                                                                   |

| nop    |       | No operation              |                                                                                                                                     |

| rif    | f,d   | Rotate left f             | $\begin{array}{c} \downarrow & \hline C & \leftarrow & \hline 7 & 0 & \leftarrow \\ \rightarrow & \rightarrow & \hline \end{array}$ |

| subwf  | f,d   | Subtract W from f         | $f - W \rightarrow d$                                                                                                               |

| swapf  | f,d   | Swap halves f             | $f(0:3) \leftrightarrow f(4:7) \rightarrow d$                                                                                       |

| orwf   | f,d   | Exclusive OR W and f      | $W$ XOR. $f \rightarrow d$                                                                                                          |

|        |       |                           | - 21 - COV-                                                                                                                         |

|        |      | <b>Byte-Oriented Instructions</b> |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|--------|------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        |      |                                   |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Mnem   | onic | Description                       | Function                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| addwf  | f,d  | Add W and f                       | $W + f \rightarrow d$                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| andwf  | f,d  | AND W and f                       | W .AND. $f \rightarrow d$                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| clrf   | f    | Clearf                            | $0 \rightarrow f$                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| clrw   |      | ClearW                            | $0 \rightarrow W$                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| comf   | f,d  | Complement f                      | .NOT. $f \rightarrow d$                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| decf   | f,d  | Decrement f                       | $f - \rightarrow d$                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| decfsz | f,d  | Decrement f, skip if zero         | $f - 1 \rightarrow d$ , skip if 0                                                                                                                                                                                                                                                                                                |  |  |  |  |

| incf   | f,d  | Increment f                       | $f + 1 \rightarrow d$                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| incfsz | f,d  | Increment f, skip if zero         | $f + 1 \rightarrow d$ , skip if 0                                                                                                                                                                                                                                                                                                |  |  |  |  |

| iorwf  | f,d  | Inclusive OR W and f              | W .0R. $f \rightarrow d$                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| movf   | f,d  | Move f                            | $f \rightarrow d$                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| movwf  | f    | Move W to f                       | $W \rightarrow f$                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| nop    |      | No operation                      |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| rlf    | f,d  | Rotate left f                     | $\begin{array}{c} & \text{register f} \\ \downarrow & \boxed{\text{C}} & \leftarrow & \boxed{7} & 0 \\ \rightarrow & \rightarrow & \end{array} \leftarrow$                                                                                                                                                                       |  |  |  |  |

| rrf    | f,d  | Rotate right f                    | $\rightarrow \qquad \boxed{\begin{array}{c} C \\ \hline \end{array}} \rightarrow \qquad \boxed{\begin{array}{c} 7 \\ \hline \end{array}} \qquad \boxed{\begin{array}{c} 0 \\ \leftarrow \end{array}} \qquad \underbrace{\begin{array}{c} \downarrow \\ \leftarrow \end{array}} \qquad \underbrace{\begin{array}{c} \end{array}}$ |  |  |  |  |

| subwf  | f,d  | Subtract W from f                 | $f - W \rightarrow d$                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| swapf  | f,d  | Swap halves f                     | $f(0:3) \leftrightarrow f(4:7) \rightarrow d$                                                                                                                                                                                                                                                                                    |  |  |  |  |

| xorwf  | f.d  | Exclusive OR W and f              | W XOR, $f \rightarrow d$                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|       |       | Dit Offente                    | u msu                                                     | ructions                         |  |  |  |

|-------|-------|--------------------------------|-----------------------------------------------------------|----------------------------------|--|--|--|

| Mne   | monic | Description                    |                                                           | Function                         |  |  |  |

| bcf   | f,b   | Bitclearf                      |                                                           | $0 \rightarrow f(b)$             |  |  |  |

| bsf   | f,b   | Bitsetf                        |                                                           | $1 \rightarrow f(b)$             |  |  |  |

| btfsc | f,b   |                                | Fit test, skip next instruction if clear skip if f(b) = 0 |                                  |  |  |  |

| btfss | f,b   | Bit test, skip next instructio | in if set                                                 | skip if f(b) = 1                 |  |  |  |

| F     | eld   |                                | D                                                         | escription                       |  |  |  |

|       | b     | Bit address within an 8-bi     | Bit address within an 8-bit file register                 |                                  |  |  |  |

|       | d     | Destination select;            | d = 0                                                     | Store result in W                |  |  |  |

|       |       |                                | d = 1                                                     | Store result in file register f. |  |  |  |

|       |       |                                |                                                           | Default is d = 1.                |  |  |  |

|       | f     | Register file address (0x0     | 0 to 0xFF)                                                |                                  |  |  |  |

|       | k     | Literal field, constant data   | ı or label                                                | Q                                |  |  |  |

|       | W     | Working register (accumu       | ulator)                                                   |                                  |  |  |  |

|       |       |                                |                                                           |                                  |  |  |  |

CuuDuongThanCong.com

|          | Danka        | DAMA                                                                         | Dani a                                                                                                     |                                                                                   |                                                                  | D.111.                                                                                    | DAM                                                                             | DAN                    |                                      |    |

|----------|--------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------|--------------------------------------|----|

|          | R/W-0<br>PA2 | R/W-0<br>PA1                                                                 | R/W-0<br>PA0                                                                                               | R-1<br>TO                                                                         | R-1<br>PD                                                        | R/W-x<br>Z                                                                                | R/W-x<br>DC                                                                     | R/W-x<br>C             | R = Readable bit                     |    |

|          | bit7         | 6                                                                            | 5                                                                                                          | 4                                                                                 | 3                                                                | 2                                                                                         | 1                                                                               | bit0                   | W = Writable bit                     |    |

|          | Dit          |                                                                              | 5                                                                                                          | 4                                                                                 | 5                                                                | 2                                                                                         |                                                                                 | DIED                   | - n = Value at POR reset             |    |

|          | bit 7:       | PA2: This b<br>Use of the<br>compatibilit                                    | PA2 bit as a                                                                                               | general p                                                                         | urpose rea                                                       | d/write bit is r                                                                          | not recomm                                                                      | ended, sinc            | e this may affect upward             |    |

|          | bit 6-5:     | 00 = Page<br>01 = Page<br>10 = Page<br>11 = Page<br>Each page<br>Using the F | 0 (000h - 16<br>1 (200h - 36<br>2 (400h - 56<br>3 (600h - 76<br>3 (600h - 76<br>is 512 word<br>A1:PA0 bits | Fh) - PIC<br>Fh) - PIC<br>Fh) - PIC<br>Fh) - PIC<br>Fh) - PIC<br>ds.<br>as genera | 16C56s/CR<br>16C56s/CR<br>16C57s/CR<br>16C57s/CR<br>al purpose i | 56s, PIC16C<br>56s, PIC16C<br>57s, PIC16C<br>57s, PIC16C<br>57s, PIC16C                   | 57s/CR57s,<br>57s/CR57s,<br>58s/CR58s<br>58s/CR58s<br>58s/CR58s<br>s in devices | PIC16C58<br>PIC16C58   |                                      |    |

| Register | bit 4:       | TO: Time-o<br>1 = After po<br>0 = A WDT                                      | wer-up, CL                                                                                                 |                                                                                   | uction, or S                                                     | LEEP instruc                                                                              | tion                                                                            |                        |                                      |    |

|          | bit 3:       | PD: Power-<br>1 = After po<br>0 = By exec                                    | wer-up or t                                                                                                |                                                                                   |                                                                  | tion                                                                                      |                                                                                 |                        |                                      |    |

| STATUS   | bit 2:       | Z: Zero bit<br>1 = The res<br>0 = The res                                    |                                                                                                            |                                                                                   |                                                                  | tion is zero<br>tion is not ze                                                            | ro                                                                              |                        |                                      |    |

| S        | bit 1:       | ADDWF<br>1 = A carry<br>0 = A carry<br>SUBWF<br>1 = A borro                  | from the 4t<br>from the 4t<br>w from the                                                                   | h low orde<br>h low orde<br>4th low ord                                           | r bit of the r<br>r bit of the r<br>der bit of the               | BWF instruction<br>result occurre<br>result did not<br>e result did not<br>e result occur | d<br>occur<br>ot occur                                                          |                        |                                      |    |

|          | bit 0:       | C: Carry/bc<br>ADDWF<br>1 = A carry<br>0 = A carry                           | occurred                                                                                                   |                                                                                   | SUBWF<br>1 = A bor                                               | RF, RLF instr<br>row did not o<br>row occurred                                            | ccur                                                                            | RRF or F<br>Load bit v | RLF<br>with LSb or MSb, respectively | 98 |

| Direct Addressin                                                                                                                        | ng                                               |   |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---|

| <ul> <li>All file registers (RAM) are accessed by an address. This is called <i>direct addressing</i>.</li> <li>For example,</li> </ul> | File Address                                     |   |

| movlw 0xFF<br>movwf 0x06                                                                                                                | 05h OSCCAL<br>06h GPIO<br>07h                    |   |

| <ul><li>loads W with FF, and then loads W into GPIO (address 0x06).</li><li>Thankfully, we can use labels instead of</li></ul>          | Registers<br>1Fh                                 |   |

| addresses:<br>GPIO equ 0x06<br>movwf GPIO                                                                                               | Note 1: Not a physical register. See Section 4.8 |   |

|                                                                                                                                         | 9                                                | 9 |

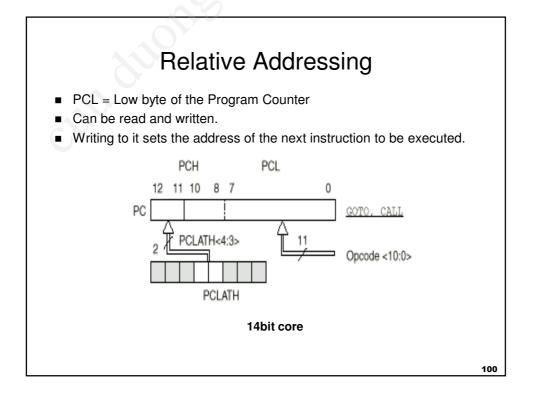

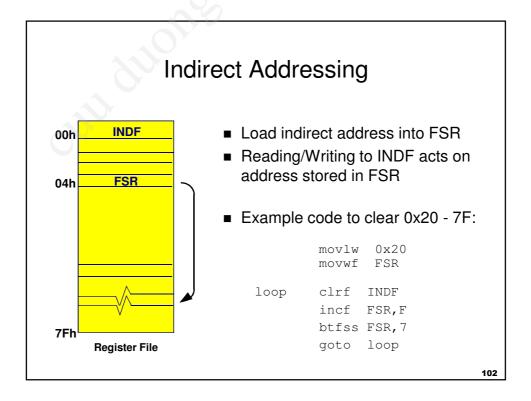

## Software: Relative Addressing

uExample of Relative Addressing (using a table):

| ; | Her  | ce's a si | imple  | looku  | p tab  | le which is called as a         |    |

|---|------|-----------|--------|--------|--------|---------------------------------|----|

| ; | suk  | proutine. | . Expe | ects t | he tal | ole offset to be loaded in W.   |    |

| ; | An   | example   | call   | looks  | like   | this:                           |    |

| ; |      | movlw     | 0x04   |        | ;      | Load W with 4                   |    |

| ; |      | call      | Table  | е      | ;      | Call the table subroutine       |    |

| ; |      | movwf     | Resu   | lt     | ;      | Store the result from the table | е  |

|   |      |           |        |        |        |                                 |    |

| Т | able | e addwf   | PCL,   | W      | ;      | Jump to (current PCL) + W       |    |

|   |      | retlw     | 0x00   |        | ;      | Return with 0x00 in W           |    |

|   |      | retlw     | 0x23   |        | ;      | Return with 0x23 in W           |    |

|   |      | retlw     | 0x33   |        | ;      | etc.                            |    |

|   |      | retlw     | 0x88   |        |        |                                 |    |

|   |      |           |        |        |        |                                 |    |

|   |      |           |        |        |        |                                 |    |

|   |      |           |        |        |        |                                 |    |

|   |      |           |        |        |        | 1                               | 01 |

|   |      |           |        |        |        |                                 |    |

|                                                  | File<br>Addre: |                      |                      | File<br>Address |

|--------------------------------------------------|----------------|----------------------|----------------------|-----------------|

|                                                  | 00h            | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup>  | 80h             |

| <b>D</b>                                         | 01h            | TMR0                 | OPTION               | 81h             |

| Banking                                          | 02h            | PCL                  | PCL                  | 82h             |

| Dariking                                         | 03h            | STATUS               | STATUS               | 83h             |

| 8                                                | 04h            | FSR                  | FSR                  | 84h             |

|                                                  | 05h            | PORTA                | TRISA                | 85h             |

|                                                  | 06h            | PORTB                | TRISB                | 86h             |

| DAM in the DICe is hereked, some sight energial  | 07h            | PORTC                | TRISC                | 87h             |

| RAM in the PICs is banked, especially special    | 08h            | PORTD <sup>(2)</sup> | TRISD <sup>(2)</sup> | 88h             |

| function registers. Use the bank colort commande | 09h            | PORTE <sup>(2)</sup> | TRISE <sup>(2)</sup> | 89h             |

| function registers. Use the bank select commands | 0Ah            | PCLATH               | PCLATH               | 8Ah             |

| to choose the bank.                              | 0Bh            | INTCON               | INTCON               | 8Bh             |

| to choose the bank.                              | 0Ch            | PIR1                 | PIE1                 | 8Ch             |

|                                                  | ODh            | PIR2                 | PIE2                 | 8Dh             |

|                                                  | 0Eh            | TMR1L                | PCON                 | 8Eh             |

| Either:                                          | 0Fh            | TMR1H                |                      | 8Fh<br>90h      |

| Littlet.                                         | 10h<br>11h     | T1CON<br>TMR2        |                      | 90h             |

|                                                  | 11h<br>12h     | T2CON                | PR2                  | 91h<br>92h      |

|                                                  | 12h            | SSPBUF               | SSPADD               | 92h             |

| bsf STATUS, RPO                                  | 14h            | SSPCON               | SSPSTAT              | 94h             |

| DST DIMIOS, MO                                   | 15h            | CCPR1L               | GGFGIAI              | 95h             |

| bcf STATUS, RPO                                  | 16h            | CCPR1H               |                      | 96h             |

| ber biniob, no                                   | 17h            | CCP1CON              |                      | 97h             |

|                                                  | 18h            | RCSTA                | TXSTA                | 98h             |

|                                                  | 19h            | TXREG                | SPBRG                | 99h             |

| Or use the assembler directive:                  | 1Ah            | RCREG                | 0.0.10               | 9Ah             |

|                                                  | 1Bh            | CCPR2L               | 1                    | 9Bh             |

|                                                  | 1Ch            | CCPR2H               | 7                    | 9Ch             |

|                                                  | 1Dh            | CCP2CON              |                      | 9Dh             |

| Banksel <registername></registername>            | 1Eh            | ADRES                |                      | 9Eh             |

|                                                  | 1Fh            | ADCON0               | ADCON1               | 9Fh             |

|                                                  | 20h            |                      |                      | A0h             |

|                                                  |                |                      |                      |                 |

|                                                  |                | General              | General              |                 |

|                                                  |                | Purpose              | Purpose              |                 |

|                                                  |                | Register             | Register             |                 |

|                                                  |                |                      |                      |                 |

|                                                  |                |                      | 1                    | FFh             |

|                                                  | 7Fh            |                      |                      | FFU .           |

|                                                  |                | Bank 0               | Bank 1               |                 |

|                                                  |                |                      |                      | 103             |

| Constant    | Syntax                                           | Example               | Value      |

|-------------|--------------------------------------------------|-----------------------|------------|

| Decimal     | D' decimal_number'<br>.'decimal_number'          | D'167'<br>.'167'      | 0x000000A7 |

| Hexadecimal | H' hexadecimal'<br>Oxhexadecimal<br>hexadecimalH | H'A7'<br>0xA7<br>0A7H | 0x000000A7 |

| Octal       | 0' octal'<br>octalO                              | Oʻ247′<br>247O        | 0x000000A7 |

| Binary      | B' binary'                                       | B'10100111'           | 0x00000A7  |

| ASCII       | A' ASCII_char'<br>`ASCIII'                       | A'Z' `Z'              | 0x000005A  |

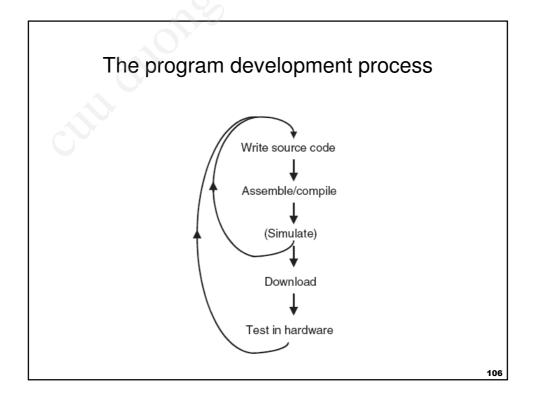

| •             | onents of MPI                                                                                            | •                                                            | -                                                                                                                         |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Software tool | Tool function                                                                                            | Files produced or used                                       | File description                                                                                                          |

| Text editor   | Used to create and modify source code text file                                                          | PROGNAME.ASM                                                 | Source code text file                                                                                                     |

| Assembler     | Generates machine code<br>from source code, reports<br>syntax errors, generates<br>list and symbol files | PROGNAME.HEX<br>PROGNAME.ERR<br>PROGNAME.LST<br>PROGNAME.COD | Executable machine code<br>Error messages<br>List file with source<br>and machine code<br>Symbol and debug<br>information |

| Simulator     | Allows program to be<br>tested in software before<br>downloading                                         | PROGNAME.HEX<br>PROGNAME.COD                                 | OR                                                                                                                        |

| Programmer    | Downloads machine code<br>to chip                                                                        | PROGNAME.HEX                                                 |                                                                                                                           |

|               |                                                                                                          | 00                                                           | 10                                                                                                                        |

|               |                                                                                                          |                                                              |                                                                                                                           |

|               | Assem                                                                                                    | nbler format                                                 |                                                                                                                           |

| mor                                                                                                    | mnemonic ope                                                                                                                                                                        | rand comment<br>; select memor<br>; config patte                                                                                                                                      | y bank 1                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Column 1                                                                                               | Column 2                                                                                                                                                                            | Column 3                                                                                                                                                                              | Column 4                                                                                                                                                                                                                                                                          |

| Label                                                                                                  | COMMAND                                                                                                                                                                             | Operand/s                                                                                                                                                                             | ; Comment                                                                                                                                                                                                                                                                         |

| Label<br>EQUated to<br>a value, or<br>to indicate<br>a program<br>destination<br>address for<br>jumps. | Mnemonic<br>form of the<br>instruction for<br>the processor<br>to carry out<br>a specific<br>operation.<br>Only mnemonics<br>specified in<br>the instruction<br>set may be<br>used. | The data or<br>register<br>contents to<br>be used in the<br>instruction.<br>Registers<br>are usually<br>represented by<br>a label. Some<br>instructions<br>do not need an<br>operand. | Explanatory text<br>to the right of a<br>semicolon on any<br>line of code helps<br>the programmer<br>and user to<br>understand the<br>program. It has<br>no effect on the<br>operation of the<br>program. Full<br>line comments<br>may also be used<br>between program<br>blocks. |

109