# Practical sition for

## Data Acquisition for Instrumentation and Control Systems

## Practical Data Acquisition for Instrumentation and Control Systems

cuu duong than cong . com

cuu duong than cong . com

#### Titles in the series

Practical Cleanrooms: Technologies and Facilities (David Conway)

*Practical Data Acquisition for Instrumentation and Control Systems* (John Park, Steve Mackay)

*Practical Data Communications for Instrumentation and Control* (John Park, Steve Mackay, Edwin Wright)

Practical Digital Signal Processing for Engineers and Technicians (Edmund Lai)

Practical Electrical Network Automation and Communication Systems (Cobus Strauss)

Practical Embedded Controllers (John Park)

Practical Fiber Optics (David Bailey, Edwin Wright)

*Practical Industrial Data Networks: Design, Installation and Troubleshooting* (Steve Mackay, Edwin Wright, John Park, Deon Reynders)

*Practical Industrial Safety, Risk Assessment and Shutdown Systems* (Dave Macdonald)

*Practical Modern SCADA Protocols: DNP3, 60870.5 and Related Systems* (Gordon Clarke, Deon Reynders)

Practical Radio Engineering and Telemetry for Industry (David Bailey)

Practical SCADA for Industry (David Bailey, Edwin Wright)

Practical TCP/IP and Ethernet Networking (Deon Reynders, Edwin Wright)

Practical Variable Speed Drives and Power Electronics (Malcolm Barnes)

## Practical Data Acquisition for Instrumentation and Control Systems

John Park ASD, IDC Technologies, Perth, Australia

**Steve Mackay** CPEng, BSc(ElecEng), BSc(Hons), MBA, IDC Technologies, Perth, Australia

## cuu duong than cong . com

## cuu duong than cong . com

AMSTERDAM • BOSTON • HEIDELBERG • LONDON • NEW YORK • OXFORD PARIS • SAN DIEGO • SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Newnes is an imprint of Elsevier

Newnes An imprint of Elsevier Linacre House, Jordan Hill, Oxford OX2 8DP 200 Wheeler Road, Burlington, MA 01803

First published 2003

Copyright © 2003, IDC Technologies. All rights reserved

No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1T 4LP. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publisher

#### **British Library Cataloguing in Publication Data**

A catalogue record for this book is available from the British Library

ISBN 07506 57960

For information on all Newnes publications, visit our website at www.newnespress.com

. com

Typeset and Edited by Vivek Mehra, Mumbai, India (vivekmehra@tatanova.com)

Printed and bound in Great Britain

## cuu duong than cong . com

## Preface

In less than a decade, the PC has become the most widely used platform for data acquisition and control. The main reasons for the popularity of PC-based technology are low costs, flexibility and ease of use, and, last but not the least, performance. This solid and dependable trait is all thanks to the use of 'off-the-shelf' components. Data acquisition with a PC enables one to display, log and control a wide variety of real world signals such as pressure, flow, and temperature. This ability coupled with that of easy interface with various stand-alone instruments makes the systems ever more desirable.

Until the advent of the PC, data acquisition and process monitoring were carried out by using dedicated data loggers, programmable logic controllers and or expensive proprietary computers. Today's superb software-based operator interfaces make the PC an increasingly attractive option in these typical applications:

- Laboratory data acquisition and control

- Automatic test equipment (ATE) for inspection of components

- Medical instrumentation and monitoring

- Process control of plants and factories

- Environmental monitoring and control

- Machine vision and inspection

The key to the effective application of PC-based data acquisition is the careful matching of real world requirements with appropriate hardware and software. Depending on your needs, monitoring data can be as simple as connecting a few cables to a plug-in board and running a menu-driven software package. At the other end of the spectrum, you could design customized sensing and conversion hardware, or perhaps develop application software to optimize a system.

This book gives both the novice and the experienced user a solid grasp of the principles and practical implementation of interfacing the PC and stand-alone instruments with real world signals. The main objective of this book is to give you a thorough understanding of PC-based data acquisition systems and to enable you to design, specify, install, configure, and program data acquisition systems quickly and effectively.

After reading this book, we believe you will be able to:

- Demonstrate a sound knowledge of the fundamentals of data acquisition (with a focus on PC-based work)

- Competently install and configure a simple data acquisition system

- Choose and configure the correct software

- Avoid the common pitfalls in designing a data acquisition system

This book is intended for engineers and technicians who are:

- Electronic engineers

- Instrumentation and control engineers

- Electrical engineers

- Electrical technicians

- Electrical technicians

Systems engineers • Scientists working in the data acquisition area

- Process control engineers

- System integrators

- Design engineers

A basic knowledge of electrical principles is useful in understanding the outlined concepts, but this book also focuses on the fundamentals; hence, understanding key concepts should not be too onerous.

The structure of the book is as follows.

**Chapter 1:** Introduction. This chapter gives a brief overview of what is covered in the book with an outline of the essentials and main hardware and software components of data acquisition.

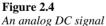

**Chapter 2:** Analog and digital signals. This chapter reviews analog and digital inputs to the data acquisition system, through such techniques as temperature measurement and the use of strain gauges.

**Chapter 3:** Signal conditioning. This chapter discusses how signals are conditioned before the data acquisition system can accurately acquire it.

**Chapter 4:** The PC for real time work. This chapter considers the various PC related issues to make it suitable for real time work such as software and hardware.

**Chapter 5:** Plug-in data acquisition boards. This chapter assesses the wide range of methods of using plug-in data acquisition boards such as analog inputs/ outputs, digital inputs/outputs and counter/timer configurations.

**Chapter 6:** Serial data communications. This chapter reviews the fundamental definitions and basic principles of digital serial data communications with a focus on RS-232 and RS-485.

**Chapter 7:** Distributed and stand-alone loggers/controllers. This chapter discusses the hardware and software configurations of stand-alone logger/controllers.

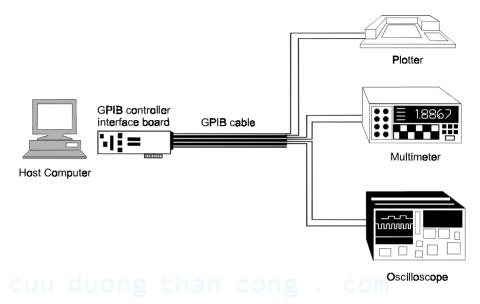

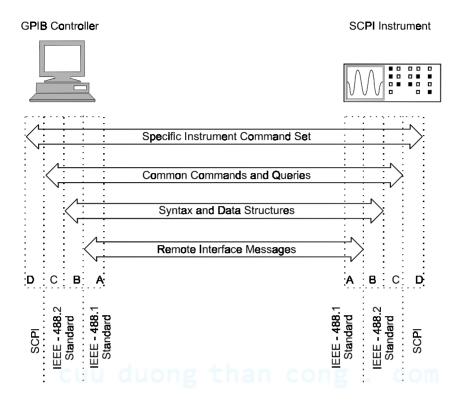

**Chapter 8:** IEEE 488 standard. This chapter reviews the IEE 488 standard with a reference to the IEEE 488.2 and SCPI approaches.

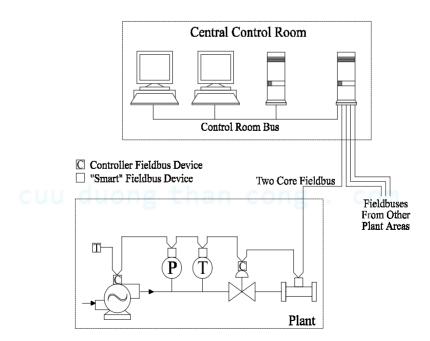

**Chapter 9: Ethernet and fieldbus systems.** This chapter briefly outlines the essentials of Ethernet and Fieldbus systems.

**Chapter 10:** The universal serial bus (USB). This chapter reviews the key features of the universal serial bus, which will have a major impact on PC-based data acquisition.

**Chapter 11:** Specific techniques. This chapter discusses how the PC can be used for process control applications.

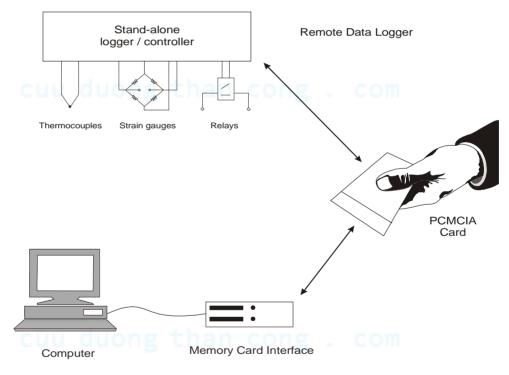

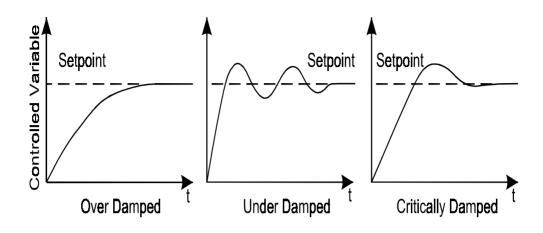

**Chapter 12:** The PCMCIA card. This chapter discusses the essentials of the PCMCIA card as applied to data acquisition systems.

## Contents

|            |                                   | Contonto                                           |                 |

|------------|-----------------------------------|----------------------------------------------------|-----------------|

| Prefa      | ce                                |                                                    | xvii            |

| 1          | Introduction                      |                                                    | 1               |

| 1.1        | Definition of data                | acquisition and control                            | 1               |

| 1.2        | Fundamentals of                   | data acquisition                                   | 2               |

|            |                                   | cers and sensors                                   | 3               |

|            |                                   | ing and communications cabling                     | 3<br>3<br>3     |

|            | •                                 | onditioning<br>quisition hardware                  | 3<br>4          |

|            |                                   | quisition software                                 | 5               |

|            | 1.2.6 Host cor                    | •                                                  | 5               |

| 1.3        | Data acquisition a                | and control system configuration                   | 6               |

|            |                                   | er plug-in I/O                                     | 7               |

|            | 1.3.2 Distribut<br>1.3.3 Stand-al | ed I/O<br>one or distributed loggers/controllers   | 8<br>9          |

|            |                                   | 8 (GPIB) remote programmable instruments           | 9<br>11         |

| 2          | Analog and di                     | gital signals                                      | 13              |

| 2.1        | Classification of                 | iong than cong . com                               | 13              |

|            |                                   | ignals binary signals                              | 14              |

|            | 2.1.2 Analog s                    |                                                    | 15              |

| 2.2        | Sensors and tran                  | sducers                                            | 17              |

| 2.3        | Transducer chara                  | acteristics                                        | 17              |

| 2.4        | Resistance tempe                  | erature detectors (RTDs)                           | 19              |

|            |                                   | eristics of RTDs                                   | 19              |

|            |                                   | of RTDs ement circuits and considerations for RTDs | 19              |

| <b>2</b> E |                                   | ament circuits and considerations for RTDs         | 20              |

| 2.5        | Thermistors                       |                                                    | 22              |

| 2.6        | 2.6.1 Reference                   | ce junction compensation                           | <b>22</b><br>23 |

|            |                                   | al block and compensation cables                   | 23              |

|            |                                   | couple linearization                               | 24              |

|            |                                   | couple types and standards                         | 25              |

|            |                                   | couple construction                                | 26              |

|            |                                   | ement errors<br>onfigurations                      | 26<br>27        |

| 2.7        | Strain gauges                     |                                                    | 28              |

| 2.8        | Wheatstone bridg                  | ges                                                | 29              |

|            | 2.8.1 General                     | characteristics                                    | 29              |

|            | 2.8.2 Quarter                     | bridge configuration                               | 30              |

|            |                             | bridge configuration                                      | 31        |

|------------|-----------------------------|-----------------------------------------------------------|-----------|

|            |                             | pridge configuration                                      | 32        |

|            |                             | g connections<br>perature considerations                  | 32<br>34  |

|            | •                           | surement errors                                           | 34        |

| 3          | Signal cond                 | litioning                                                 | 36        |

| 3.1        | Introduction                |                                                           | 36        |

| 3.2        | Types of signa              | al conditioning                                           | 37        |

|            |                             | ification                                                 | 37        |

|            | 3.2.2 Isolat                |                                                           | 37        |

|            | 3.2.3 Filter<br>3.2.4 Linea | ing<br>arization                                          | 38<br>44  |

| 3.3        |                             | nal conditioning                                          | 44        |

| 5.5        |                             | in board signal conditioning                              | 44        |

|            | 0                           | t connect modular – two-wire transmitters                 | 45        |

|            | 3.3.3 Distri                | buted I/O – digital transmitters                          | 46        |

| 3.4        | Field wiring ar             | nd signal measurement                                     | 48        |

|            |                             | nded signal sources                                       | 49        |

|            |                             | ing signal sources                                        | 49        |

|            |                             | e-ended measurement<br>rential measurement                | 50<br>50  |

|            |                             | mon mode voltages and CMRR                                | 50        |

|            |                             | suring grounded signal sources                            | 52        |

|            |                             | nd loops                                                  | 53        |

|            |                             | al circuit isolation                                      | 53        |

|            |                             | suring ungrounded signal sources                          | 54        |

| о <b>г</b> | •                           | em isolation                                              | 55        |

| 35         | Noise and inte              |                                                           | <b>56</b> |

|            |                             | ition of noise and interference<br>ces and types of noise | 56<br>56  |

| 3.6        | Minimizing noi              |                                                           | 61        |

| 5.0        |                             | e shielding and shield earthing                           | 61        |

|            |                             | nding cable shields                                       | 62        |

| 3.7        | Shielded and t              | wisted-pair cable                                         | 64        |

|            |                             | ted-pair cables                                           | 65        |

|            | 3.7.2 Coax                  | tial cables                                               | 66        |

| 4          | The PC for                  | real time work                                            | 67        |

|            | Introduction                |                                                           | 67        |

| 4.1        | Operating syst              | tems                                                      | 67        |

|            | 4.1.1 DOS                   |                                                           | 68        |

|            |                             | osoft Windows 3.1, 95, 98, 2000 and NT                    | 69        |

|            | 4.1.3 UNIX                  |                                                           | 71        |

| 4.2        | Operation of ir             | nterrupts                                                 | 72        |

#### 4.2 **Operation of interrupts**

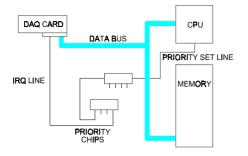

|      | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8 | Hardware interrupts<br>Non-maskable interrupts<br>Maskable interrupts<br>Programmable interrupt controller(s)<br>Initialization required for interrupts<br>I/O devices requesting interrupt service<br>Interrupt service routines<br>Sharing interrupts | 73<br>73<br>73<br>73<br>75<br>75<br>75<br>76<br>77   |

|------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

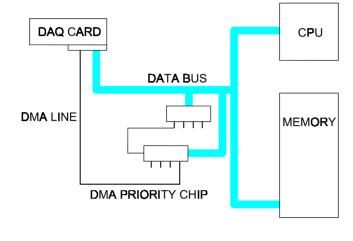

| 4.3  | <b>Operatio</b><br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5         | DMA controllers<br>Initialization required for DMA control<br>I/O devices requesting DMA<br>Terminal count signal<br>DMA modes                                                                                                                          | <b>77</b><br>78<br>79<br>79<br>80<br>81              |

| 4.4  | •                                                                    | string instructions (REP INSW)                                                                                                                                                                                                                          | 83                                                   |

| 4.5  |                                                                      | lata transfer                                                                                                                                                                                                                                           | 84                                                   |

| 4.6  |                                                                      | nsfer speed (polled I/O, interrupt I/O, DMA)                                                                                                                                                                                                            | 96                                                   |

| 4.7  | <b>Memory</b><br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4                    | Base memory<br>Expanded memory system (EMS)<br>Extended memory (XMS)<br>Expansion memory hardware                                                                                                                                                       | <b>97</b><br>97<br>98<br>99<br>99                    |

| 48   | <b>Expansi</b><br>4.8.1<br>4.8.2<br>4.8.3<br>4.8.4                   | ion bus standards (ISA, EISA, PCI, and PXI bus)<br>ISA bus<br>Microchannel bus<br>EISA bus<br>The PCI, compactPCI and PXI bus                                                                                                                           | <b>99</b><br>99<br>108<br>108<br>109                 |

| 4.9  | <b>Serial co</b><br>4.9.1<br>4.9.2                                   | ommunications<br>Standard settings<br>Intelligent serial ports                                                                                                                                                                                          | <b>112</b><br>112<br>112                             |

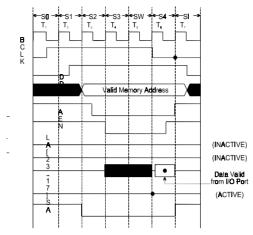

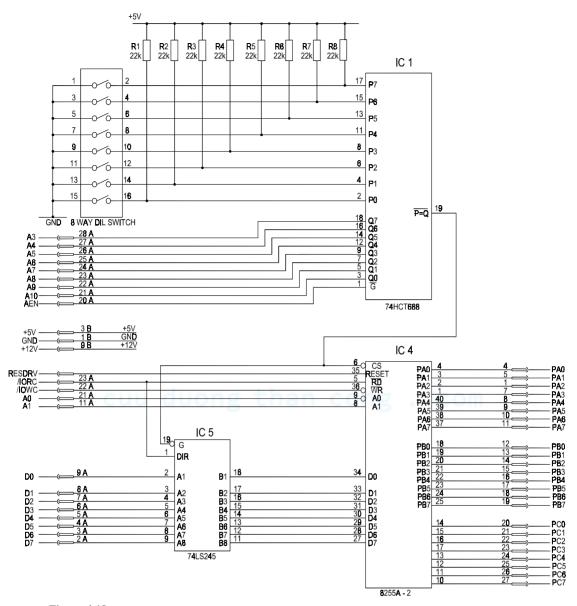

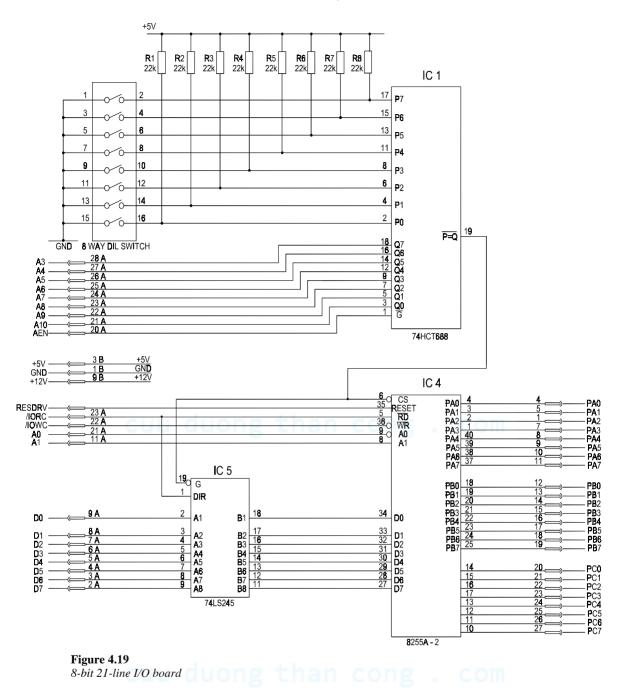

| 4.10 | Interfaci<br>4.10.1<br>4.10.2<br>4.10.3                              | ing techniques to the IBM PC<br>Hardware considerations<br>Address decoding<br>Timing requirements                                                                                                                                                      | <b>113</b><br>114<br>115<br>116                      |

| 5    | Plug-ir                                                              | n data acquisition boards                                                                                                                                                                                                                               | 119                                                  |

| 5.1  | Introduc                                                             | ction                                                                                                                                                                                                                                                   | 119                                                  |

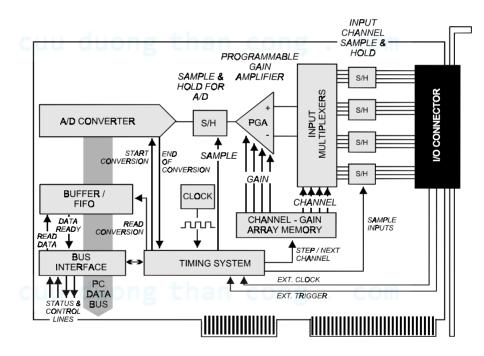

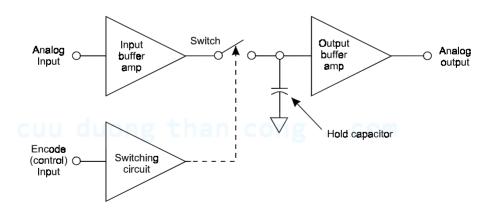

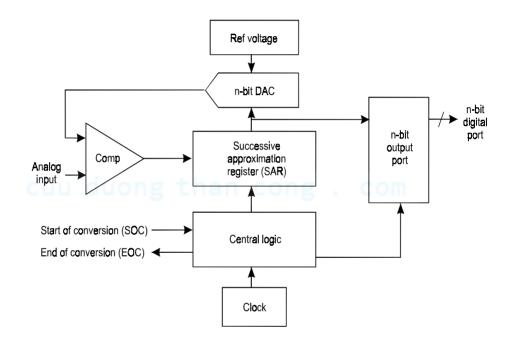

| 5.2  | <b>A/D Boa</b><br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6 | nrds<br>Multiplexers<br>Input signal amplifier<br>Channel-gain arrays<br>Sample and hold circuits<br>A/D converters<br>Memory (FIFO) buffer                                                                                                             | <b>120</b><br>120<br>121<br>123<br>123<br>124<br>136 |

|      | 5.2.7                                                                         | Timing circuitry                                                                                                                                                                       | 136                                                         |

|------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|      | 5.2.8                                                                         | Expansion bus interface                                                                                                                                                                | 137                                                         |

| 5.3  | <b>Single e</b>                                                               | ended vs differential signals                                                                                                                                                          | <b>138</b>                                                  |

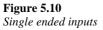

|      | 5.3.1                                                                         | Single ended inputs                                                                                                                                                                    | 138                                                         |

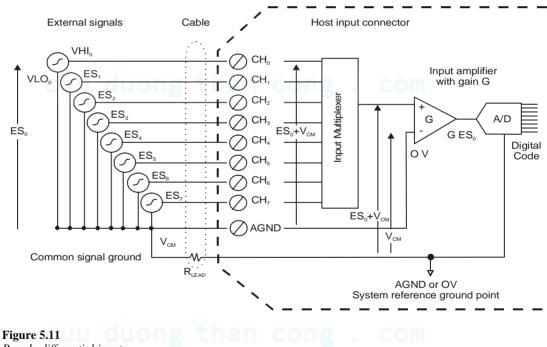

|      | 5.3.2                                                                         | Pseudo-differential configuration                                                                                                                                                      | 139                                                         |

|      | 5.3.3                                                                         | Differential inputs                                                                                                                                                                    | 140                                                         |

| 5.4  | <b>Resolut</b>                                                                | ion, dynamic range and accuracy of A/D boards                                                                                                                                          | <b>141</b>                                                  |

|      | 5.4.1                                                                         | Dynamic range                                                                                                                                                                          | 141                                                         |

|      | 5.4.2                                                                         | Resolution                                                                                                                                                                             | 141                                                         |

|      | 5.4.3                                                                         | System accuracy                                                                                                                                                                        | 142                                                         |

| 5.5  | <b>Samplir</b>                                                                | ng rate and the Nyquist theorem                                                                                                                                                        | <b>143</b>                                                  |

|      | 5.5.1                                                                         | Nyquist's theorem                                                                                                                                                                      | 143                                                         |

|      | 5.5.2                                                                         | Aliasing                                                                                                                                                                               | 143                                                         |

|      | 5.5.3                                                                         | Preventing aliasing                                                                                                                                                                    | 146                                                         |

|      | 5.5.4                                                                         | Practical examples                                                                                                                                                                     | 148                                                         |

| 5.6  | <b>Samplir</b>                                                                | ng techniques                                                                                                                                                                          | <b>151</b>                                                  |

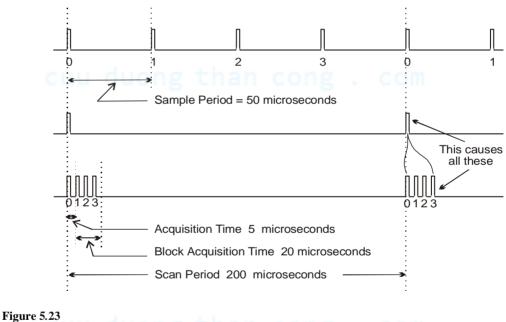

|      | 5.6.1                                                                         | Continuous channel scanning                                                                                                                                                            | 151                                                         |

|      | 5.6.2                                                                         | Simultaneous sampling                                                                                                                                                                  | 153                                                         |

|      | 5.6.3                                                                         | Block mode operations                                                                                                                                                                  | 154                                                         |

| 5.7  | Speed v                                                                       | /s throughput                                                                                                                                                                          | 156                                                         |

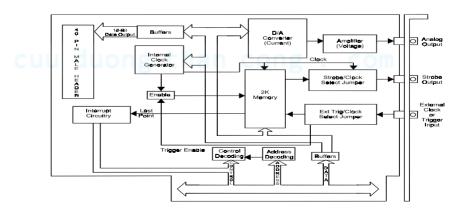

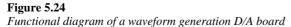

| 5.8  | <b>D/A boa</b><br>5.8.1<br>5.8.2<br>5.8.3<br>5.8.4<br>5.8.5<br>5.8.6<br>5.8.7 | IndsDigital to analog convertersParameters of D/A convertersFunctional characteristics of D/A boardsMemory (FIFO) bufferTiming circuitryOutput amplifier bufferExpansion bus interface | <b>157</b><br>158<br>160<br>162<br>162<br>163<br>163<br>163 |

| 5.9  | Digital I                                                                     | /O boards                                                                                                                                                                              | 164                                                         |

| 5.10 | Interfac                                                                      | ing digital inputs/outputs                                                                                                                                                             | <b>166</b>                                                  |

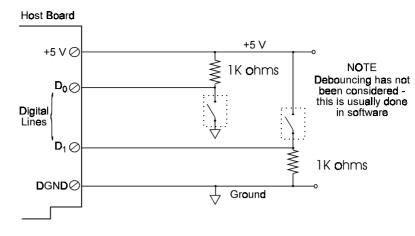

|      | 5.10.1                                                                        | Switch sensing                                                                                                                                                                         | 166                                                         |

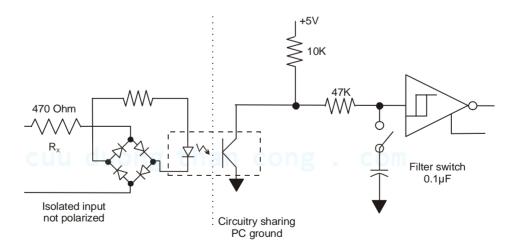

|      | 5.10.2                                                                        | AC/DC voltage sensing                                                                                                                                                                  | 167                                                         |

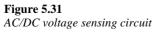

|      | 5.10.3                                                                        | Driving an LED indicator                                                                                                                                                               | 168                                                         |

|      | 5.10.4                                                                        | Driving relays                                                                                                                                                                         | 168                                                         |

| 5.11 | Counter                                                                       | r/timer I/O boards                                                                                                                                                                     | 170                                                         |

|      |                                                                               |                                                                                                                                                                                        |                                                             |

| 6    | Serial                                                                        | data communications                                                                                                                                                                    | 176                                                         |

| 6.1  | <b>Definitio</b>                                                              | ons and basic principles                                                                                                                                                               | <b>176</b>                                                  |

|      | 6.1.1                                                                         | Transmission modes – simplex and duplex                                                                                                                                                | 177                                                         |

|      | 6.1.2                                                                         | Coding of messages                                                                                                                                                                     | 178                                                         |

|      | 6.1.3                                                                         | Format of data communications messages                                                                                                                                                 | 181                                                         |

|      | 6.1.4                                                                         | Data transmission speed                                                                                                                                                                | 182                                                         |

|     | -      |                                      |  |

|-----|--------|--------------------------------------|--|

| 6.2 | RS-232 | -C interface standard                |  |

|     | 6.2.1  | Electrical signal characteristics    |  |

|     | 6.2.2  | Interface mechanical characteristics |  |

182 183 186

|     | 6.2.3                                                        | Functional description of the interchange circuits | 187 |

|-----|--------------------------------------------------------------|----------------------------------------------------|-----|

|     | 6.2.4                                                        | The sequence of operation of the EIA-232 interface | 188 |

|     | 6.2.5                                                        | Examples of RS-232 interfaces                      | 190 |

|     | 6.2.6                                                        | Main features of the RS-232 Interface Standard     | 190 |

| 6.3 | RS-485                                                       | interface standard                                 | 191 |

|     | 6.3.1                                                        | RS-485 repeaters                                   | 192 |

| 6.4 | Compa                                                        | rison of the RS-232 and RS-485 standards           | 193 |

| 6.5 | The 20                                                       | mA current loop                                    | 194 |

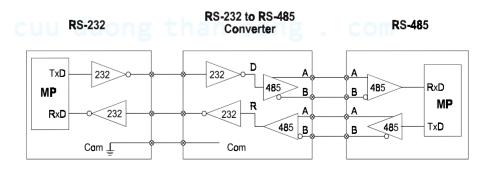

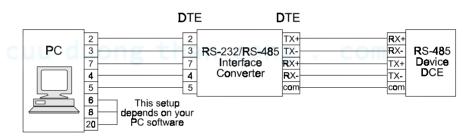

| 6.6 | Serial i                                                     | nterface converters                                | 194 |

| 6.7 | Protoc                                                       | ols                                                | 195 |

|     | 6 7.1                                                        | Flow control protocols                             | 196 |

|     | 6.7.2                                                        | ASCII-based protocols                              | 196 |

| 6.8 | Error d                                                      | etection                                           | 198 |

|     | 6.8.1                                                        | Character redundancy checks                        | 199 |

|     | 6.8.2                                                        | Block redundancy checks                            | 199 |

|     | 6.8.3                                                        | Cyclic redundancy Checks                           | 199 |

| 6.9 | Troubleshooting & testing serial data communication circuits |                                                    |     |

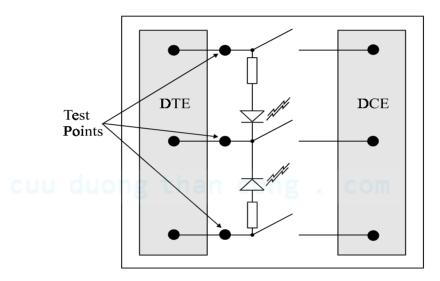

|     | 6.9.1                                                        | The breakout box                                   | 201 |

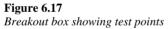

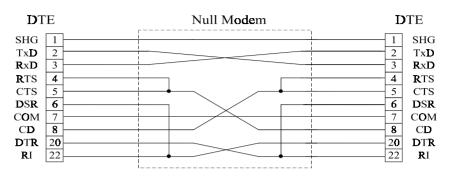

|     | 6.9.2                                                        | Null modem                                         | 201 |

|     | 6.9.3                                                        | Loop back plug                                     | 202 |

|     | 6.9.4                                                        | Protocol analyzer                                  | 202 |

|     | 6.9.5                                                        | The PC as a protocol analyzer                      | 202 |

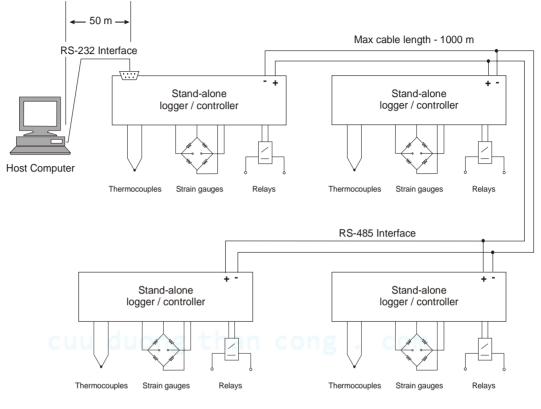

## **7** Distributed and stand-alone loggers/controllers 204

| 7.1 | Introdu                           | uction                                             | 204 |  |

|-----|-----------------------------------|----------------------------------------------------|-----|--|

| 7.2 | Method                            | Methods of operation                               |     |  |

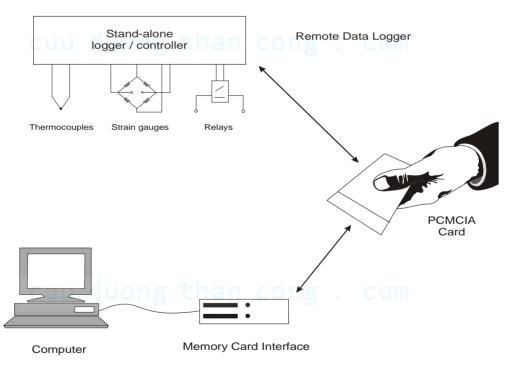

|     | 7.2.1                             | Programming and logging data using PCMCIA cards    | 205 |  |

|     | 7.2.2                             | Stand-alone operation                              | 206 |  |

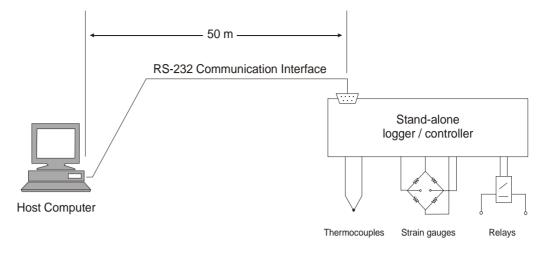

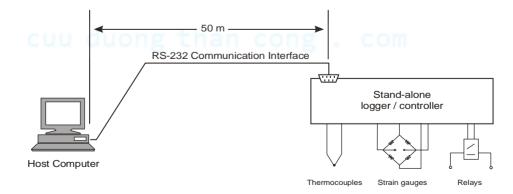

|     | 7.2.3                             | Direct connection to the host PC                   | 206 |  |

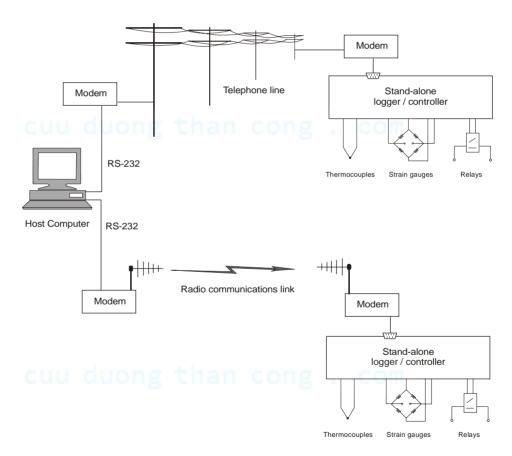

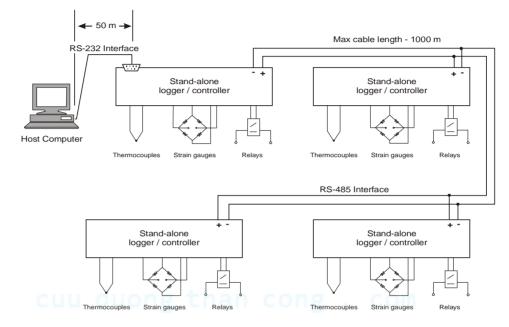

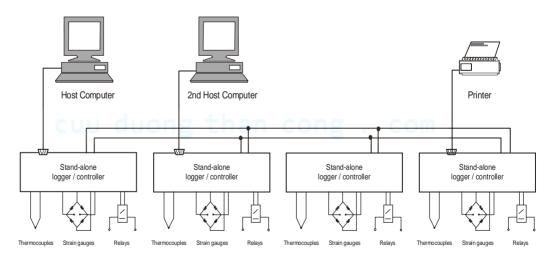

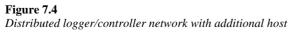

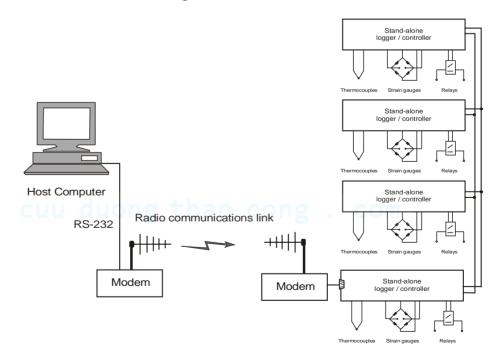

|     | 7.2.4                             | Remote connection to the host PC                   | 208 |  |

| 7.3 | Stand-                            | alone logger/controller hardware                   | 209 |  |

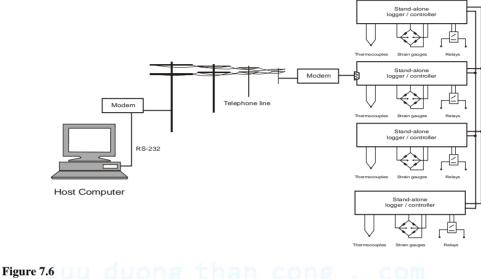

|     | 7.3.1                             | Microprocessors                                    | 210 |  |

|     | 7.3.2                             | Memory                                             | 210 |  |

|     | 7.3.3                             | Real time clock                                    | 211 |  |

|     | 7.3.4                             | Universal asynchronous receiver/transmitter (UART) | 212 |  |

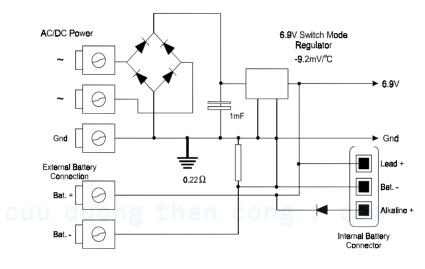

|     | 7.3.5                             | Power supply                                       | 213 |  |

|     | 7.3.6                             | Power management circuitry                         | 214 |  |

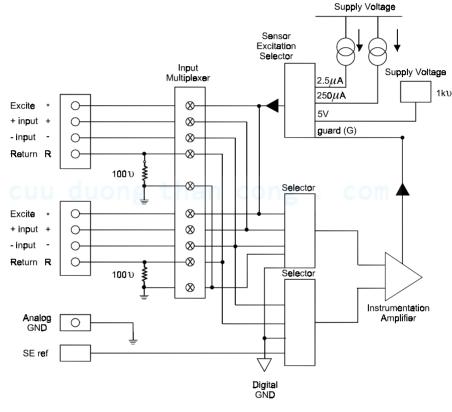

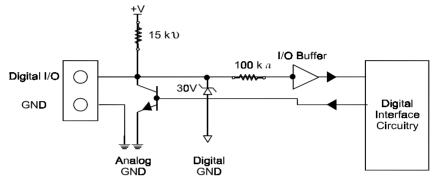

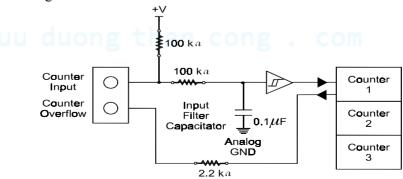

|     | 7.3.7                             | Analog inputs and digital I/O                      | 215 |  |

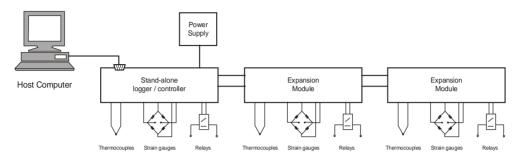

|     | 7.3.8                             | Expansion modules                                  | 217 |  |

| 7.4 | Communications hardware interface |                                                    | 217 |  |

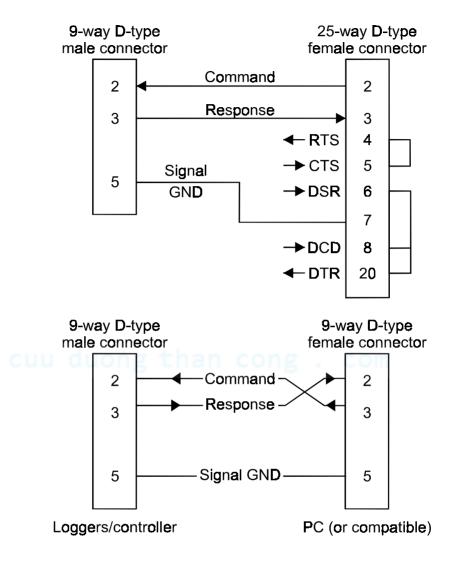

|     | 7.4.1                             | RS-232 interface                                   | 217 |  |

|     | 7.4.2                             | RS-485 standard                                    | 219 |  |

|     | 7.4.3                             | Communication bottlenecks and system performance   | 219 |  |

|     | 7.4.4                             | Using Ethernet to connect data loggers             | 220 |  |

| 7.5 | Stand-a                           | alone logger/controller firmware                   | 220 |  |

#### x Contents

| 7.6 | Stand-alone logger/controller software design                                                                | 221               |

|-----|--------------------------------------------------------------------------------------------------------------|-------------------|

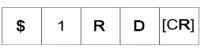

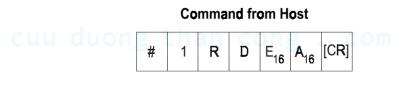

|     | 7.6.1 ASCII based command formats                                                                            | 222               |

|     | 7.6.2 ASCII based data formats                                                                               | 223               |

|     | 7.6.3 Error reporting                                                                                        | 223               |

|     | 7.6.4 System commands                                                                                        | 224               |

|     | 7.6.5 Channel commands                                                                                       | 224               |

|     | 7.6.6 Schedules                                                                                              | 226               |

|     | 7.6.7 Alarms<br>7.6.8 Data logging and retrieval                                                             | 229<br>229        |

| 7.7 | 7.6.8 Data logging and retrieval Host software                                                               | 229<br><b>230</b> |

|     |                                                                                                              |                   |

| 7.8 | Considerations in using standalone logger/controllers                                                        | 231               |

| 7.9 | Stand-alone logger/controllers vs internal systems                                                           | 232               |

|     | <ul><li>7.9.1 Advantages</li><li>7.9.2 Disadvantages</li></ul>                                               | 232<br>232        |

|     | 7.9.2 Disadvantages                                                                                          | 232               |

| 8   | IEEE 488 Standard                                                                                            | 234               |

| 8.1 | Introduction                                                                                                 | 234               |

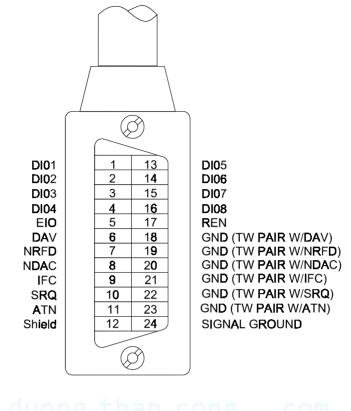

| 8.2 | Electrical and mechanical characteristics                                                                    | 235               |

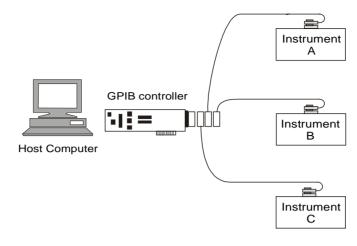

| 8.3 | Physical connection configurations                                                                           | 236               |

| 8.4 | Device types                                                                                                 | 237               |

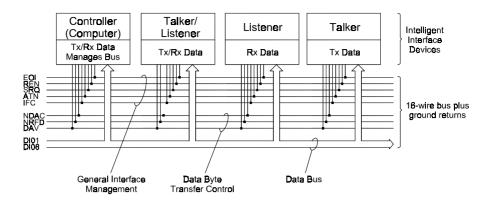

| 8.5 | Bus structure ong than cong com                                                                              | 238               |

|     | 8.5.1 Data lines                                                                                             | 239               |

|     | 8.5.2 Interface management lines                                                                             | 239               |

|     | 8.5.3 Handshake lines                                                                                        | 240               |

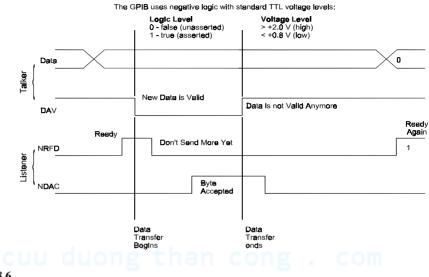

| 8.6 | GPIB handshaking                                                                                             | 240               |

| 8.7 | Device communication                                                                                         | 241               |

|     | 8.7.1 GPIB addressing                                                                                        | 242               |

|     | 8.7.2 Un-addressing devices                                                                                  | 242               |

|     | 8.7.3 Terminating data messages                                                                              | 242               |

|     | 8.7.4 Sending and receiving data                                                                             | 243               |

| 8.8 | IEEE 488.2                                                                                                   | 243               |

|     | 8.8.1 Requirements of IEEE 488.2 controllers                                                                 | 243               |

|     | 8.8.2 IEEE 488.2 control sequences                                                                           | 244               |

|     | 8.8.3 IEEE 488.2 protocols                                                                                   | 244               |

|     | 8.8.4 Device interface capabilities                                                                          | 246               |

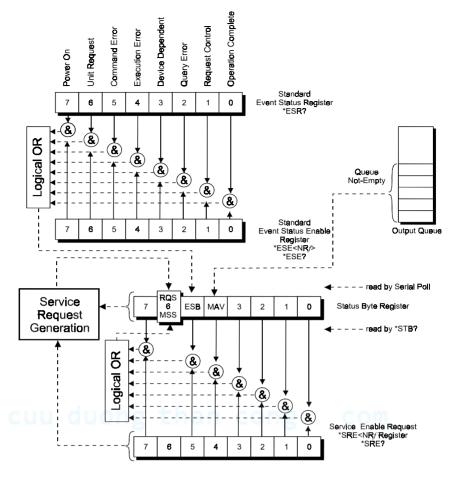

|     | 8.8.5 Status reporting model                                                                                 | 246               |

| 0.0 | 8.8.6 Common command set                                                                                     | 247               |

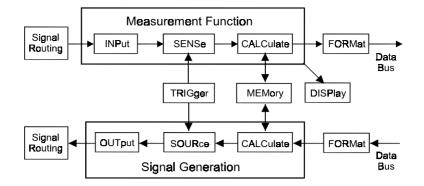

| 8.9 | Standard commands for programmable instruments (SCPI)                                                        | 248               |

|     | 8.9.1 IEEE 488.2 common commands required by the SCPI                                                        | 248               |

|     | 8.9.2 SCPI required commands                                                                                 | 249               |

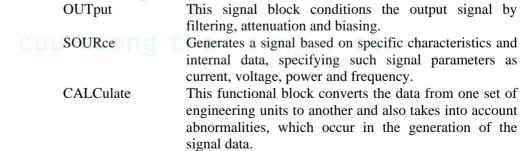

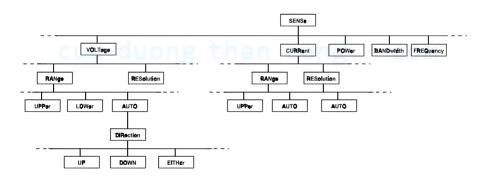

|     | <ul><li>8.9.3 The SCPI programming command model</li><li>8.9.4 SCPI hierarchical command structure</li></ul> | 249<br>251        |

|     |                                                                                                              |                   |

## 9 Ethernet & LAN systems

252

280

281

282

282

283

283

| 9.1  | Etherne  | t and fieldbuses for data acquisition   | 252 |

|------|----------|-----------------------------------------|-----|

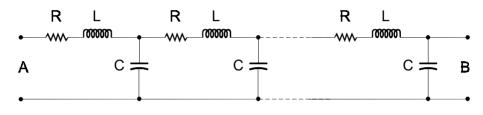

| 9.2  | Physica  | Il layer                                | 253 |

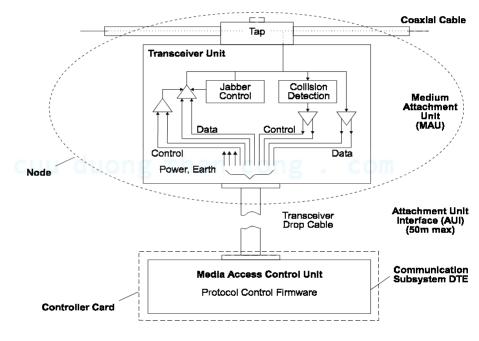

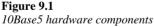

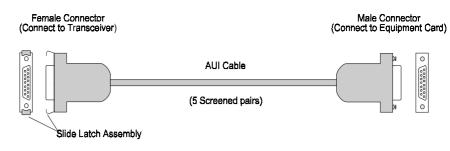

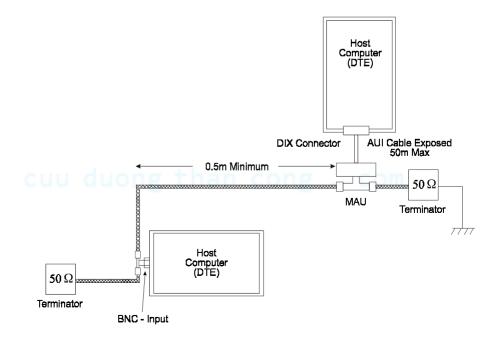

|      | 9.2.1    | 10Base5 systems                         | 253 |

|      | 9.2.2    | 10Base2 systems                         | 256 |

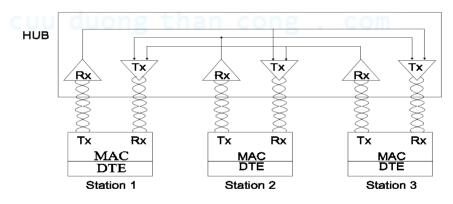

|      | 9.2.3    | 10BaseT                                 | 257 |

|      | 9.2.4    | 10BaseF                                 | 258 |

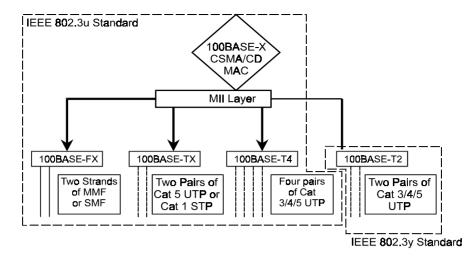

|      | 9.2.5    | 100 Base-T (100 Base-TX, T4, FX,T2)     | 258 |

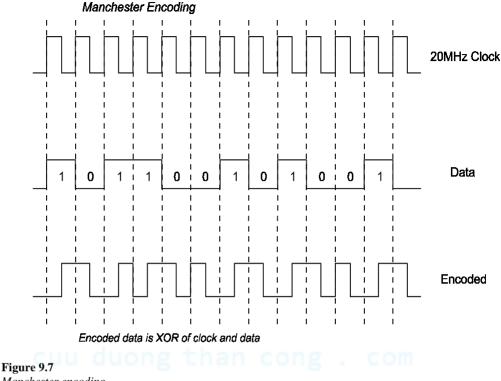

| 9.3  | Medium   | access control                          | 260 |

| 9.4  | MAC fra  | ame format                              | 263 |

| 9.5  | Differen | ce between 802.3 and Ethernet           | 264 |

| 9.6  | Reducir  | ng collisions                           | 265 |

| 9.7  | Etherne  | t design rules                          | 265 |

|      | 9.7.1    | Length of the cable segment             | 265 |

|      | 9.7.2    | Maximum transceiver cable length        | 266 |

|      | 9.7.3    | Node placement rules                    | 266 |

|      | 9.7.4    | Maximum transmission path               | 266 |

|      | 9.7.5    | Maximum network size                    | 267 |

|      | 9.7.6    | Repeater rules                          | 267 |

|      | 9.7.7    | Cable system grounding                  | 268 |

| 9.8  | Fieldbu  | ses                                     | 268 |

| 10   | The ur   | niversal serial bus (USB)               | 271 |

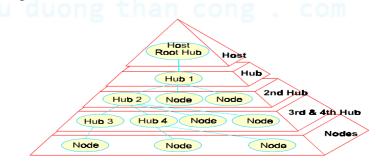

| 10.1 | Introduo | ction                                   | 271 |

| 10.2 | USB ov   | erall structure                         | 271 |

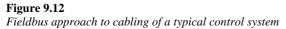

|      | 10.2.1   | Topology                                | 272 |

|      | 10.2.2   | Host hubs                               | 273 |

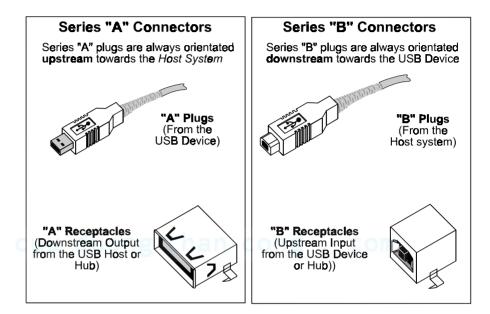

|      | 10.2.3   | The connectors (Type A and B)           | 274 |

|      | 10.2.4   | Low-speed cables and high-speed cables  | 274 |

|      | 10.2.5   | External hubs                           | 274 |

|      | 10.2.6   | USB devices                             | 275 |

|      | 10.2.7   | Host hub controller hardware and driver | 275 |

|      | 10.2.8   | USB software driver                     | 276 |

|      | 10.2.9   | Device drivers                          | 276 |

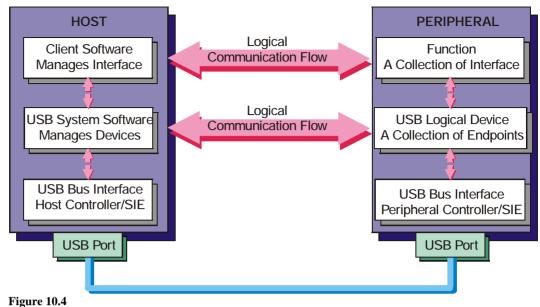

| 10 - | 10.2.10  | Communication flow                      | 276 |

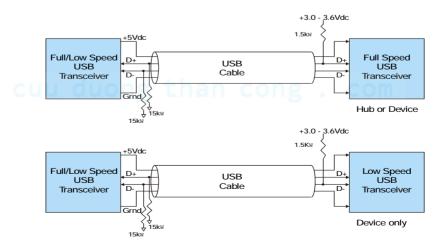

| 10.3 |          | vsical layer                            | 277 |

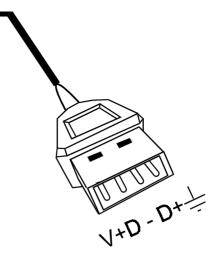

|      | 10.3.1   | Connectors                              | 278 |

|      | 10.3.2   | Cables                                  | 278 |

|      | 10.3.3   | Signaling                               | 279 |

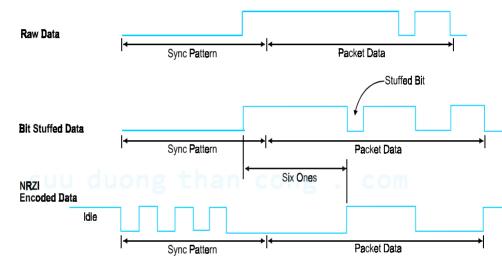

|      | 10.3.4   | NRZI and bit stuffing                   | 280 |

- 10.3.4 NRZI and bit stuffing

- 10.3.5 Power distribution

#### 10.4 **Datalink layer**

- Transfer types 10.4.1 10.4.2 Packets and frames

- 10.5 Application layer (user layer)

- 10.6 Conclusion

|      | 10.6.1                                                                                                                             | Acknowledgements                                                                                                                                                                                                              | 284                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 11   | Specif                                                                                                                             | ic techniques                                                                                                                                                                                                                 | 285                                                                                            |

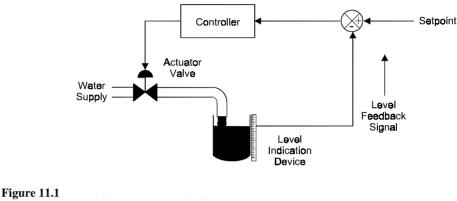

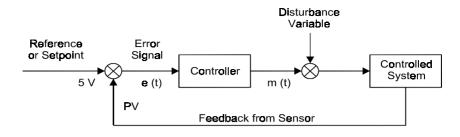

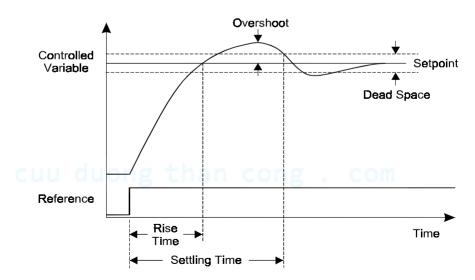

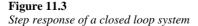

| 11.1 | <b>Open ar</b><br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.1.5<br>11.1.6<br>11.1.7                                               | nd closed loop control<br>Definitions<br>Fluid level closed loop control system<br>PID control algorithms<br>Transient performance – step response<br>Deadband<br>Output limiting<br>Manual control – bumpless transfer       | 285<br>285<br>286<br>286<br>288<br>289<br>289<br>289                                           |

| 11.2 | <b>Capturir</b><br>11.2.1<br>11.2.2<br>11.2.3                                                                                      | <b>ng high speed transient data</b><br>A/D board operation and memory requirements<br>Trigger modes (pre- and post-triggering)<br>Trigger source and level                                                                    | <b>290</b><br>290<br>290<br>290                                                                |

| 12   | The P                                                                                                                              | CMCIA Card                                                                                                                                                                                                                    | 292                                                                                            |

|      | Introduc                                                                                                                           | ction                                                                                                                                                                                                                         | 292                                                                                            |

| 12.1 | History                                                                                                                            |                                                                                                                                                                                                                               | 293                                                                                            |

| 12.2 | Features                                                                                                                           | S                                                                                                                                                                                                                             | 293                                                                                            |

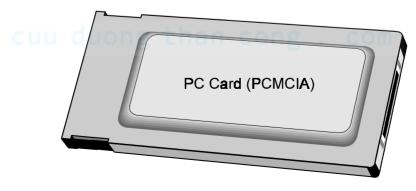

|      | 12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>12.2.5<br>12.2.6<br>12.2.7<br>12.2.8                                                       | Size and Versatility<br>16-Bit<br>Direct memory access (DMA)<br>Multi-functional and transparent<br>Low voltage<br>Plug and play<br>Execute in place<br>Problems                                                              | 293<br>294<br>294<br>294<br>294<br>294<br>294<br>295<br>295                                    |

| 12.3 | Product<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>12.3.12 | S<br>Memory cards<br>Disk drives<br>Pagers<br>Local area networks<br>Modems<br>Cellular telephone<br>Data acquisition<br>Digital multimeter<br>GPS systems<br>Pocket organizer<br>Stand-alone products<br>Full size computers | <b>295</b><br>295<br>296<br>296<br>296<br>296<br>296<br>296<br>296<br>297<br>297<br>297<br>297 |

| 12.4 | Constru                                                                                                                            | ction                                                                                                                                                                                                                         | 297                                                                                            |

|      | 12.4.1<br>12.4.2                                                                                                                   | Size and types<br>Extended types                                                                                                                                                                                              | 298<br>298                                                                                     |

| 12.5 | Hardwai<br>12.5.1                                                                                                                  |                                                                                                                                                                                                                               | <b>298</b><br>299                                                                              |

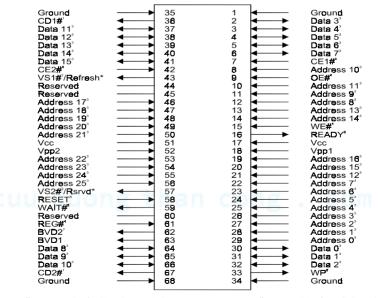

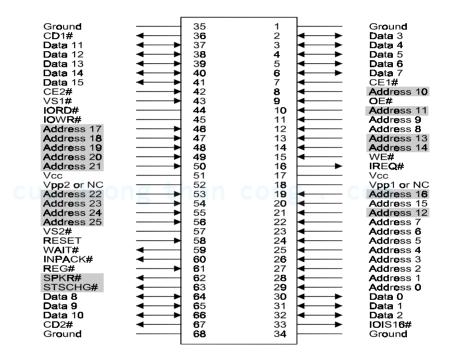

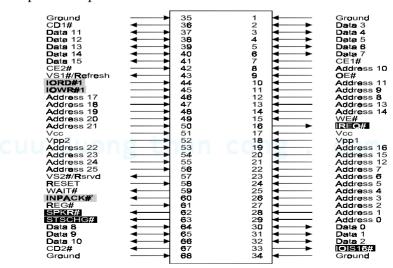

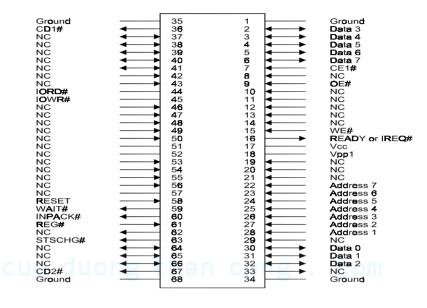

|      | 12.5.2  | Pin assignments                                         | 299 |

|------|---------|---------------------------------------------------------|-----|

|      | 12.5.3  | Memory only cards                                       | 299 |

|      | 12.5.4  | I/O Cards                                               | 300 |

|      | 12.5.5  | I/O with direct memory access                           | 300 |

|      | 12.5.6  | ATA interface (AT attachment)                           | 301 |

|      | 12.5.7  | AIMS interface (auto-indexing mass storage)             | 302 |

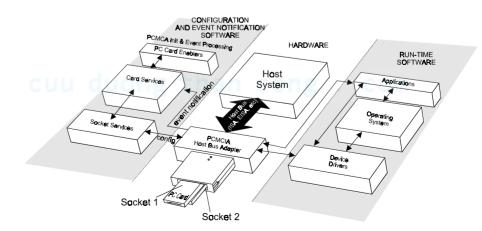

| 12.6 | Softwar | 8                                                       | 302 |

|      | 12.6.1  | PC Card environment                                     | 303 |

| 12.7 | PC Card | l enablers and support software                         | 303 |

| 12.8 | Future  |                                                         | 304 |

|      | 12.8.1  | Magazine list and PCMCIA address                        | 304 |

|      | 12.8.2  | Personal Computer Memory Card International Association | 304 |

|      |         |                                                         |     |

## Appendix A Glossary

305

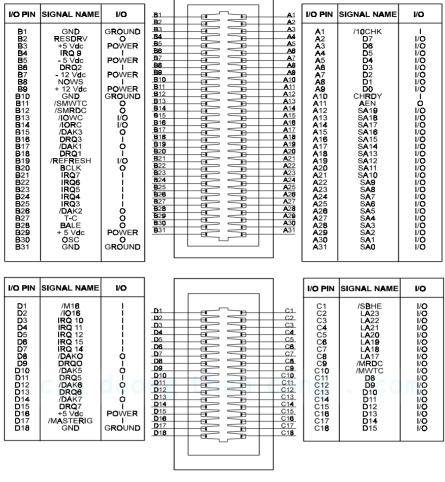

| Арре | endix B IBM PC bus specifications                | 332 |

|------|--------------------------------------------------|-----|

| B.I  | Hardware interrupts                              | 332 |

| B.2  | DMA channels                                     | 333 |

| B.3  | 8237 DMA channels                                | 333 |

|      | Refresh (AT) 08F                                 | 334 |

| B.4  | 8259 interrupt controller                        | 334 |

| B.5  | 8253 / 8254 counter/timer                        | 336 |

| B.6  | Bus signal information                           | 344 |

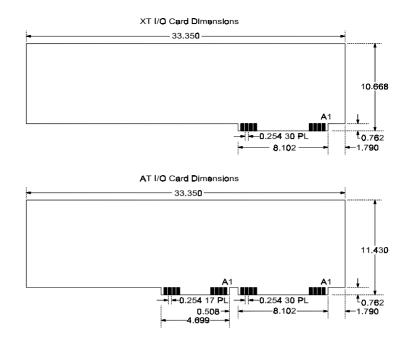

| B.7  | Card dimensions                                  | 346 |

| B.8  | Centronics interface standard                    | 347 |

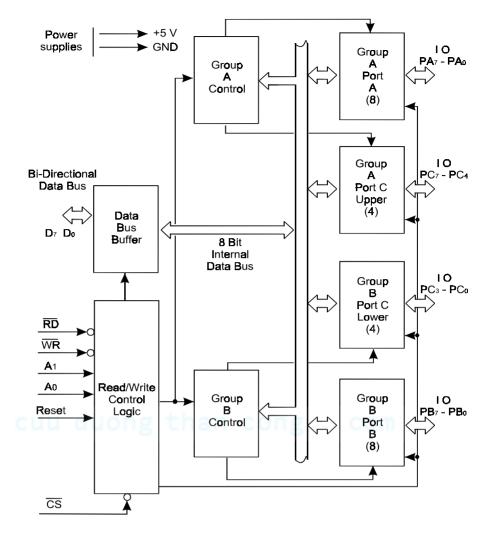

| Арре | endix C Review of the Intel 8255 PPI chip        | 349 |

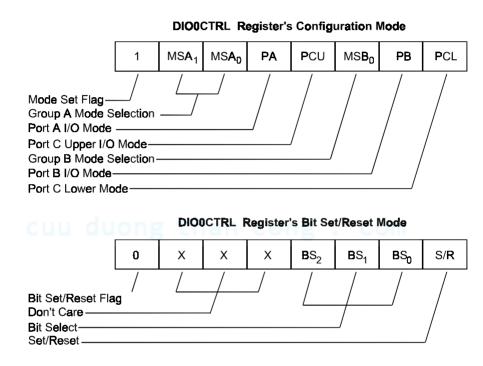

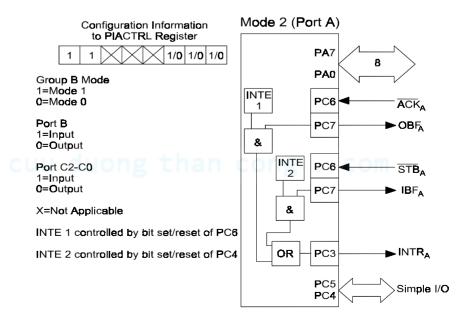

| C.1  | DIO0CTRL – control register of the 8255          | 351 |

| C.2  | DIOA – port A of the 8255 (offset 0, read/write) | 352 |

| C.3  | DIOB – port B of the 8255 (offset 1, read/write) | 353 |

| C.4  | DIOC – port C of the 8255 (offset 2, read/write) | 353 |

| C.5  | Mode 0: simple I/O                               | 355 |

| C.6  | Mode 0 programming                               | 355 |

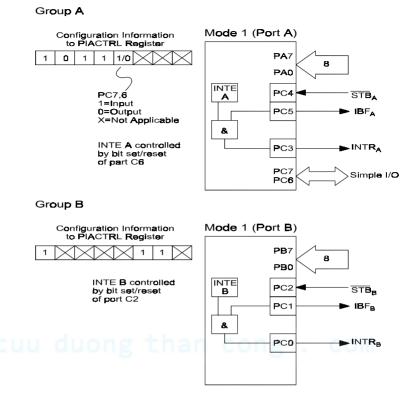

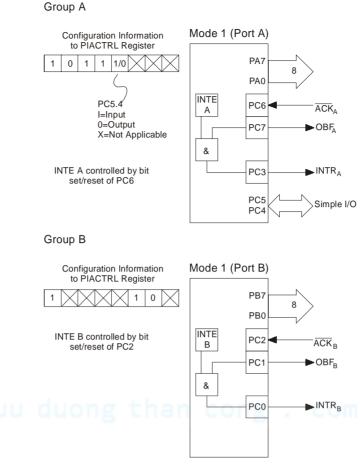

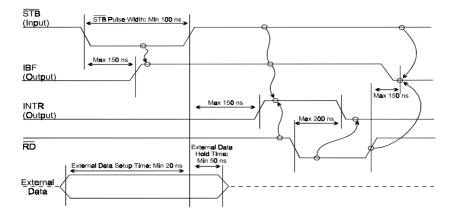

| C.7  | Mode 1: strobed I/O                              | 355 |

| C.8  | Mode 1 programming                               | 356 |

| C.9  | Mode 2: strobed bi-directional bus I/O           | 358 |

| C.10 | Mode 2 programming                               | 359 |

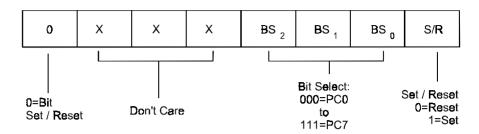

| C.11 | Single-bit set/reset                             | 361 |

| C.12 | Mixed mode programming                           | 361 |

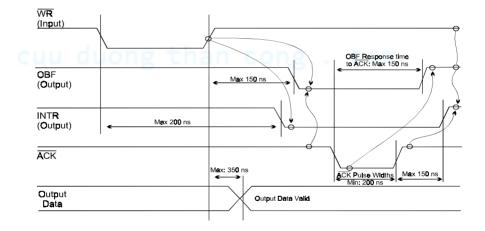

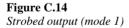

| C.13                                                      | 8255-2 mode 1 and 2 timing diagrams                                                                                                                                                                                                                                                                |                                                                    |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

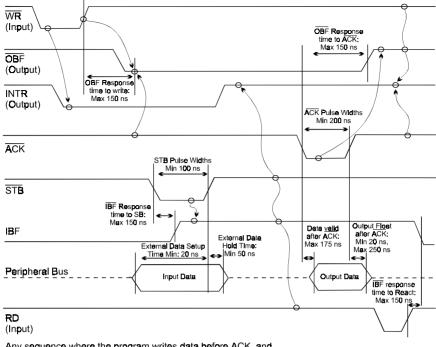

| Appendix D Review of the Intel 8254 timer-counter chip 36 |                                                                                                                                                                                                                                                                                                    |                                                                    |

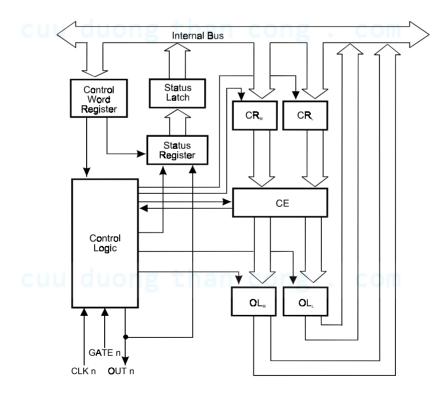

| D.1                                                       | <b>8254 architecture</b><br>Count register (CR)<br>Counting element (CE)<br>Output latch (OL)                                                                                                                                                                                                      | <b>364</b><br>366<br>366<br>366                                    |

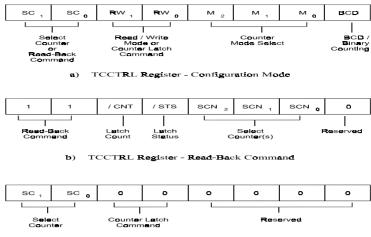

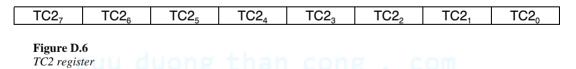

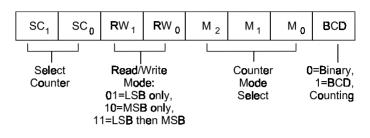

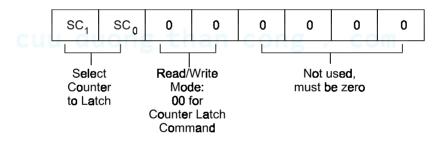

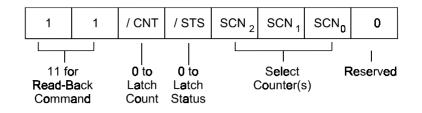

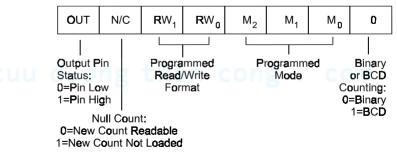

| D.2                                                       | 8254 registers<br>TCCTRL timer/counter control register (offset 3, write only)<br>Configuration mode<br>Read-back command<br>Counter latch command<br>TCO - timer/counter 0 (offset 0, read/write)<br>TC1 - timer/counter 1 (offset 1, read/write)<br>TC2 - timer/counter 2 (offset 2, read/write) | <b>366</b><br>366<br>367<br>368<br>368<br>369<br>369<br>369<br>369 |

| D.3                                                       | <b>Programming a counter</b><br>Data transfer format<br>Clock pulse input<br>Gate input                                                                                                                                                                                                            | <b>369</b><br>370<br>370<br>370                                    |

| D.4                                                       | Read operations<br>Simple read operation<br>Counter latch command<br>Read-back command<br>Multiple counter latch<br>Counter status information<br>Latching both status and current count                                                                                                           | <b>370</b><br>371<br>371<br>371<br>372<br>372<br>373               |

| D.5                                                       | Counter mode definitions<br>Mode 0: interrupt on terminal count<br>Mode 1: hardware re-triggerable one-shot<br>Mode 2: rate generator<br>Mode 3: square wave generator<br>Mode 4: software-triggered strobe<br>Mode 5: hardware-triggered strobe                                                   | <b>373</b><br>373<br>374<br>374<br>374<br>375<br>375               |

| D.6                                                       | Interrupt handling                                                                                                                                                                                                                                                                                 | 376                                                                |

| Арре                                                      | endix E Thermocouple tables                                                                                                                                                                                                                                                                        | 377                                                                |

|                                                           | Type B thermocouple                                                                                                                                                                                                                                                                                | 377                                                                |

| Type B thermocouple<br>Type BP thermocouple<br>Type BN thermocouple<br>Type E thermocouple<br>Type J thermocouples<br>Type JP thermocouples<br>Type JN thermocouples<br>Type K thermocouple<br>Type KP thermocouple | 377<br>378<br>378<br>379<br>380<br>380<br>381<br>381<br>381<br>382<br>383 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Type R thermocouple  | 384 |

|----------------------|-----|

| Type S thermocouple  | 385 |

| Type T thermocouple  | 386 |

| Type TP thermocouple | 387 |

| Type TN thermocouple | 388 |

| Appendix F Number systems38 |                                  |                                                                                      |                          |  |

|-----------------------------|----------------------------------|--------------------------------------------------------------------------------------|--------------------------|--|

| F.1                         | Introduction                     |                                                                                      |                          |  |

| F.2                         | A generalized number system      |                                                                                      |                          |  |

| F.3                         | Binary<br>F.3.1                  | numbers<br>Conversion between decimal and binary numbers                             | <b>390</b><br>391        |  |

| F.4                         | Hexade<br>F.4.1                  | ecimal numbers<br>Conversion between binary and hexadecimal                          | <b>392</b><br>393        |  |

| F.5                         | Octal                            |                                                                                      | 393                      |  |

| F.6                         | Binary coded decimal             |                                                                                      | 394                      |  |

| F.7                         | Binary coded octal systems       |                                                                                      | 394                      |  |

| F.8                         | <b>Interna</b><br>F.8.1<br>F.8.2 | Il representation of information<br>Numeric data<br>Alphanumeric data representation | <b>395</b><br>395<br>396 |  |

| F.9                         | Binary                           | arithmetic                                                                           | 396                      |  |

## Appendix G GPIB (IEEE-488) mnemonics & their definitions 398

| Index | 403 |

|-------|-----|

| Index | 403 |

## cuu duong than cong . com

## Introduction

In 1981, when IBM released its first personal computer or PC (as it became widely known) its open system design encouraged the development of a wide range of compatible add-on products by independent third party developers. In addition, the open system design has encouraged the proliferation of IBM compatible PCs in the market place, resulting in a rapid increase in the speed and power of the PC, as competitors vie for a market edge.

Accompanied by a significant drop in cost and a rapid expansion in software, which utilizes the increased power of the processor, the PC is now the most widely used platform for digital signal processing, image processing, data acquisition, and industrial control and communication applications. In many applications, indeed for data acquisition and process control, the PCs power and flexibility allow it to be configured in a number of ways, each with its own distinct advantages. The key to the effective use of the PC is the careful matching of the specific requirements of a particular data acquisition application to the appropriate hardware and software available.

This chapter reviews the fundamental concepts of data acquisition and control systems and the various system configurations, which make use of the PC.

#### 1.1 Definition of data acquisition and control

Data acquisition is the process by which physical phenomena from the real world are transformed into electrical signals that are measured and converted into a digital format for processing, analysis, and storage by a computer.

In a large majority of applications, the data acquisition (DAQ) system is designed not only to acquire data, but to act on it as well. In defining DAQ systems, it is therefore useful to extend this definition to include the control aspects of the total system. Control is the process by which digital control signals from the system hardware are convened to a signal format for use by control devices such as actuators and relays. These devices then control a system or process. Where a system is referred to as a data acquisition system or DAQ system, it is possible that it includes control functions as well.

#### 1.2 Fundamentals of data acquisition

A data acquisition and control system, built around the power and flexibility of the PC, may consist of a wide variety of diverse hardware building blocks from different equipment manufacturers. It is the task of the system integrator to bring together these individual components into a complete working system.

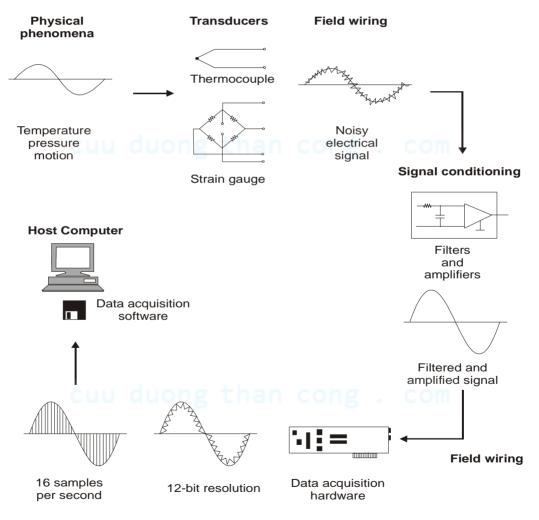

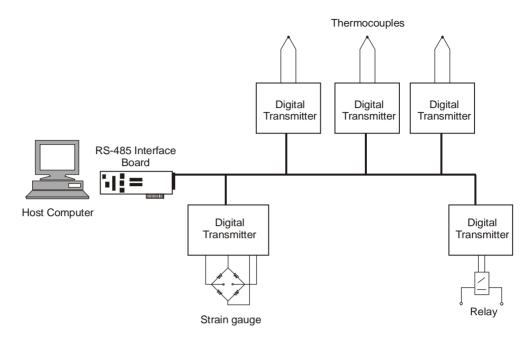

The basic elements of a data acquisition system, as shown in the functional diagram of Figure 1.1, are as follows:

- Sensors and transducers

- Field wiring

- Signal conditioning

- Data acquisition hardware

- PC (operating system)

- Data acquisition software

Figure 1.1

Functional diagram of a PC-based data acquisition system

Each element of the total system is important for the accurate measurement and collection of data from the process or physical phenomena being monitored, and is discussed in the following sections.

#### 1.2.1 Transducers and sensors

Transducers and sensors provide the actual interface between the real world and the data acquisition system by converting physical phenomena into electrical signals that the signal conditioning and/or data acquisition hardware can accept.

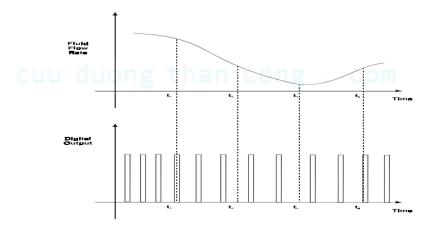

Transducers available can perform almost any physical measurement and provide a corresponding electrical output. For example, thermocouples, resistive temperature detectors (RTDs), thermistors, and IC sensors convert temperature into an analog signal, while flow meters produce digital pulse trains whose frequency depends on the speed of flow.

Strain gauges and pressure transducers measure force and pressure respectively, while other types of transducers are available to measure linear and angular displacement, velocity and acceleration, light, chemical properties (e.g. CO concentration, pH), voltages, currents, resistances or pulses. In each case, the electrical signals produced are proportional to the physical quantity being measured according to some defined relationship.

#### 1.2.2 Field wiring and communications cabling

Field wiring represents the physical connection from the transducers and sensors to the signal conditioning hardware and/or data acquisition hardware. When the signal conditioning and/or data acquisition hardware is remotely located from the PC, then the field wiring provides the physical link between these hardware elements and the host computer. If this physical link is an RS-232 or RS-485 communications interface, then this component of the field wiring is often referred to as communications cabling.

Since field wiring and communications cabling often physically represents the largest component of the total system, it is most susceptible to the effects of external noise, especially in harsh industrial environments. The correct earthing and shielding of field wires and communications cabling is of paramount importance in reducing the effects of noise. This passive component of the data acquisition and control system is often overlooked as an important integral component, resulting in an otherwise reliable system becoming inaccurate or unreliable due to incorrect wiring techniques.

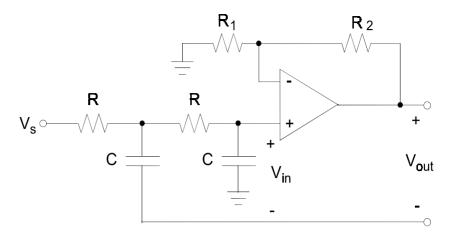

#### 1.2.3 Signal conditioning

Electrical signals generated by transducers often need to be converted to a form acceptable to the data acquisition hardware, particularly the A/D converter which converts the signal data to the required digital format. In addition, many transducers require some form of excitation or bridge completion for proper and accurate operation.

The principal tasks performed by signal conditioning are:

- Filtering

- Amplification

- Linearization

- Isolation

- Excitation

#### Filtering

In noisy environments, it is very difficult for very small signals received from sensors such as thermocouples and strain gauges (in the order of mV), to survive without the sensor data being compromised. Where the noise is of the same or greater order of magnitude than the required signal, the noise must first be filtered out. Signal conditioning equipment often contains low pass filters designed to eliminate high frequency noise that can lead to inaccurate data.

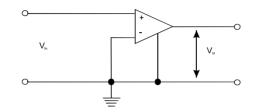

#### Amplification

Having filtered the required input signal, it must be amplified to increase the resolution. The maximum resolution is obtained by amplifying the input signal so that the maximum voltage swing of the input signal equals the input range of the analog-to-digital converter (ADC), contained within the data acquisition hardware.

Placing the amplifier as close to the sensor as physically possible reduces the effects of noise on the signal lines between the transducer and the data acquisition hardware.

#### Linearization

Many transducers, such as thermocouples, display a non-linear relationship to the physical quantity they are required to measure. The method of linearizing these input signals varies between signal conditioning products. For example, in the case of thermocouples, some products match the signal conditioning hardware to the type of thermocouple, providing hardware to amplify and linearize the signal at the same time.

A cheaper, easier, and more flexible method is provided by signal conditioning products that perform the linearization of the input signal using software.

#### Isolation

Signal conditioning equipment can also be used to provide isolation of transducer signals from the computer where there is a possibility that high voltage transients may occur within the system being monitored, either due to electrostatic discharge or electrical failure. Isolation protects expensive computer equipment from damage and computer operators from injury. In addition, where common-mode voltage levels are high or there is a need for extremely low common mode leakage current, as for medical applications, isolation allows measurements to be accurately and safely obtained.

#### Excitation

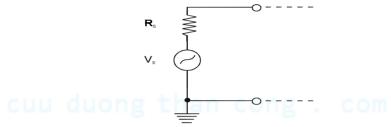

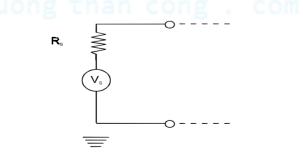

Signal conditioning products also provide excitation for some transducers. For example: strain gauges, thermistors and RTDs, require external voltage or current excitation signals.

#### 1.2.4 Data acquisition hardware

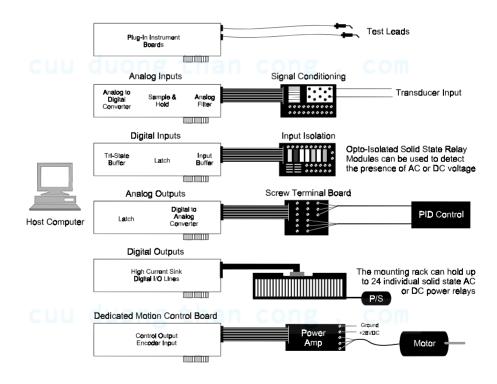

Data acquisition and control (DAQ) hardware can be defined as that component of a complete data acquisition and control system, which performs any of the following functions:

- The input, processing and conversion to digital format, using ADCs, of analog signal data measured from a system or process the data is then transferred to a computer for display, storage and analysis

- The input of digital signals, which contain information from a system or process

- The processing, conversion to analog format, using DACs, of digital signals from the computer the analog control signals are used for controlling a system or process

- The output of digital control signals

Data acquisition hardware is available in many forms from many different manufacturers. Plug-in expansion bus boards, which are plugged directly into the computer's expansion bus, are a commonly utilized item of DAQ hardware. Other forms of DAQ hardware are intelligent stand-alone loggers and controllers, which can be monitored, controlled and configured from the computer via an RS-232 interface, and yet can be left to operate independently of the computer.

Another commonly used item of DAQ hardware, especially in R&D and test environments, is the remote stand-alone instrument that can be configured and controlled by the computer, via the IEEE-488 communication interface. Several of the most common DAQ system configurations are discussed in the section **Data acquisition and control system configuration p. 6**

#### 1.2.5 Data acquisition software

Data acquisition hardware does not work without software, because it is the software running on the computer that transforms the system into a complete data acquisition, analysis, display, and control system.

Application software runs on the computer under an operating system that may be single-tasking (like DOS) or multitasking (like Windows, Unix, OS2), allowing more than one application to run simultaneously.

The application software can be a full screen interactive panel, a dedicated input/output control program, a data logger, a communications handler, or a combination of all of these.

There are three options available, with regard to the software required, to program any system hardware:

- Program the registers of the data acquisition hardware directly

- Utilize low-level driver software, usually provided with the hardware, to develop a software application for the specific tasks required

- Utilize off-the-shelf application software this can be application software, provided with the hardware itself, which performs all the tasks required for a particular application; alternatively, third party packages such as LabVIEW and Labtech Notebook provide a graphical interface for programming the tasks required of a particular item of hardware, as well as providing tools to analyze and display the data acquired

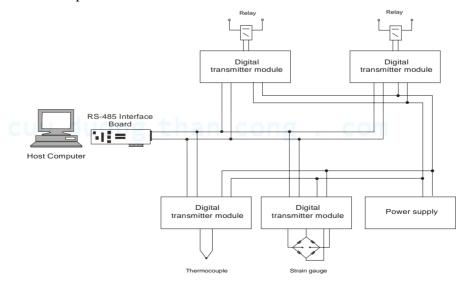

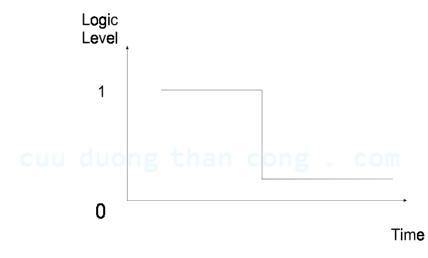

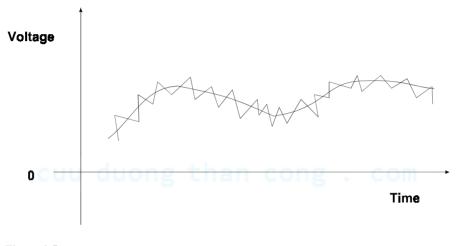

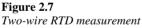

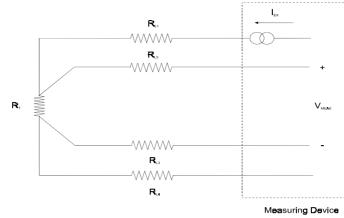

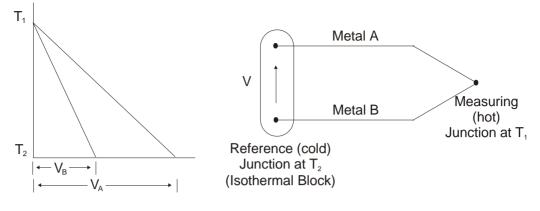

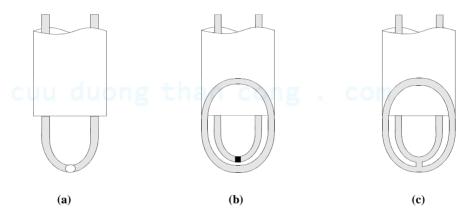

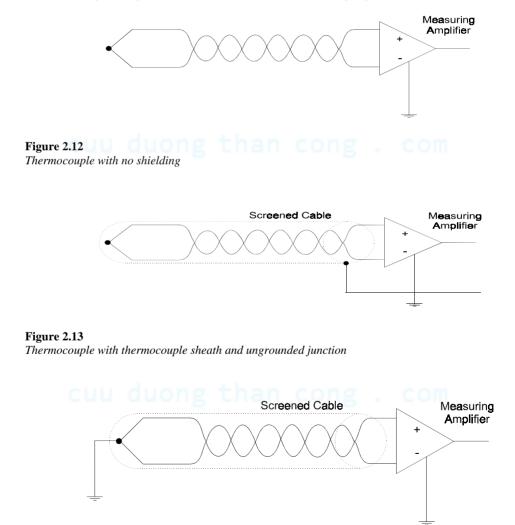

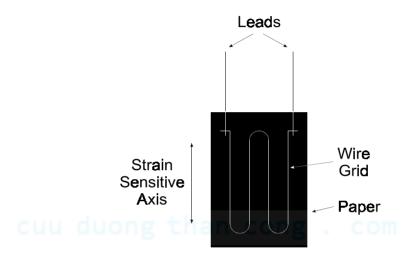

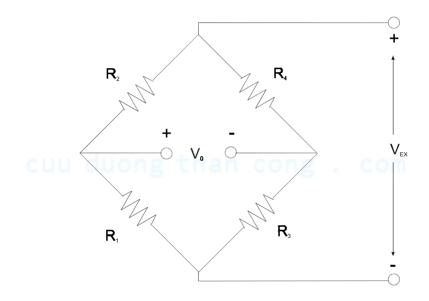

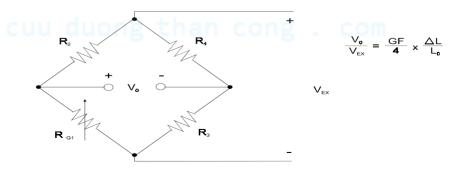

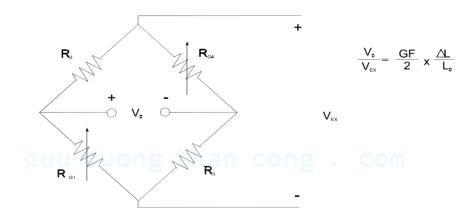

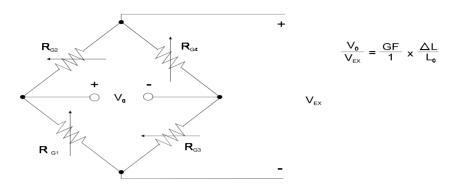

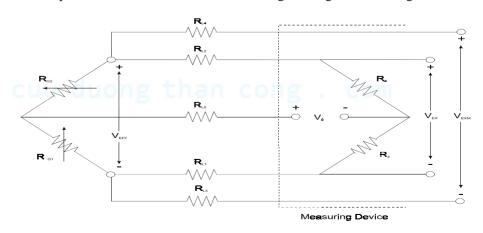

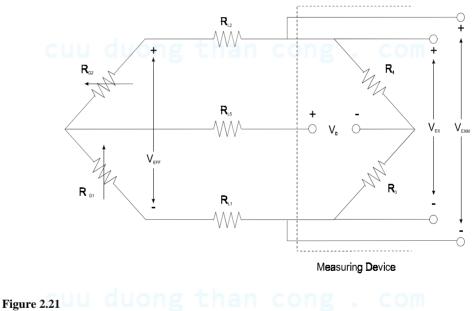

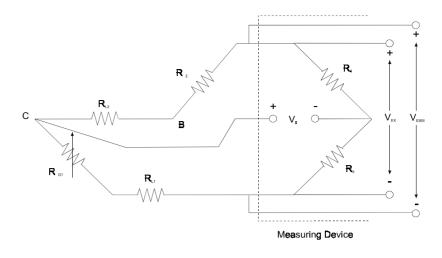

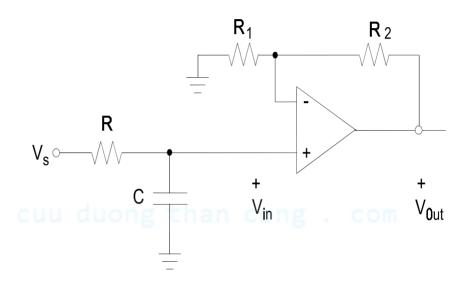

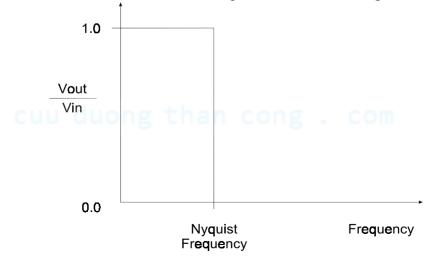

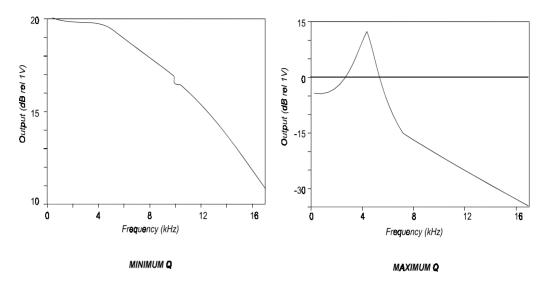

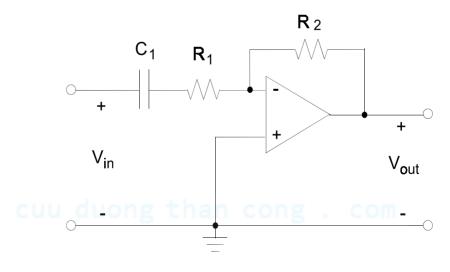

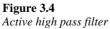

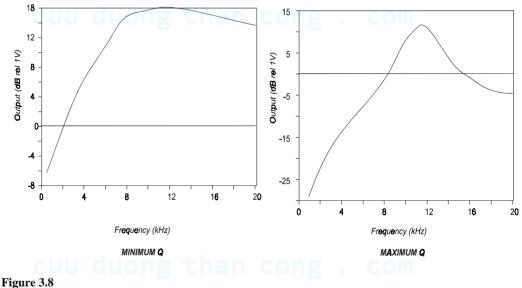

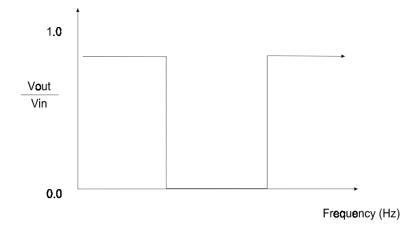

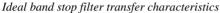

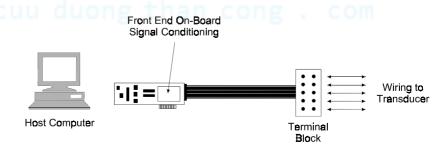

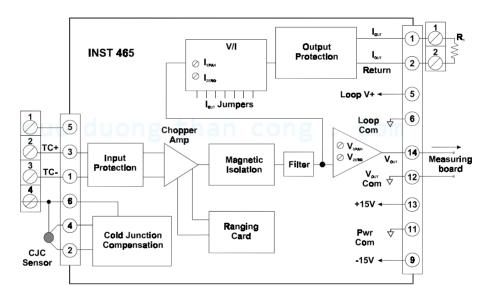

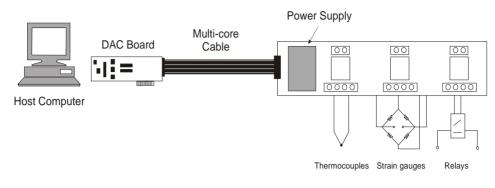

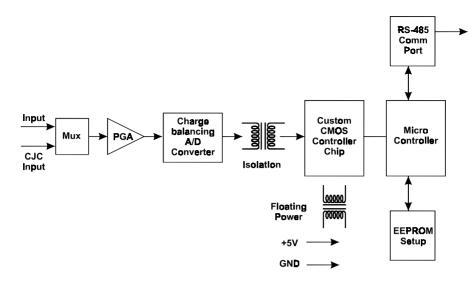

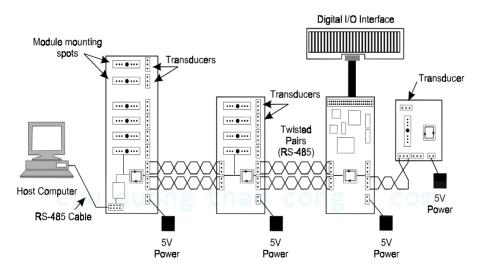

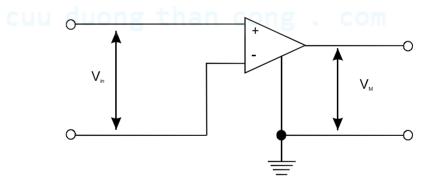

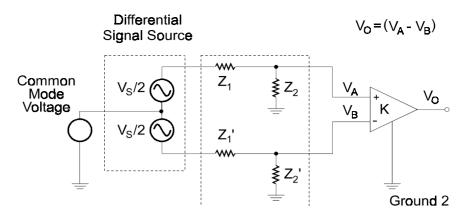

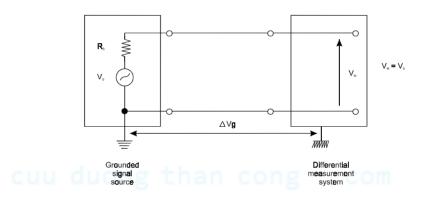

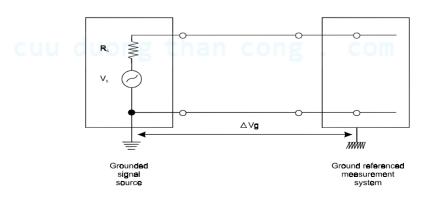

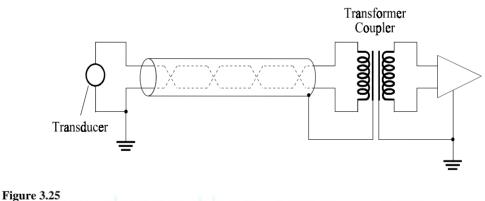

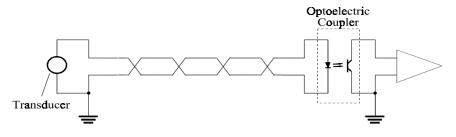

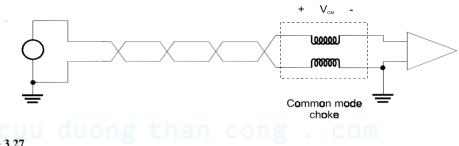

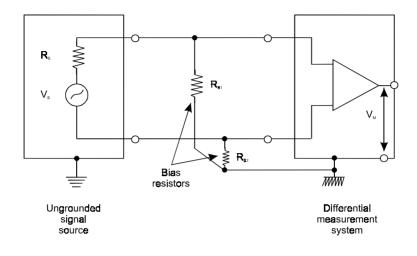

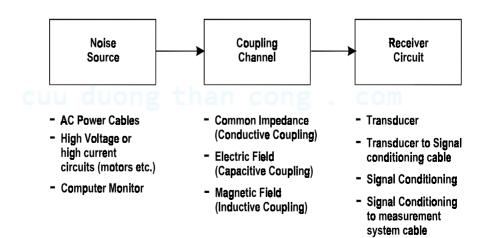

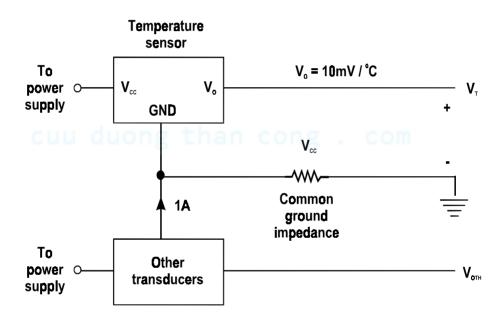

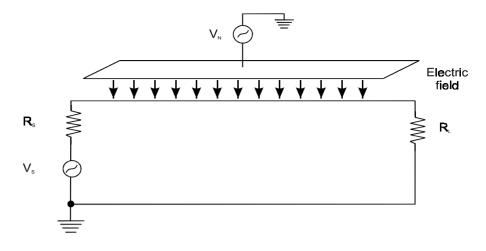

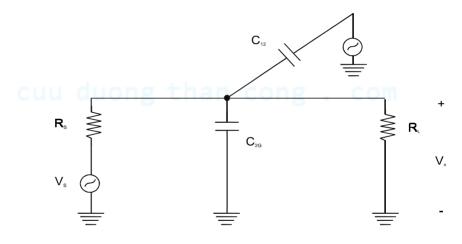

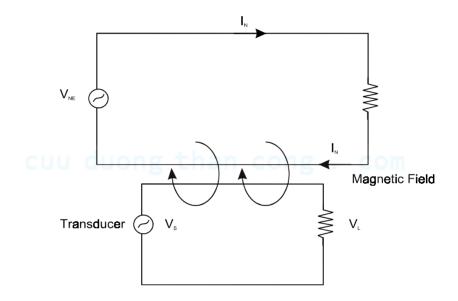

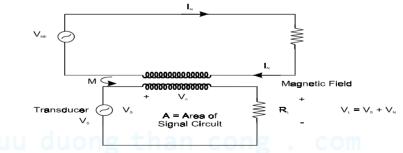

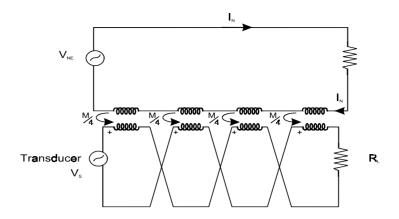

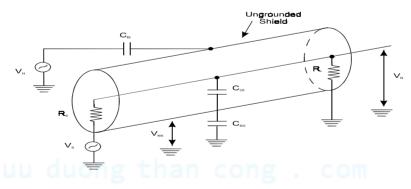

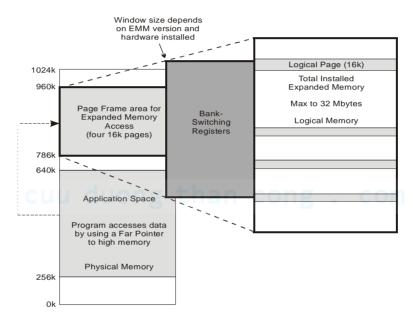

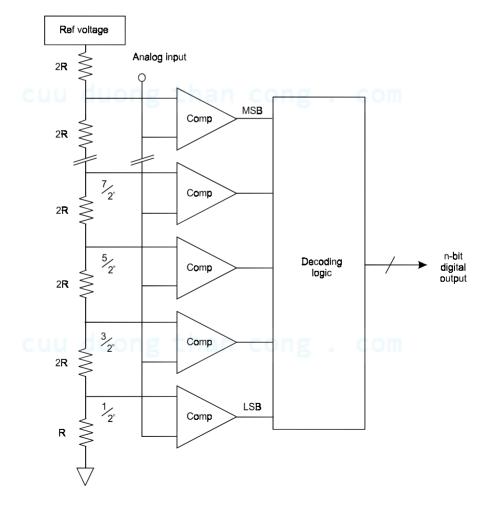

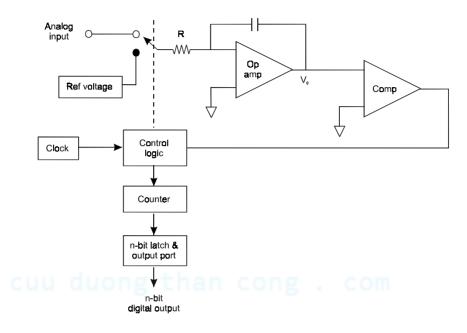

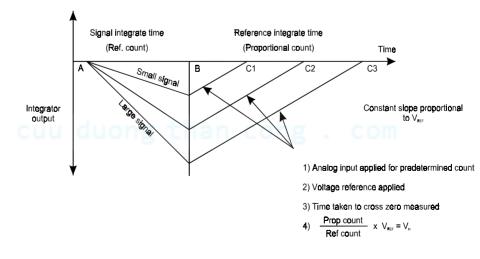

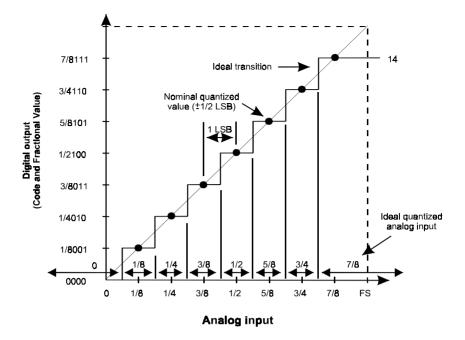

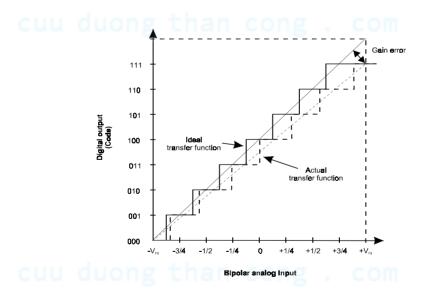

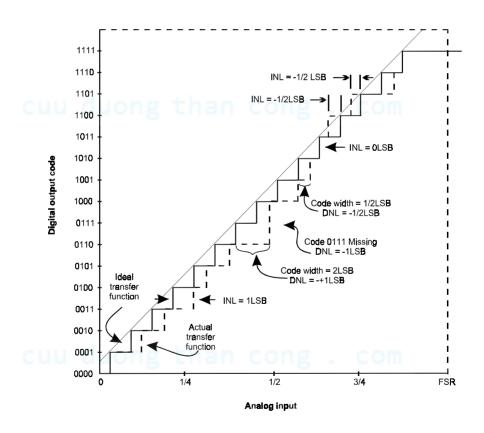

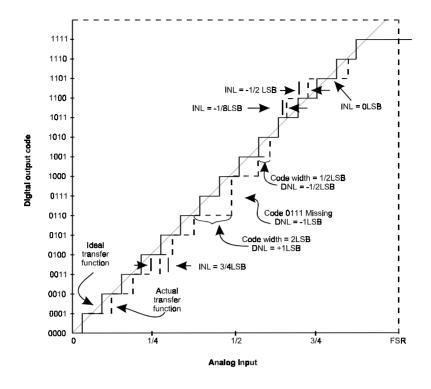

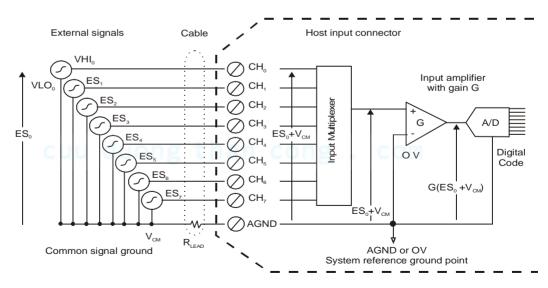

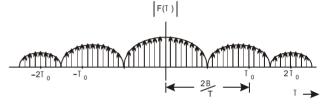

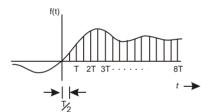

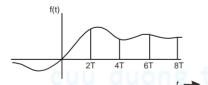

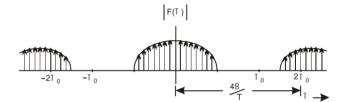

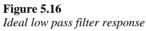

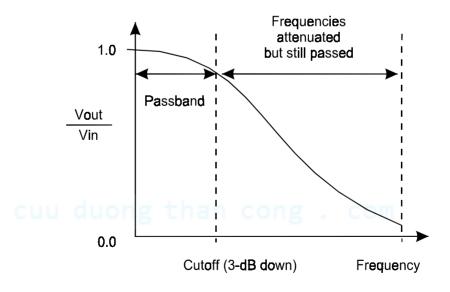

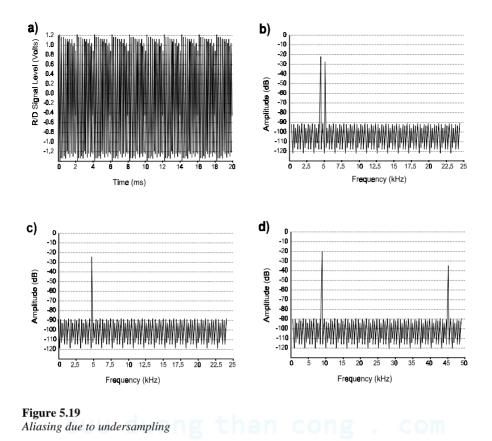

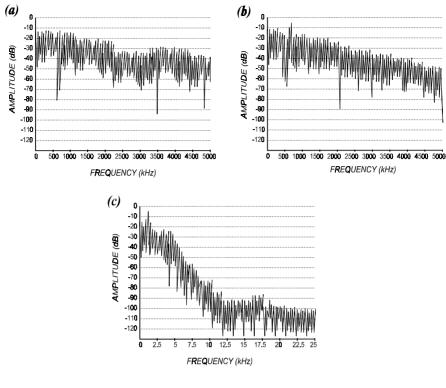

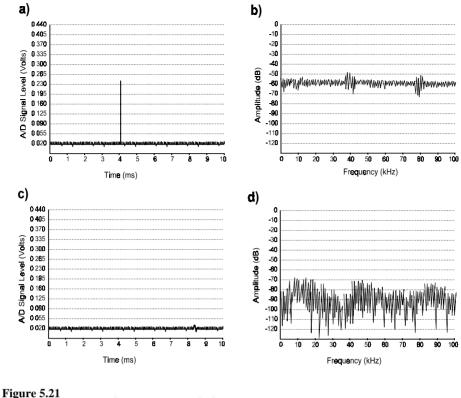

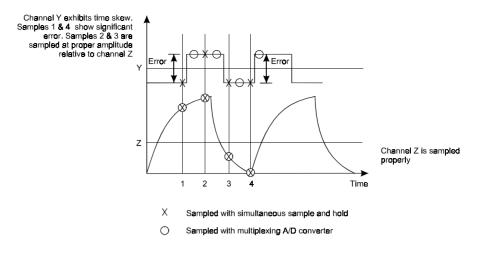

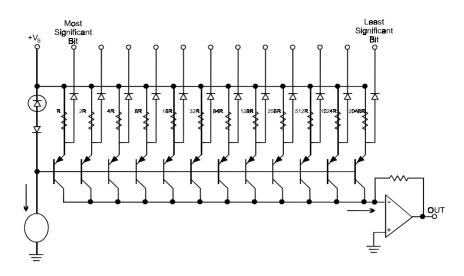

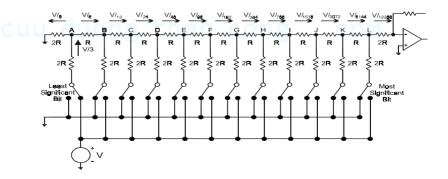

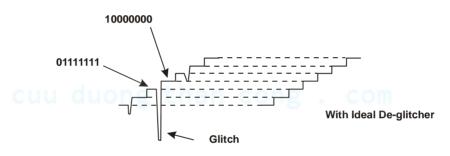

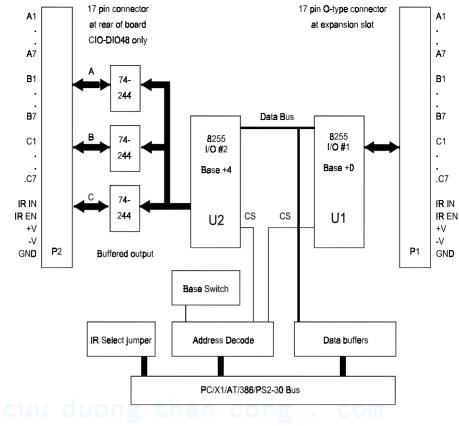

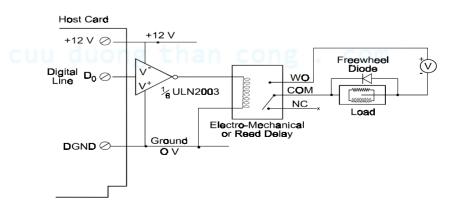

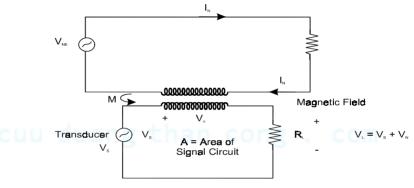

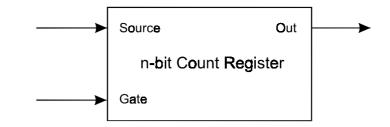

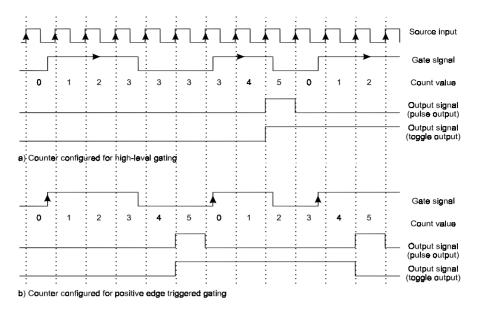

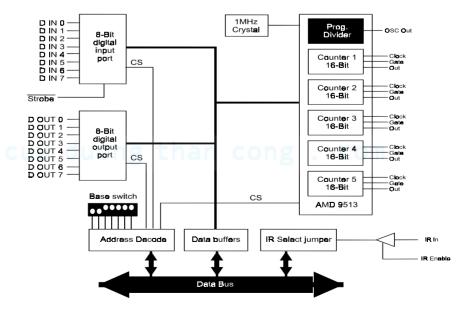

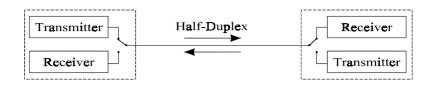

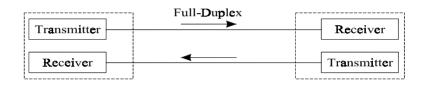

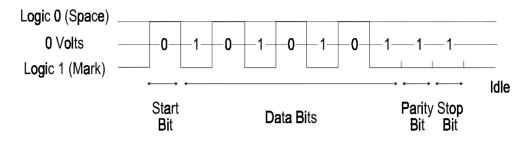

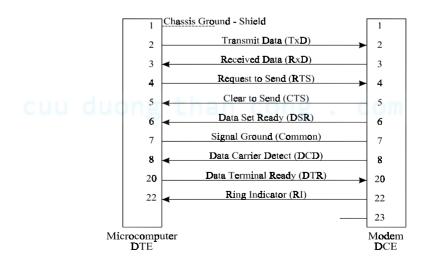

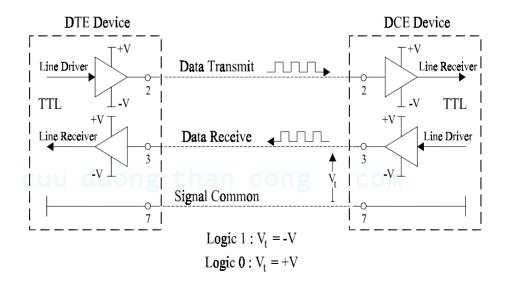

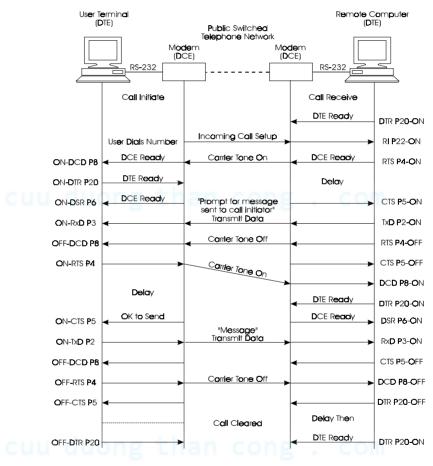

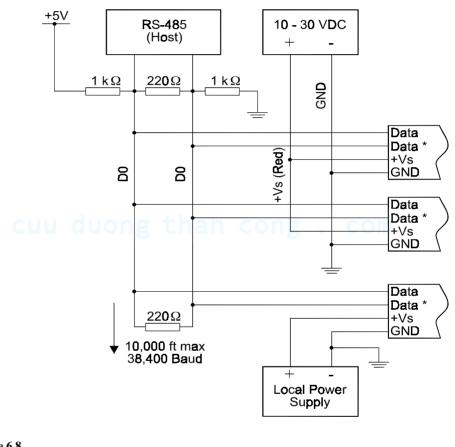

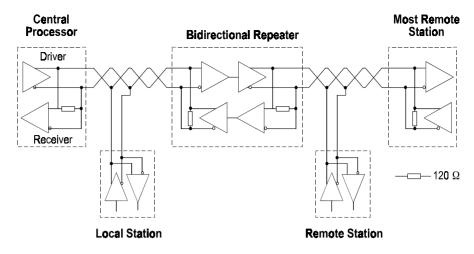

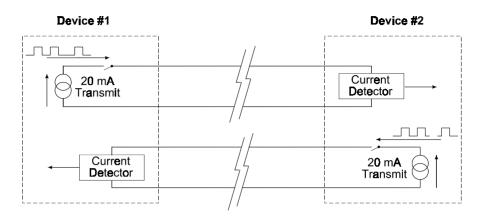

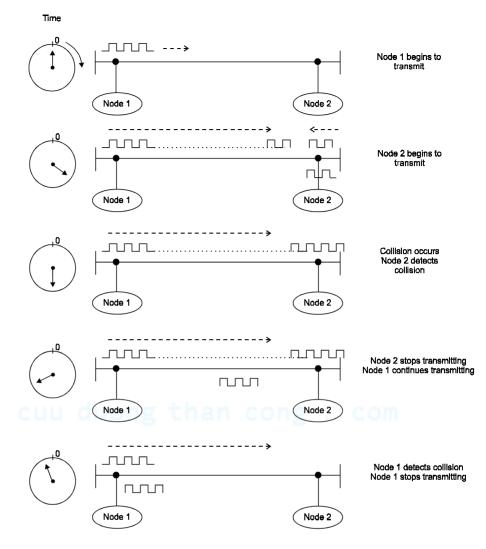

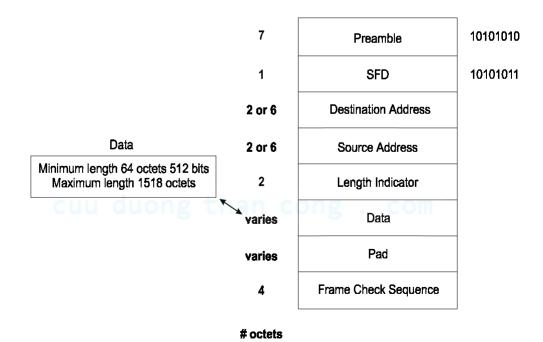

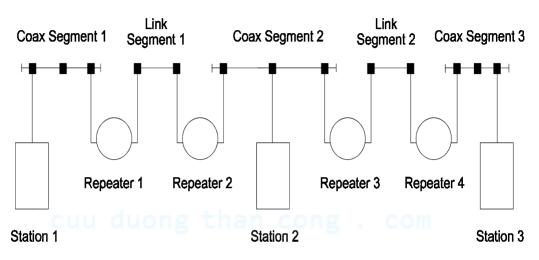

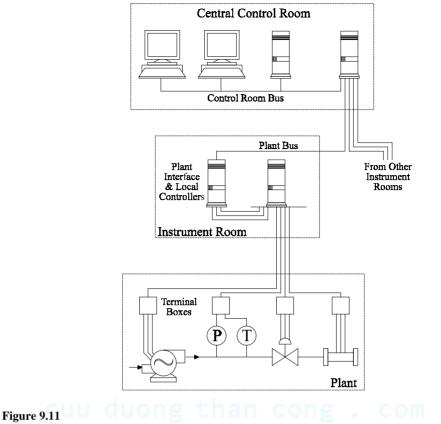

#### 1.2.6 Host computer